stm32F103寄存器

313029282726252423222120191817

151413121110987654321

DBP PVDE CSBF CWUF PDDS

313029282726252423222120191817

151413121110987654321

EWUP PVDO SBF

151413121110987654321151413121110987654321

注:当WKUP 引脚已经是高电平时,在(通过设置EWUP 位)使能WKUP 引脚时,会检测到一个额外事件

BKP ——DRx (x=1...10)(备份数据寄存器)

15-0位:备份数据由用户来写数据。注:BKP ——DRx 寄存器不会被系统复位,电源复位,待机唤醒所复位

它可以由备份域复位来复位或(如果入侵检测引脚TAMPER 功能被开启时)由浸入引脚事件复位

BKP_RTCCR (RTC 时钟校准寄存器)

注:复位时清除这一位

2位:PVDO-PVD 输出(当PVD 被PVDE 位使能后该位才有效)定义:0(VDD/VDDA 高于PLS[2-0]选定的PVD 阀值),1(VDD/VDDA 低于PLS[2-0]选定的PVD 阀值) 注:在待机模式下PVD 被停止,因此,待机模式后或复位后,直到设置PVDE 位之前,该位为0

1位:SBF 待机标志位(该位由硬件设置,并只能由POR/PDR (上电/掉电复位)或设置电源控制寄存器(PWR_CR )的CSBUF 位清除)定义:0(不在待机)1(已待机)0位:WUF 唤醒标志(该位由硬件设置,并只能由POR/PDR (上电/掉电复位)或设置电源控制寄存器(PWR_CR )的CWUF 位清除)

定义:0(没有唤醒事件),1(在WKUP 引脚上发生唤醒事件或出现RTC 脑中事件)

3位:CSBF 清除待机位(始终输出为0)定义:0(无功效),1(清除SBF 待机位(写)

2位:CWUF 清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF 唤醒位(写)

1位:PDDS 掉电深睡眠(与LPDS 位协同操作)定义:0(当CPU 进入深睡眠时进入停机模式,调压器状态由LPDS 位控制),1(CPU 进入深睡眠时进入待机模式)8位:EWUP 使能WKUP 引脚。定义:0(WKUP 为通用IO ),1(用于待机唤醒模式,WKUP 引脚被强置为输入下拉的配置(WKUP 引脚上的上升沿将系统从待机模式唤醒)0位:LPDS 深睡眠下的低功耗(PDDS=0时,与PDDS 位协同操作)定义:0(在待机模式下电压调压器开启),1(在待机模式下电压调压器处于低功耗模式)

PWR_CSR (电源控制/状态寄存器)

保留

保留保留7-5位:PVD 电源电压检测器的电压阀值。定义:000(2.2v ),001(2.3v ),010(2.4v ),011(2.5v ),100(2.6v ),101(2.7v ),110(2.8v ),111(2.98位:DBP 取消后备区域写保护。复位值为0。定义:0为禁止写入,1为允许写入。注:如果rtc 时钟是HSE/128,必须保持为1

4位:PVDE 电源电压检测器(PVD )使能。定义:0(禁止PVD ),1(开启PVD )

PWR_CR (电源控制寄存器)

保留

保留PLS[2:0]PWR 电源相关寄存器

学习STM32,官方提供一个库,但如果刚入手的话,肯定连功能都不太清楚,所以用不太习惯

觉得还是操作寄存器来的直接,所以就整理了STM32的大部分寄存器共大家参考。版权归ST 公司我只是把数据手册中的寄存器整理了一下方便大家看。如果有什么不对的,请通知我,也好修改联系方式:qq 526083029 小树

基本上都是103的,其中107的RCC ,USB ,和以太网等一些不太重要的没有,但大部分都有。

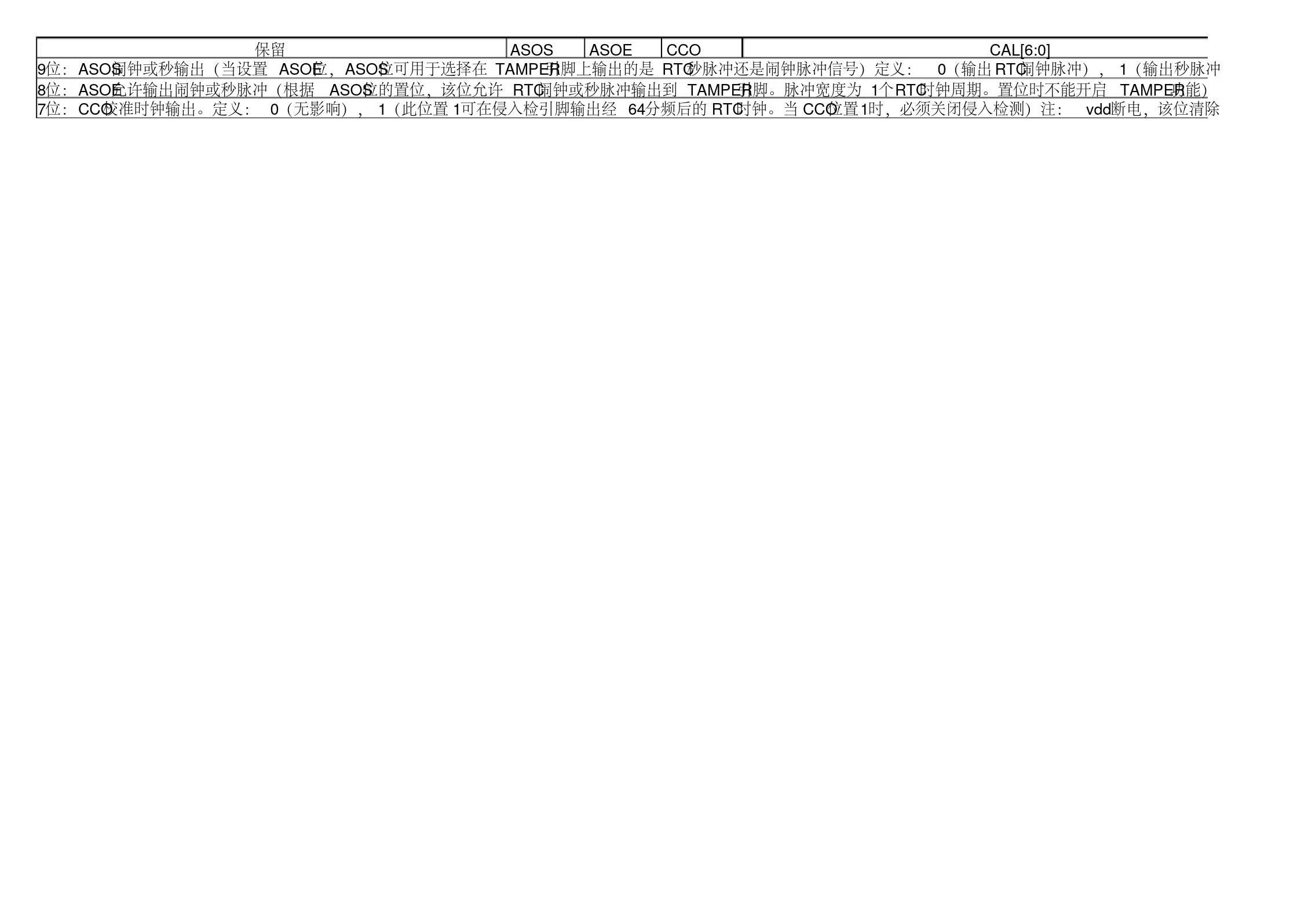

保留CAL[6:0]

ASOS ASOE CCO

9位:ASOS闹钟或秒输出(当设置ASOE位,ASOS位可用于选择在TAMPER引脚上输出的是RTC秒脉冲还是闹钟脉冲信号)定义:0(输出RTC闹钟脉冲),1(输出秒脉冲8位:ASOE允许输出闹钟或秒脉冲(根据ASOS位的置位,该位允许RTC闹钟或秒脉冲输出到TAMPER引脚。脉冲宽度为1个RTC时钟周期。置位时不能开启TAMPER功能)7位:CCO校准时钟输出。定义:0(无影响),1(此位置1可在侵入检引脚输出经64分频后的RTC时钟。当CCO位置1时,必须关闭侵入检测)注:vdd断电,该位清除

151413121110987654321

TPAL

151413121110987654321

TIF TEF TPIE CTI

1位:CTI 清除侵入检测中断(只能写入,读出值为0)定义:0(无效)1(清除侵入检测中断和TIF 侵入检测中断标志)

9位:TIF 侵入中断标志(当检测有侵入事件且TPIE 为1时,此为硬件置1,通过向CTI 位写1来清除标志位(同时也清除中断)。如果TPIE 被清除,此位也会被清除。 注:1、侵入检测无法将系统内核从低功耗模式唤醒,2、仅当系统复位或由待机模式唤醒后才复位该位

定义:0(无侵入),1(检测到侵入)注:仅当系统复位或由待机模式唤醒后才复位该位

8位:TEF 侵入事件标志(当检测到侵入事件时此位由硬件置1。通过向CTE 位写1可清除此标志位)定义:0(无侵入事件),1(有侵入事件)

2位:TPIE :允许侵入TAMPER 引脚中断。定义0(禁止侵入检测中断),1(允许(BKP_CR 寄存器TPE 位也必须置1)

注:侵入事件会复位所有的BKP_DRx 寄存器。只要TEF 为1,所有的BKP_DRx 寄存器就一直保持复位状态。当此位被置1时,若对BKP_DRx 写操作,则不会保存。保留保留1位:TPAL 侵入检测TAMPER 引脚有效电平。定义:0(检测TAMPER 脚高电平清除备份数据)1(检测TAMPER 脚低电平清除备份数据)

2位:TPE 启动入侵检测TAMPER 引脚。定义:0(TAMPER 脚为普通IO ),1(开启检测)

注:TPAL 、TPE 同时置为可用,但同时清零则会出问题。所以推荐在TPE 为0时才改变TPAL 位状态。

BKP_CSR(备份控制/状态寄存器)

6-0位:CAL 校准值。表示在每2的20次方个时钟脉冲内将有多少个脉冲被跳过。这可用来对RTC 进行校准,以1000000/(2的20次方比例减慢时钟)可用被减慢0-121

BKP_CR(备份控制寄存器)

保留

31

302928272625242322212019

1817PLLRDY PLLON CSSON HSEBYP HSERDY 1514131211

10987654321保留HSIRDY 313029282726252423222120191817

保留OTGFSPRE PLLXTPRE

151413121110987654321

15-8位:HSICAL[7:0]-内部高速时钟校准。系统启动时,这些位被自动初始化。

7-3位:HSITRIM[4:0]-内部高速时钟调整(软件控制,与HSICAL 叠加,相当于手动微调)

1位:HSIRDY 内部高速时钟就绪标志硬件置1,在HSION 清零后,该位需要6个内部8M 振荡周期清零。定义:0(没有就绪),1(有就绪)

19位:CSSON 时钟安全系统使能(由软件置1或清零)定义:0(时钟监测器关闭),1(如果外部4-16M 振荡器就绪,时钟监测器开启)

18位:HSEBYP 外部高速时钟旁路。定义:0(晶振4-16M ),1(有源晶振25M )。调试模式下由软件控制。只有在4-16M 振荡器关闭情况下,才能写入该位。

17位:HSERDY 外部高速时钟就绪标志(自动)在HSEON 位清零后,需6个外部4-25M 振荡器周期清零。定义:0(4),

16位:HSEON 外部高速时钟使能(软件控制)定义:0(HSE 关闭),1(HSE 开启)。待机或停机模式硬件清零,当用作系统系统时钟时,该位不能清零。

RCC_CR(时钟控制寄存器)0位:HSION 内部高速时钟使能(软件控制)当从待机或停机返回用或外部振荡故障时由硬件置1。若使用内部时钟做系统时钟则不能清零。定义:0(关),1(开)

0位:CTE 清除侵入检测事件(只能写入,读出值为0)定义:0(无效)1(清除TEF 侵入检测事件标志(并复位侵入检测器)

保留保留HSICAL[7:0]

HSITRIM[4:0]25位:PLLRDY-PLL 时钟就绪标志(PLL 锁定后由硬件置1)定义:0(未锁定),1(锁定)

24位:PLLON-PLL 使能(手动)定义:0(PLL 关闭),1(PLL 使能)。进入待机或停机模式时,该位由硬件清零当PLL 用作系统始终时,该位不能被清零。

SW[1:27-24位:MCO 微控制器时钟输出(手动)注:该时钟输出在启动和切换MCO 时钟源时可能会被截断。在系统时钟作为MCO 引脚时,需保证输出不高于50M

ADCPRE[1:0]RCC_CFGR(时钟配置寄存器)

保留MCO[3:0]PLLMUL[3:0]22位:OTGFSPRE 全速USBOTG 预分频(手动)在RCC_APB1ENR 寄存器中使能全速OTG 时钟之前,必须保证该位已经有效,如OTG 时钟被使能则不能清0

定义:0(VCO 时钟除3,但必须配置PLL 输出为72M ),1(VCO 时钟除2,但必须配置PLL 输出为48M )

21-18位:PLLMUL-PLL 倍频系数(手动)注:只有在PLL 关闭的情况下才能被写入,且PLL 的输出频率不能超过72M

定义:000x,10xx,1100(保留),0010(PLL4倍),0011(PLL5倍),0100(PLL6倍),0101(PLL7倍),0110(PLL8倍),0111(PLL9倍),1101(PLL6.5倍)PPRE2[2:0]PPRE1[2:0] 定义:00xx (无输出),0100(系统时钟sysclk 输出),0101(内部8M 输出),0110(外部25M 输出),0111(PLL 时钟2分频输出),1000(PLL2输出) 1001(PLL3时钟2分频输出),1010(XT1外部25M 输出(为以太网),1011(PLL3时钟输出)

HPRE[3:0]SWS[1:0]15/14位:ADCPRE-ADC 预分频(手动)定义:00(PCLK2-2分频),01(PCLK2-4分频),10(PCLK2-6分频),11(PCLK2-8分频)

13-11位:PPRE2[2:0]-APB2预分频(手动)定义:0xx (HCLK 不分频),100(HCLK2分频),101(HCLK4分频),110(HCLK8分频),111(HCLK16分频)

7-4位:HPRE[3:0]-AHB 预分频(手动)定义:0xxx(SYSCLK 不分频),1000(2分频),1001(4分频),1010(8分频),1011(16分频)

1100(64分频),1101(128分频),1110(256分频),1111(512分频).注:AHB 时钟预分频大于1时,必须开预取缓冲器。当使用以太网模块时,频率至少25M 10-8位:PPRE1[2:0]-APB1预分频(手动)定义:0xx (HCLK 不分频),100(HCLK2分频),101(HCLK4分频),110(HCLK8分频),111(HCLK16分频),注小于17位:PLLXTPRE-PREDIV1分频因子低位(软件控制)与RCC_CFGR2的0位为同一位。如果RCC_CFGR2[3:1]为000,则该位控制PREDIV1对输入时钟进行2分频(PLLXPR 或不对输入时钟分频(PLLXPRE=0),只能在关闭PLL 时才写入此位

16位:PLL 输入时钟源(软件控制,且只能在关闭PLL 时才写入此位)定义:0(HIS 时钟2分频做PLL 输入),1(PREDIV1输出做PLL 输入)

注:当改变主PLL 的输入时钟源时,必须在选定了新的时钟源后才能关闭原来的时钟源

3-2位:SWS[1:0]系统时钟切换状态(自动)定义:00(HIS 作为系统时钟),01(HSE 做系统时钟),10(PLL 做系统时钟),11(不可用)RCC 时钟相关寄存器

313029282726252423222120191817

CSSC PLLRDYC HSERDYCHISRDYC LSERDYC

151413121110987654321

PLLRDYIEHSERDYIE HSIRDYIE LSERDYIELSIRDYIE CSSF PLLRDYF HSERDYF HSIRDYF LSERDYF

313029282726252423222120191817

151413121110987654321

ADC3RST USART1RST TIM8RST SPI1RST TIM1RST ADC2RST ADC1RST IOPGRST IOPFRST IOPERST IOPDRST IOPCRST IOPBRST IOPARST 保留

3位:IOPBRST-IOPB 接口复位(手动)定义:0(无作用),1(复位IOPB 接口)

2位:IOPARST-IOPA 接口复位(手动)定义:0(无作用),1(复位IOPA 接口)

9位:ADC1RST-ADC1接口复位(手动)定义:0(无作用),1(复位ADC1接口)

8位:IOPGRST-IOPG 接口复位(手动)定义:0(无作用),1(复位IOPG 接口)

7位:IOPFRST-IOPF 接口复位(手动)定义:0(无作用),1(复位IOPF 接口)

6位:IOPERST-IOPE 接口复位(手动)定义:0(无作用),1(复位IOPE 接口)

5位:IOPDRST-IOPD 接口复位(手动)定义:0(无作用),1(复位IOPD 接口)

4位:IOPCRST-IOPC 接口复位(手动)定义:0(无作用),1(复位IOPC 接口)

15位:ADC3RST-ADC3接口复位(手动)定义:0(无作用),1(复位ADC3接口)

14位:USART1RST-USART1接口复位(手动)定义:0(无作用),1(复位USART1接口)

13位:TIM8RST-TIM8接口复位(手动)定义:0(无作用),1(复位TIM8接口)

12位:SPI1RSTRST-SPI1接口复位(手动)定义:0(无作用),1(复位SPI1接口)

11位:TIM1RST-TIM1接口复位(手动)定义:0(无作用),1(复位TIM1接口)

10位:ADC2RST-ADC2接口复位(手动)定义:0(无作用),1(复位ADC2接口)

保留

4位:PLLRDYF-PLL3就绪中断标志(自动置1,手动PLLRDYC 清除)定义:0(无PLL 上锁产生的时钟就绪中断),1(PLL 上锁导致中断)

3位:HSERDYF-HSE 就绪中断标志(自动置1,手动HSERDYC 清除)0(无中断),1(有中断)

9位:LSERDYIE-LSE 就绪中断使能(手动)定义:0(LSE 就绪中断关闭),1(LSE 就绪中断使能)

8位:LSIRDYIE-LSI 就绪中断使能(手动)定义:0(LSI 就绪中断关闭),1(LSI 就绪中断使能)

7位:CSSF 时钟安全系统中断标志(自动置1,手动CSSC 清除)定义:0(无HSE 时钟失效产生的中断),1(HSE 时钟失效产生中断)

RCC_APB2RSTR (APB2外设复位寄存器)

0位:LSIRDYF-LSI 就绪中断标志(自动置1,手动HSERDYC 清除)0(无中断),1(有中断)

1位:LSERDYF-LSE 就绪中断标志(自动置1,手动HSERDYC 清除)0(无中断),1(有中断)

2位:HSIRDYF-HSI 就绪中断标志(自动置1,手动HSERDYC 清除)0(无中断),1(有中断)

1-0位:SW 系统时钟切换(手动,自动,自动时时钟安全须开启)定义:00(HIS 做系统时钟),01(HSE 做系统时钟),10(PLL 做系统时钟),11(不可用)

12位:PLLRDYIE-PLL 就绪中断使能(手动)定义:0(PLL 就绪中断关闭),1(PLL 就绪中断使能)

10位:HSIRDYIE-HSI 就绪中断使能(手动)定义:0(HSI 就绪中断关闭),1(HSI 就绪中断使能)

11位:HSERDYIE-HSE 就绪中断使能(手动)定义:0(HSE 就绪中断关闭),1(HSE 就绪中断使能)

保留保留保留RCC_CIR(时钟中断寄存器)

保留16位:LSIRDYC 清除HSE 就绪中断(手动)定义:0(无作用),1(清除LSI 就绪中断标志位LSIRDYF )

18位:HSIRDYC 清除HSE 就绪中断(手动)定义:0(无作用),1(清除HSI 就绪中断标志位HSIRDYF )

17位:LSERDYC 清除HSE 就绪中断(手动)定义:0(无作用),1(清除LSE 就绪中断标志位LSERDYF )

23位:CSSC 清除时钟安全系统中断(软件置1)定义:0(无作用),1、清除CSSF 安全系统中断标志

20位:PLLRDYC 清除PLL 就绪中断(手动)定义:0(无作用),1(清除PLL 就绪中断标志位PLLRDYF )

19位:HSERDYC 清除HSE 就绪中断(手动)定义:0(无作用),1(清除HSE 就绪中断标志位HSERDYF )

31302928272625242322

2120191817DACRST PWRRST BKPRST 保留CANRST 保留USBRST I2C2RST

I2C1RST UART5RST UART4RST UART3RST UART2RST 1514131211109876

54321SPI3RST SPI2RST WWDGRST TIM7RST TIM6RST TIM5RST TIM4RST TIM3RST 31302928272625242322

21201918171514131211109876

54321SDIOEN 保留FSMCEN 保留CRCEN

保留FLITFEN 保留SRAMEN DMA2EN 31302928272625242322

2120191817151413121110987654321

保留

2位:TIM4RST-TIM4复位接口(手动)定义:0(无作用),1(复位TIM4接口)

1位:TIM3RST-TIM3复位接口(手动)定义:0(无作用),1(复位TIM3接口)

0位:TIM2RST-TIM2复位接口(手动)定义:0(无作用),1(复位TIM2接口)

RCC_AHBENR (外设时钟使能寄存器)

RCC_APB2ENR (APB2外设时钟使能寄存器)

保留

4位:FLITFEN-FLITF 时钟使能(手动)定义:0(时钟关闭),4(时钟开启)

10位:SDIOEN-SDIO 时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

8位:FSMCEN-FSMC 时钟使能(手动)定义:0(时钟关闭),2(时钟开启)

2位:SRAMEN-SRAM 时钟使能(手动)定义:0(时钟关闭),5(时钟开启)

1位:DMA2EN-DMA2时钟使能(手动)定义:0(时钟关闭),6(时钟开启)

14位:SPI2RST-SPI2复位接口(手动)定义:0(无作用),1(复位SPI2接口)

22位:I2C2RST-I2C2复位接口(手动)定义:0(无作用),1(复位I2C2接口)

21位:I2C1RST-I2C1复位接口(手动)定义:0(无作用),1(复位I2C1接口)

20位:UART5RST-UART5复位接口(手动)定义:0(无作用),1(复位UART5接口)

19位:UART4RST-UART4复位接口(手动)定义:0(无作用),1(复位UART4接口)

0位:DMA1EN-DMA1时钟使能(手动)定义:0(时钟关闭),7(时钟开启)

保留5位:TIM7RST-TIM7复位接口(手动)定义:0(无作用),1(复位TIM7接口)

4位:TIM6RST-TIM6复位接口(手动)定义:0(无作用),1(复位TIM6接口)

3位:TIM5RST-TIM5复位接口(手动)定义:0(无作用),1(复位TIM5接口)

0位:AFIORST 辅助功能IO 复位(手动)定义:0(无作用),1(复位辅助功能)

RCC_APB1RSTR (APB1外设复位寄存器)

18位:UART3RST-UART3复位接口(手动)定义:0(无作用),1(复位UART3接口)

17位:UART2RST-UART2复位接口(手动)定义:0(无作用),1(复位UART2接口)

保留保留保留

29位:DACRST-DAC 复位接口(手动)定义:0(无作用),1(复位DAC 接口)

25位:CANRST-CAN 复位接口(手动)定义:0(无作用),1(复位CAN 接口)

23位:USBRST-USB 复位接口(手动)定义:0(无作用),1(复位USB 接口)

28位:PWRRST 电源复位接口(手动)定义:0(无作用),1(复位PWR 接口)

27位:BKPRST-备份复位接口(手动)定义:0(无作用),1(复位BKP 接口)

6位:CRCEN-CRC 时钟使能(手动)定义:0(时钟关闭),3(时钟开启)

11位:WWDGRST-WWDG 复位接口(手动)定义:0(无作用),1(复位WWDG 接口)

15位:SPI3RST-SPI3复位接口(手动)定义:0(无作用),1(复位SPI3接口)

ADC3EN USART1ENTIM8EN SPI1EN TIM1EN ADC2EN ADC1EN IOPGEN IOPFEN IOPEEN IOPDEN IOPCEN IOPBEN IOPAEN 保留

313029282726252423222120191817

DACEN PWREN BKPEN 保留CANEN 保留USBEN I2C2EN I2C1EN UART5EN UART4EN UART3EN UART2EN

151413121110987654321

SPI3EN SPI2EN WWDGEN TIM7EN TIM6EN TIM5EN TIM4EN TIM3EN 0位:TIM2RST-TIM2时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

4位:TIM6RST-TIM6时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

3位:TIM5RST-TIM5时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

2位:TIM4RST-TIM4时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

1位:TIM3RST-TIM3时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

11位:WWDGRST-WWDG 时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

5位:TIM7RST-TIM7时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

19位:UART4RST-UART4时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

14位:SPI2RST-SPI2时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

18位:UART3RST-UART3时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

17位:UART2RST-UART2时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

15位:SPI3RST-SPI3时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

27位:BKPRST-备份时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

25位:CANRST-CAN 时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

23位:USBRST-USB 时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

22位:I2C2RST-I2C2时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

21位:I2C1RST-I2C1时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

20位:UART5RST-UART5时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

29位:DACRST-DAC 时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

2位:IOPAEN :IOPA 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

0位:AFIOEN :AFIO 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

保留RCC_APB1ENR (APB1外设时钟使能寄存器)

28位:PWRRST 电源时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

6位:IOPEEN :IOPE 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

3位:IOPBEN :IOPB 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

5位:IOPDEN :IOPD 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

4位:IOPCEN :IOPC 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

保留保留14位:USART1EN :USART1接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

13位:TIM8EN :TIM8接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

7位:IOPFEN :IOPF 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

8位:IOPGEN :IOPG 接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

12位:SPI1EN :SPI1接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

11位:TIM1EN :TIM1接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

10位:ADC2EN :ADC2接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

9位:ADC1EN :ADC1接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

15位:ADC3EN :ADC3接口时钟使能(手动)定义:0(时钟关闭),1(时钟开启)

RCC_BDCR(备份时钟控制寄存器)

31

3029282726252423222120191817151413121110987654321

RTCEN LSEBYP LSERDY 313029282726252423222120191817

LPWRRSTF WWDGRSTF IWDGRSTF SFTRSTF PORRSTF PINRSTF 保留RMVF 151413121110987654321

LSIRDY

保留保留RTCSEL[1:0]保留16位:BDRST 备份域软件复位(手动)定义:0(复位未激活),1(复位整个备份域)

15位:RTCEN-RTC 时钟使能(手动)定义:0(RTC 时钟关闭),1(RTC 时钟开启)

2位:LSEBYP 低速时钟振荡器旁路(手动)只有在外部振荡器关闭时,才能写入该位低速振荡器周期才被清零。定义:0(无旁路),1(有旁路)

RCC_CSR(RCC 时钟控制/状态寄存器)

9-8位:RTCSEL[1:0]RTC 时钟源选择(手动)一旦选定,则直到下次后被域被复位前不能改变,可通过设置BDRST 来清除

定义:00(无时钟),01(LSE 为时钟),10(LSI 为时钟),11(HSE 振荡器在128分频后做时钟)

1位:LSERDY 外部低速LSE 就绪(自动)在LSEON 被清零后,该位需要6个低速周期才被清零。定义:0(外部振荡器未就绪),1(外部振荡器就绪)

0位:LSEON 外部低速振荡器使能(软件)定义:0(外部振荡器关闭),1(外部振荡器开启)

保留

保留31位:LWRRSTF 低功耗复位标志(自动),由软件通过写RMVF 位清除,定义:0(无低功耗管理复位发生),1(发生低功耗管理复位)

30位:WWDGRSTF 窗口看门狗复位标志(自动),由软件通过写RMVF 位清除,定义:0(无复位发生),1(有复位发生)

29位:IWDGRSTF 窗口看门狗复位标志(自动),由软件通过写RMVF 位清除,定义:0(无复位发生),1(有复位发生)

28位:SFTRSTF 软件复位标志(自动)由软件通过写RMVF 位清除,定义:0(无复位发生),1(有复位发生)

27位:PORRSTF 上电掉电复位标志(自动),由软件通过写RMVF 位清除,定义:0(无复位发生),1(有复位发生)

26位:PINRSTF-NRST 引脚复位标志(自动),由软件通过写RMVF 位清除,定义:0(无复位发生),1(有复位发生)

24位:RMVF 清除复位标志(手动),定义:0(无作用),1(清除复位标志)

1位:LSIRDY 内部低速振荡器就绪(自动),在LSION 清零后,3个内部40K 振荡周期后LSIRDY 被清零,定义:0(内部未就绪),1(内部RC 振荡器开启)

313029282726252423222120191817

151413121110987654321

313029282726252423222120191817

151413121110987654321

313029282726252423222120191817

151413121110987654321

IDR15IDR14IDR13IDR12IDR11IDR10IDR9IDR8IDR7IDR6IDR5IDR4IDR3IDR2IDR1

313029282726252423222120191817

151413121110987654321

ODR15ODR14ODR13ODR12ODR11ODR10ODR9ODR8ODR7ODR6ODR5ODR4ODR3ODR2ODR1313029282726252423222120191817

BR15BR14BR13BR12BR11BR10BR9BR8BR7BR6BR5BR4BR3BR2BR1

151413121110987654321

BS15BS14BS13BS12BS11BS10BS9BS8BS7BS6BS5BS4BS3BS2BS1

313029282726252423222120191817

31-16位:BRy 清除端口x 的位,这些位只能写入并只能以字的形式操作,定义:0(对应的ODRy 位不产生影响),1(清除对应ODRy 位为0)

15-0位:Bsy 设置端口x 的位,这些位只能写入并只能以字的形式操作,定义:0(对应的ODRy 位不产生影响),1(设置对应ODRy 位为1)

注:如果同时设置了Bsy 和Bry 的对应位,Bsy 位起作用。

GPIOx_BRR (端口位清除寄存器x=A,E )

保留

GPIOx_ODR (端口输出数据寄存器x=A,E )

0位:LSION 内部低速振荡器使能(软件),定义:0(内部振荡器关闭),1(内部振荡器开启)

GPIOx_CRL(端口配置低寄存器x=A,E)

MODE1[1:0]CNF0[1:0]MODE0[1MODE5[1:0]CNF5[1:0]CNF4[1:0]CNF7[1:0]MODE7[1:0]CNF6[1:0]MODE6[1:0]GPIOx_CRH(端口配置高寄存器x=A,E)

31-0双位:MODE 端口x 的模式位(软件控制0-7管脚)定义:00(输入模式(复位后模式),01(最大10M 输入),10(最大2M 输出),11(最大50M 输出)

在输出模式(MODE[1:0]>00)下:00(通用推挽),01(通用开漏),10(复用推挽),11(复用开漏)

CNF15[1:0]MODE15[1:0]CNF14[1:0]MODE14[1:0]CNF13[1:0]MODE13[1:0]CNF12[1:0]MODE12[CNF11[1:0]MODE11[1:0]CNF10[1:0]MODE10[1:0]CNF9[1:0]MODE9[1:0]CNF8[1:0]MODE8[1GPIO 输入输出相关寄存器

31-0单位:CNF 端口x 配置位(软件控制0-7管脚)定义:在输入模式[1:0]=00下:00(模拟输入),01(浮空输入(复位后状态),10(上/下拉输入),11(保留MODE4[1CNF3[1:0]MODE3[1:0]CNF2[1:0]MODE2[1:0]CNF1[1:0]31-0单位:CNF 端口x 配置位(软件控制8-15管脚)定义:在输入模式[1:0]=00下:00(模拟输入),01(浮空输入(复位后状态),10(上/下拉输入),11(保留 在输出模式(MODE[1:0]>00)下:00(通用推挽),01(通用开漏),10(复用推挽),11(复用开漏)

31-0双位:MODE 端口x 的模式位(软件控制8-15管脚)定义:00(输入模式(复位后模式),01(最大10M 输入),10(最大2M 输出),11(最大50M 输出)

GPIOx_IDR (端口输入数据寄存器x=A,E )

保留

15-0位:IDRy 端口输入数据(y=15-0)这些位为只读并只能以16位的形式读出。读出的值为对应IO 的状态。

GPIOx_BSRR (端口位设置/清除寄存器x=A,e )

15-0位:ODRy 端口输出数据(y=15-0)这些位可读可写并只能以字的形式操作。注:对GPIOx_BSRR ,可以分别的对各个ODR 位进行独立的设置/清除。

151413121110987654321

BR15BR14BR13BR12BR11BR10BR9BR8BR7BR6BR5BR4BR3BR2BR1

313029282726252423222120191817

151413121110987654321

LCK15LCK14LCK13LCK12LCK11LCK10LCK9LCK8LCK7LCK6LCK5LCK4LCK3LCK2LCK1

313029282726252423222120191817

151413121110987654321

EVOE 313029282726252423222120191817

ADC2REG ADC2INJ ADC1REGADC1INJ

151413121110987654321

PD01TIM4USART3USART1I2C

USART3_REMAP CAN_REMAP[1:0]TIM3_REMAP TIM2_REMAP TIM1_REMAP 1000(选择Px8),1001(选择Px9),1010(选择Px10),1011(选择Px11),1100(选择Px12),1101(选择Px13),1110(选择Px14),1111(选择Px15)

AFIO_EVCR (事件控制寄存器)

AFIO_MAPR (复用重映射和调试IO 配置寄存器)

保留SWJ_CFG[2:0]保留7位:EVOE 允许事件输出(手动)当设置该位后,Cortex 的EVENOUT 将连接到由PORT[2:0]和PIN[3:0]选定的IO 口

6-4位:PORT[2:0]端口选择,选择用于输出Cortex 的EVENTOUT 信号的端口。定义:000(PA ),001(PB ),010(PC ),011(PD ),100(PE )

3-0位:PIN[3:0]引脚选择,选择用于输出Cortex 的EVENTOUT 信号引脚,

定义:0000(选择Px0),0001(选择Px1),0010(选择Px2),0011(选择Px3),0100(选择Px4),0101(选择Px5),0110(选择Px6),0111(选择Px7)

保留

16位:LCKK 锁键,该位可随时读出,它只可通过锁键写入序列修改,定义:0(端口配置锁键位激活),1(端口配置锁位被激活,下次复位前GPIOx_LCKR 被锁住) 锁键写序列:写1-》写0-》写1-》读0-》读1 最后一个读可省略,但可以用来确认锁键已被激活

保留

注:在操作锁键的写入序列时,不能改变LCK[15-0]的值,且操作写入序列中的任何错误将不能激活锁键

15-0位:LCKy 端口x 的锁位y (y=0-15)这些位可读可写但只能在LCKK 位为0时写入,定义:0(不锁定端口的配置),1(锁定端口的配置)

保留PORT[2:0]PIN[3:0]

保留

15-0位:Bry 清除端口x 的位(y=15-0)这些位只能写入并只能以字的形式操作,定义:0(对对应位无影响),1(清除对应位的ODR 位为0)

GPIOx_LCKR (端口配置锁定寄存器x=A,E )

ADC1注入转换外部触发与EXTI15相连;当该位置1时,ADC1注入转换外部触发与TIM8通道4相连。

ADC2注入转换外部触发与EXTI15相连;当该位置1时,ADC2注入转换外部触发与TIM8通道4相连。

17位:ADC1_ETRGINJ_REMAP-ADC1注入转换外部触发重映射(手动),它控制与ADC1注入转换外部触发相连的触发输入。当该位置0时

26-24位:SWJ_CFG[2:0]串行线JTAG 配置,这些位只可由软件写,读这些位将返回未定义的数值。用于配置SWJ 和跟踪复用功能IO 口。SWJ (串行JTAG )

支持JTAG 或SWD 访问Cortex 的调试端口。系统复位后的默认状态时启用SWJ 但没有跟踪功能,这种状态下可以通过JTMS/JTCK 脚上的特定信号选择JTAG 或SW 模 定义:000(完全SWJ ,复位状态),001(完全SWJ ,但没有NJTRST ),010(关闭JATG 启动SW ),100(关闭JATG ,关闭SW )

20位:ADC2_ETRGREG_REMAP-adc2规则转换外部触发重映射(手动)它控制与ADC2注入转换外部触发相连的触发输入。当该位置0时,

ADC2规则转换外部触发与EXTI11相连;当该位置1时,ADC2规则转换外部触发与TIM8_TRGO 相连

19位:ADC2_ETRGINJ_REMAP-ADC2注入转换外部触发重映射(手动),它控制与ADC2注入转换外部触发相连的触发输入。当该位置0时

18位:ADC1_ETRGREG_REMAP-adc1规则转换外部触发重映射(手动)它控制与ADC1注入转换外部触发相连的触发输入。当该位置0时,

16位:TIM5CH4_IREMAP-TIM5通道4内部重映射(手动)它控制TIM5通道4内部映像。定义:0(TIM5_CH4与PA3相连),1(LSI 内部振荡器与TIM5_CH4相连,对LSI 校准

ADC1规则转换外部触发与EXTI11相连;当该位置1时,ADC1规则转换外部触发与TIM8_TRGO 相连

12位:TIM4_REMAP 定时器4的重映像(手动)控制将TIM4的通道1-4映射到GPIO 上

11-10位:TIM3_REMAP[1:0]定时器3重映像(手动),控制定时器3的1-4通道在GPIO 端口的映像

9-8位:TIM2_REMAP[1:0]定时器2重映像(手动)控制定时器2的1-4通道和外部触发ETR 在GPIO 端口的映像

7-6位:TIM1_REMAP[1:0]定时器1的重映像(手动)控制定时器1的通道1-4、1N-3N 、外部触发和刹车输入在GPIO 的映像

15位:PD01_REMAP 端口D0/端口D1映像到OSC_IN/OSC_OUT (手动)当不使用HSE 时PD0和PD1可映像到这两个管脚,定义:0(不映像),1(PD0-IN ,PD1-OUT )14-13位:CAN_REMAP[1:0]CAN 复用功能重影像(手动)在只有单个CAN 接口的产品上控制复用功能的重映像

5-4位:USART3_REMAP[1:0]USART3的重映像(手动)控制USART3的CTS 、RTS 、CK 、TX 、RX 复用功能在GPIO 端口的映像

3位:USART2_REMAP[1:0]USART3的重映像(手动)控制USART2的CTS 、RTS 、CK 、TX 、RX 复用功能在GPIO 端口的映像

2位:USART1_REMAP-USART1的重映像(手动)控制USART1的TX 、RX 复用功能在GPIO 端口的映像

1位:I2C1_REMAP-I2C1的重映像控制I2C1的SCL 和SDA 复用功能在GPIO 端口的映像

313029282726252423222120

191817151413121110987654

321313029282726252423222120

191817151413121110987654

321313029282726252423222120

191817151413121110987654

321313029282726252423222120

191817151413121110987654

321313029282726252423

222120191817

MR19MR18MR17

151413121110987654321

MR15MR14MR13MR12MR11MR10MR9MR8MR7MR6MR5MR4MR3MR2MR1

313029282726252423222120191817EXTI0[3:0]0位:SPI1_REMAP-SPI1的重映像控制SPI1的NSS 、SCK 、MISO 、MOSI 复用功能在GPIO 端口的映像

保留

15-0位:EXTI[3:0]EXTIx (x=0-3)配置(手动)用于选择EXTIx 外部中断输入源

定义:0000(PA[x]引脚),0001(PB[x]引脚),0010(PC[x]引脚),0011(PD[x]引脚),0100(PE[x]引脚),0101(PF[x]

引脚),0110(PG[x]引AFIO_EXTICR2(外部中断配置寄存器2)

AFIO_EXTICR1(外部中断配置寄存器1)

中断和事件相关寄存器

保留

EXTI3[3:0]EXTI2[3:0]EXTI1[3:0]

定义:0000(PA[x]引脚),0001(PB[x]引脚),0010(PC[x]引脚),0011(PD[x]引脚),0100(PE[x]引脚),0101(PF[x]

引脚),0110(PG[x]引15-0位:EXTI[3:0]EXTIx (x=4-7)配置(手动)用于选择EXTIx 外部中断输入源

EXTI7[3:0]EXTI6[3:0]EXTI5[3:0]

EXTI4[3:0]AFIO_EXTICR3(外部中断配置寄存器3)

保留

EXTI11[3:0]EXTI10[3:0]EXTI9[3:0]

EXTI8[3:0]EXTI15[3:0]EXTI14[3:0]EXTI13[3:0]

EXTI12[3:0]15-0位:EXTI[3:0]EXTIx (x=8-11)配置(手动)用于选择EXTIx 外部中断输入源

定义:0000(PA[x]引脚),0001(PB[x]引脚),0010(PC[x]引脚),0011(PD[x]引脚),0100(PE[x]引脚),0101(PF[x]

引脚),0110(PG[x]引AFIO_EXTICR4(外部中断配置寄存器4)

保留

保留19-0位:MRx 线x 上的事件屏蔽,定义:0(屏蔽来自线x 上的事件请求),1(开放来自线x 上的时间请求)注:19只用于互联型,对其他芯片保留

15-0位:EXTI[3:0]EXTIx (x=12-15)配置(手动)用于选择EXTIx 外部中断输入源

定义:0000(PA[x]引脚),0001(PB[x]引脚),0010(PC[x]引脚),0011(PD[x]引脚),0100(PE[x]引脚),0101(PF[x]引脚),0110(PG[x]引

EXTI_IMR (中断屏蔽寄存器)EXTI_EMR (中断屏蔽寄存器)

MR19MR18MR17

151413121110987654321

MR15MR14MR13MR12MR11MR10MR9MR8MR7MR6MR5MR4MR3MR2MR1

313029282726252423222120191817

TR19TR18TR17

151413121110987654321

TR15TR14TR13TR12TR11TR10TR9TR8TR7TR6TR5TR4TR3TR2TR1

313029282726252423222120191817

TR19TR18TR17

151413121110987654321

TR15TR14TR13TR12TR11TR10TR9TR8TR7TR6TR5TR4TR3TR2TR1

313029282726252423222120191817

SWIER19SWIER18SWIER17

151413121110987654321

SWIER15SWIER14SWIER13SWIER12SWIER11SWIER10SWIER9SWIER8SWIER7SWIER6SWIER5SWIER4SWIER3SWIER2SWIER1313029282726252423222120191817

PR19PR18PR17

151413121110987654321

PR15PR14PR13PR12PR11PR10PR9PR8PR7PR6PR5PR4PR3PR2PR1

19-0位:MRx 线x 上的事件屏蔽,定义:0(屏蔽来自线x 上的事件请求),1(开放来自线x 上的时间请求)注:19只用于互联型,对其他芯片保留

保留EXTI_RTSR (上升沿触发选择寄存器)

保留0-19位:TRx 线x 的上升沿触发时间配置位,定义:0(禁止输入线x 上的上升沿触发(中断和事件),1(允许输入线x 上的上升沿触发(中断和时间)注19位用于互联型

注:通过清除EXTI_PR 的对应位(写1),可清除该位为0,19位为互联型,对其他芯片为保留

保留19-0位:PRx 挂起位,定义:0(没有发生触发请求),1(发生了选择的触发请求) 注:19位用于互联型,对其他产品为保留位

EXTI_FTSR (下降沿触发选择寄存器)

保留0-19位:TRx 线x 的上升沿触发时间配置位,定义:0(禁止输入线x 上的上升沿触发(中断和事件),1(允许输入线x 上的上升沿触发(中断和时间)注19位用于互联型

EXTI_SWIER

EXTI_PR (挂起寄存器)

保留19-0位:SWIERx 线x 上的软件中断,当该位为0时,写1将设置EXTI_PR 中相应的挂起位。如果在EXTI_IMR 和EXTI_EMR 中允许产生中断,则此时将产生一个中断。

313029282726252423222120191817

TEIF7HTIF7TCIF7GIF7TEIF6HTIF6TCIF6GIF6TEIF5HTIF5TCIF5

151413121110987654321

TEIF4HTIF4TCIF4GIF4TEIF3HTIF3TCIF3GIF3TEIF2HTIF2TCIF2GIF2TEIF1HTIF1TCIF1313029282726252423222120191817

CTEIF7CHTIF7CTCIF7CGIF7CTEIF6CHTIF6CTCIF6CGIF6CTEIF5CHTIF5CTCIF5

151413121110987654321

CTEIF4CHTIF4CTCIF4CGIF4CTEIF3CHTIF3CTCIF3CGIF3CTEIF2CHTIF2CTCIF2CGIF2CTEIF1CHTIF1CTCIF1313029282726252423222120191817

151413121110987654321

保留MEM2MEM MINC PINC CIRC DIR TEIE HTIE TCIE

313029282726252423222120191817

151413121110987654321

3位:TEIE 允许传输错误中断(手动)定义:0(禁止TE 中断),1(允许TE 中断)

2位:HEIE 允许半传输中断(手动)定义:0(禁止TE 中断),1(允许TE 中断)

1位:TCIE 允许传输完成中断(手动)定义:0(禁止TE 中断),1(允许TE 中断)

0位:EN 开启通道(手动)定义:0(不工作),1(开启)

保留

13和12位:PL[1:0]通道优先级(手动),定义:00(低),01(中),10(高),11(最高)

11和10位:MSIZE[1:0]存储器数据宽度(手动)定义:00(8位),01(16位),10(32位),11(保留)

保留

PL[1:0]MSIZE[1:0]PSIZE[1:0]27,23,19,15,11,7,3位:CTEIFx 清除通道x 的传输错误标志(x=1,7)(手动)定义:0(无效),1(清除DMA_ISR 寄存器中的对应TEIF 标志)

25,21,17,13,9,5,1位:CTCIFx 清除通道x 的传输完成标志(x=1,7)(手动)定义:0(无效),1(清除DMA_ISR 寄存器中的对应HTIF 标志)

24,20,16,12,8,4,0位:CGIFx 清除通道x 的全局中断标志(x=1,7)(手动)定义:0(无效),1(清除DMA_ISR 寄存器中的对应HTIF 标志)

保留DMA_CCRx (DMA 通道x 配置寄存器x=1,7)

14位:MEM2MEM 存储器到存储器模式(手动),定义:0(非存储器到存储器模式),1(启动存储器到存储器模式)

DMA_CNDTRx (DMA 通道x 传输数量寄存器x=1,7)

7位:MINC 存储器地址增量模式(手动)定义:0(不执行存储器地址增量操作),1(执行存储器地址增量操作)

6位:PINC 外设地址增量模式(手动)定义:0(不执行存储器地址增量操作),1(执行存储器地址增量操作)

5位:CIRC 循环模式(手动)定义:0(不执行循环操作),1(执行循环操作)

4位:DIR 数据传输方向(手动)定义:0(从外设读),1(从存储器读)

9和8位PSIZE[1:0]外设数据宽度(手动)定义:00(8位),01(16位),10(32位),11(保留)

保留27,23,19,15,11,7,3位:TEIFx 通道x 的传输错误标志(x=1,7)(硬件控制)在DMA_IFCR 寄存器的相应位写1可清除这些标志位,定义:0(无错),1(有错)26,22,18,14,10,6,2位:HTIFx 通道x 的办传输标志(x=1,7)(硬件控制)在DMA_IFCR 寄存器的相应位写1可清除这写位,定义:0(无半传输事件),1(有)25,21,17,13,9,5,1位:TCIFx 通道x 的传输完成标志(x=1,7)(硬件控制)在DMA_IFCR 寄存器的相应位写入1可清除这些位,定义:(传输没完成),1(传输完成)24,20,16,12,8,4,0位:GIFx 通道x 的全局中断标志(x=1,7)(硬件控制)在DMA_IFCR 寄存器的相应位写入1可清除这些位,定义:0(没有TE/HT/TC 事件),1(有)

DMA_IFCR(DMA 中断标志清除寄存器)

DMA_ISR(DMA 中断状态寄存器

当在外部中断线上发生了选择的边沿事件,该位被置1。在该位中写入1可以清除它,也可以通过改变边沿检测的极性清除。

DMA 相关寄存器

26,22,18,14,10,6,2位:CHTIFx 清除通道x 的办传输标志(x=1,7)(手动)定义:0(无效),1(清除DMA_ISR 寄存器中的对应HTIF 标志)

313029282726252423222120191817

151413121110987654321

313029282726252423222120191817

151413121110987654321

待传输字节数目。寄存器内容在每次DMA 传输后递减。数据传输结束后,寄存器的内容或者变为0,或者当该通道配置为自动重加载模式时,寄存器的内容 被自动重新加载为之前配置时的数值。当寄存器的内容为0时,无论通道是否开启,都不会发生任何数据传输

PA

PA

NDT

15-0位:DNT[15:0]数据传输数量,数据传输数量为0到65535。这个寄存器只能在通道不工作(DMA_CCRx 的EN=0)时写入,通道开启后该寄存器变为只读指令剩余的31-0位:PA[31:0]外设地址,外设数据寄存器的基地址,作为数据传输的源或目标,当开启通道(DMA_CCRx 的EN=1)时不能写该寄存器,

DMA_CPARx (DMA 通道x 外设地址寄存器x=1,7)

DMA_CMARx (DMA 通道x 存储器地址寄存器x=1,7)

MA

当PSIZE=01(16位),不使用PA[0]位。操作自动的与半字节地址对齐,当PSIZE=10(32位)时,不使用PA[1:0]位。操作自动的与字地址对齐

MA

31-0位:MA[31:0]外设地址,外设数据寄存器的基地址,作为数据传输的源或目标,当开启通道(DMA_CCRx 的EN=1)时不能写该寄存器,

31

3029282726252423222120191817151413121110987654321

STRT JSTRT JEOC EOC

313029282726252423222120191817

AWDEN JAWDEN 151413121110987654321

JDISCN DISCEN JAUTO AWDSGL SCAN JEOCIE AWDIE EOCIE 313029282726252423222120191817

TSVREFE SWSTARTJSWSTART EXTTRIG 151413121110987654321

JEXTTRIG ALIGN DMA RSTCAL CAL CONT 保留EXTSEL[2:0]

JEXTSEL[2:0]保留保留7位:JEOCIE 允许产生注入通道转换结束中断(手动)用于禁止或允许所有注入通道转换结束后产生的中断,定义:0(禁止JEOC 中断),1(当置位JEOC 时产生中断保留9位:AWDSGL 扫描模式中在一个单一的通道上使用看门狗(手动)用于开启或关闭AWDCH[4:0]位指定的通道上的看门狗功能,定义:(在所有通道用),1(单一通道10位:JAUTO 自动的注入通道组转换,(手动)用于开启或关闭规则通道组转换结束后自动的注入通道组转换,定义:0(关闭自动注入通道组的转换),1(开启)11位:DISCEN 在规则通道上的间断模式,(手动)用于开启或关闭规则通道组函的间断模式,定义:0(规则通道组注上禁用间断模式),1(使用)

12位:JDISCEN 在注入通道上的间断模式,(手动)用于开启或关闭注入通道组上的间断模式,定义:0(注入通道注组上禁用间断模式),1(使用)

15-13位:DISCNUM[2:0]间断模式通道计数,软件通过这些位定义在间断模式下收到外部触发后转换规则通道的数目,定义:000(1通道)001(2通道)111(8通道 同步丢失,建议在进行任何配置改变前关闭双模式

1000(慢速交叉模式),1001(交替触发模式)注:在ADC2和ADC3中这些位为保留,在双模式中,改变通道的配置会产生一个重新开始的条件,则将导致8位:SCAN 扫描模式(手动)用于开启或关闭扫描模式,在扫描模式中,转换由ADC_SQRx 或ADC_JSQRx 寄存器选中的通道,定义:0(关闭),1(使用扫描模式)0位:AWD 模拟看门狗标志,该位在硬件转换的电压值超出了ADC_LTR 和ADC_HTR 寄存器定义的范围时置位,由软件清0,定义:0(没事件),1(有事件)

1位:转换结束位(该位由硬件在(规则或注入)通道组转换结束时设置,由软件清除或由读取ADC_DR 时清除,定义:0(转换未完成),1(转换完成)

0011(混合同步注入+快速交叉模式),0100(混合同步注入+慢速交叉模式),0101(注入同步模式),0110(规则同步模式),0111(快速交叉模式)19-16位:DUALMOD[3:0]双模式选择(手动)定义:0000(独立模式),0001(混合同步规则+注入同步模式),0010(混合同步规则+交替触发模式)

22位:JAWDEN 在注入通道上开启模拟看门狗(手动)定义:0(在规则通道上禁用模拟开门狗),1(使用)

23位:AWDEN 在规则通道上开启模拟看门狗(手动)定义:0(在规则通道上禁用模拟开门狗),1(使用)

保留DUALMOD[3:0]

DISCNUM[2:0]AWDCH[4:0]

4-0位:AWDCH[4:0]模拟看门狗通道选择位(手动)选择模拟看门狗保护的输入通道,00000(0通道)00001(1通道)01111(16)10000(16)10001(17)其他保 注:ADC1的模拟输入通道16和17在芯片内部分别连到了温度传感器和Vrefint ,ADC2的模拟输入通道16和17连到了VSS ,ADC3模拟输入9/14/15/16/17与VSS

23位:TSVREFE 温度传感器和Vrefint 使能(手动)在多余1个ADC 的器件中该位仅出现在ADC1中,定义:0(禁止),1(开启)

ADC_CR1(ADC 控制寄存器1)

ADC 相关寄存器

当MSIZE=01(16位),不使用MA[0]位。操作自动的与半字节地址对齐,当MSIZE=10(32位)时,不使用MA[1:0]位。操作自动的与字地址对齐

ADC_SR (ADC 状态寄存器)保留ADC_CR2(ADC 控制寄存器2)

2位:JEOC 注入通道转换结束位(硬件在所有注入通道转换结束时设置,由软件清0)定义:0(转换未完成),1(转换完成)

3位:JSTRT 注入通道开始位(硬件在开始转换时置位,软件清0)定义:0(规则通道未开始转换),1(规则通道已开始转换)

4位:STRT 规则通道开始位(硬件在开始转换时置位,软件清0)定义:0(规则通道未开始转换),1(规则通道已开始转换)

保留6位:AWDIE 允许产生模拟看门狗中断(手动),在扫描模式下,如果看门狗检测到超范围数值时,只有在设置了该位时扫描才会终止。定义:0(禁止),1(允许5位:EOCIE 允许产生EOC 中断(手动)用于禁止或允许转换后产生中断,定义:0(禁止EOC 中断),1(允许,当硬件置位EOC 时产生中断)

22位:SWSTART 开始转换规则通道(软件启动该位,转换后硬件马上清除此位)如果在EXTSEL[2:0]位中选择了SWSTART 为触发事件,该位用于启动一组规则通道的转

313029282726252423222120191817

151413121110987654321

SMP15[0]313029282726252423222120191817

保留151413121110987654321

SMP5[0]313029282726252423222120191817

151413121110987654321

15位:JEXTTRIG 注入通道的外部触发转换模式(手动)定义:0(不用外部事件启动转换),1(使用外部事件启动转换)

21位:JSWSTART 开始转换注入通道,(软件启动该位,转换后硬件马上清除此位)如果在JEXTSEL[2:0]位中选择了JSWSTART 位触发事件,启动一组注入通道的转换 定义:0(复位状态),1(开始转换注入通道)

定义:000(T1的CC1事件)001(T1的CC2事件)010(T1的CC3事件)011(T2的CC2事件)100(T3的TRGO 事件)101(T4的CC4事件)110EXTI 线11/T8_TRGO 事 111(SWSTART )

ADC_JOFRx(ADC 注入通道数据偏移寄存器x=1,4)

ADC_SMPR1(ADC 采样时间寄存器)

SMP14[2:0]SMP13[2:0]SMP12[2:0]SMP11[2:0]SMP10[2:0]ADC_SMPR1(ADC 采样时间寄存器)

23-0位:SMPx[2:0]选择通道x 的采样时间,定义:000(1.5周期)001(7.5)010(13.5)011(28.5)100(41.5)101(55.5)110(71.5)111(239.5)

SMP7[2:0]20位:EXTTRIG 规则通道的外部触发转换模式(手动),定义:0(不用外部事件启动转换),1(使用外部事件启动转换)

19-17位:EXTSEL[2:0]选择启动规则通道组转换的外部事件,这些位选择用于启动规则通道组转换的外部事件,ADC1和ADC2的触发配置如下

定义:0(复位状态),1(开始转换规则通道)

14-12位:JEXTSEL[2:0]选择启动注入通道转换的外部事件,这些位选择用于启动注入通道组转换的外部事件,定义:ADC1和ADC2的触发配置如下

8位:DMA 字节存储器访问模式(手动)定义:0(不使用DMA 模式),1(使用)

11位:ALIGN 数据对齐(手动)定义:0(右对齐),1(左对齐)

ADC3触发配置,定义:000(T1的TRGO)001(T1的CC4)010(T4的CC3)011(T8的CC2)100(T8的CC4)101(T5的TRGO)110(T5的CC4)111(JSWSTART)

111(SWSTART)

ADC3的触发配置如下:000(T3的CC1事件)001(T2的CC3事件)010(T1的CC3事件)011(T8的CC1事件)100(T8的TRGO 事件)101(T5的CC1事件)110(T5的CC3事件)3位:RSTCAL 复位校准(手动,在校准寄存器被初始化后该位将被清除,定义:0(校准寄存器已初始化),1(初始化校准寄存器)

注:如果正在进行转换时设置RSTCAL ,清除校准寄存器需要额外的周期

2位:CAL-A/D 校准(该位软件置1,在校准结束时由硬件清除),定义:0(校准完成),1(开始校准)

1位:CONT 连续转换(手动,如果设置此位则转换将连续进行直到该位被清除),定义:0(单词转换),1(连续转换)

111(JSWSTART)

定义:000(T1的TRGO 事件)001(T1的CC4事件)010(T2的TRGO 事件)011(T2的CC1事件)100(T3的CC4事件)101(T4的TRGO 事件)110(EXTI 线15/T8_CC4事件)

0位:ADON 开关AD 转换器(手动)当该位为0时,写入1将把ADC 从断电模式下唤醒。当该位为1时,写入1将启动转换,应用程序需注意,在转换器上电转换开始有 一个延迟Tstab ,定义:0(关闭ADC 转换和校准,并进入断电模式),1(开启ADC 并启动转换)

保留SMP17[2:0]SMP16[2:0]SMP15[2

注:如果在这个寄存器与ADON 一起还有其他位改变,则转换不被触发。则是为了防止触发错误的转换。

SMP6[2:0]SMP5[2

SMP0[2:0]29-0位:SMPx[2:0]选择通道x 的采样时间,定义:000(1.5周期)001(7.5)010(13.5)011(28.5)100(41.5)101(55.5)110(71.5)111(239.5)

SMP9[2:0]SMP8[2:0]SMP4[2:0]SMP3[2:0]SMP2[2:0]SMP1[2:0]保留

保留JOFFSETx

11-0位:JOFFSETx[11:0]注入通道x 的数据偏移,当转换注入通道时,这些位定义了用于从原始转换数据中减去的数值。转换的结果可以在ADC_JDRx 寄存器中读出

ADC_HTR (ADC 看门狗高阀值寄存器)

31

3029282726252423222120191817151413121110987654

321313029282726252423222120

191817151413121110987654

321313029282726252423222120

191817151413121110987654

321SQ16313029282726252423222120

191817151413121110987654

321SQ10[0]313029282726252423222120

191817151413121110987654

321

SQ4[0]ADC_SQR3(ADC 规则序列寄存器3)

14-10位:SQ3[4:0]规则序列中的第3个转换

保留SQ6[4:0]SQ5[4:0]

SQ4[4:0]SQ3[4:0]SQ2[4:0]

SQ1[4:0]ADC_LRT (ADC 看门狗低阀值寄存器)

ADC_SQR1(ADC 规则序列寄存器1)

ADC_SQR2(ADC 规则序列寄存器2)

保留保留HT[11:0]

11-0位:HT[11:0]模拟看门狗高阀值,这些位定义了模拟看门狗的阀值高限。

保留

保留

11-0位:LT[11:0]模拟看门狗低阀值,这些位定义了模拟看门狗的阀值低限

L[3:0]

SQ16[4:1]SQ15[2:0]9-5位:SQ14[4:0]规则序列中的第14个转换

14-10位:SQ15[4:0]规则序列中的第15个转换

19-15位:SQ16[4:0]规则序列中的第16个转换,这些位由软件定义转换序列中的第16个转换通道的编号(0~17)。

23-20位:L[3:0]规则通道序列长度,这些位由软件定义在规则通道转换序列中的通道数目,定义:0000(1个转换),1111(16个转换)

SQ13[2:0]SQ14[2:0]

19-15位:SQ10[4:0]规则序列中的第10个转换,

24-20位:SQ11[4:0]规则序列中的第11个转换,

29-25位:SQ12[4:0]规则序列中的第12个转换,这些位由软件定义转换序列中的第12个转换通道的编号(0~17)。

4-0位:SQ13[4:0]规则序列中的第13个转换

保留SQ12[4:0]SQ11[4:0]

SQ10[4:0]29-25位:SQ6[4:0]规则序列中的第6个转换,这些位由软件定义转换序列中的第12个转换通道的编号(0~17)。

24-20位:SQ5[4:0]规则序列中的第5个转换,

19-15位:SQ4[4:0]规则序列中的第4个转换,

9-5位:SQ2[4:0]规则序列中的第2个转换,SQ9[4:0]SQ8[4:0]

SQ7[4:0]4-0位:SQ7[4:0]规则序列中的第7个转换,

9-5位:SQ8[4:0]规则序列中的第8个转换,

14-10位:SQ9[4:0]规则序列中的第9个转换

31302928272625242322212019

1817

151413121110987654321

JSQ4[0]313029282726252423222120191817

151413121110987654321

313029282726252423222120191817

151413121110987654321

ADC_DR (ADC 规则数据寄存器)

31-16位:ADC2DATA[15:0]ADC2转换的数据,在ADC1中:双模式下,这些位包含了ADC2转换的规则通道数据,在ADC2和ADC3中:不使用这些位DATA[15:0]

ADC2DATA[15:0]

ADC_JSQRADC (注入序列寄存器)19-15位:JSQ4[4:0]注入序列中的第4个转换,这些位由软件定义转换序列中的第4个转换通道的编号(0~17)。

21-20位:JL[1:0]注入通道序列长度,这些位由软件定义在规则通道转换序列中的通道数目。定义:00(1个转换),01(2个转换),10(3个转换),11(4个转JSQ1[4:0]

JSQ2[4:0]4-0位:SQ1[4:0]规则序列中的第1个转换,

保留JL[3:0]JSQ4[4:1]

4-0位:JSQ1[4:0]:注入序列中的第1个转换

保留

JDATA[15:0]

15-0位:JDATA[15:0]注入转换的数据,这些位为只读,包含了注入通道的转换结果。数据是左对齐或右对齐

ADC_JDRx (ADC 注入数据寄存器x=1,4)

JSQ3[4:0]9-5位:JSQ3[4:0]:注入序列中的第2个转换

14-10位:JSQ3[4:0]:注入序列中的第3个转换

意味着扫描转换将按下列通道顺序转换:7、3、3,而不是2、7、3。

注:不同于规则转换序列,如果JL[1:0]的长度小于4,则转换的序列顺序是从(4-JL)开始。例如:ADC_JSQR[21:0] = 10 00011 00011 00111 00010

313029282726252423222120191817

DMAEN2TEN2BOFF2

151413121110987654321

DMAEN2TEN1BOFF1

313029282726252423222120191817

151413121110987654321

SWTRIG2

7-6位:WAVE1[1:0]DAC 通道1噪声/三角波生成使能(手动)定义:00(关闭波形发生器)10(使能噪声波形发生器)1x (使能三角波发生器)

5-3位:TSEK1[2:0]DAC 通道1触发选择,该3位用于选择DAC 通道1的外部触发事件,定义:000(TIM6 TRGO 事件)001(F107时T3的TRGO 事件,对于F103是T8的TRGO 事DAC_CR (DAC 控制寄存器)

18位:TEN2DAC 通道2触发使能(手动)使能/关闭DAC 通道2的触发,定义:0(关闭触发,写入DAC_DHRx 寄存器的数据在1个APB1时钟周期后传入DAC_DOR2寄存器)15-0位:规则转换的数据,这些位为只读,包含了规则通道的转换结果。数据是左对齐或右对齐

保留 注意:该3位只能在TEN2 = 1(DAC 通道2触发使能)时设置

MAMP2[3:0]WAVE2[2:0]TSEL2[2:0]21-19位:TSEK2[2:0]DAC 通道2触发选择,该3位用于选择DAC 通道2的外部触发事件,定义:000(TIM6 TRGO 事件)001(F107时T3的TRGO 事件,对于F103是T8的TRGO 23-22位:WAVE2[1:0]DAC 通道2噪声/三角波生成使能(手动)定义:00(关闭波形发生器)10(使能噪声波形发生器)1x (使能三角波发生器)

1010:[10:0] / 2047;≥1011: [11:0] / 4095

0011: [3:0]/15;0100:[4:0] / 31;0101:[5:0] /63;0110:[6:0] / 127;0111:[7:0] / 255;1000:[8:0] / 三511;1001:[9:0] / 102 定义:0000:不屏蔽LSFR 位0 / 三角波幅值等于1;0001:不屏蔽LSFR 位[1:0] / 三角波幅值等于3;0010:不屏蔽LSFR 位[2:0] / 三角波幅值等于7;27-24位:MAMP2[3:0]DAC 通道2屏蔽/幅值选择器(手动)用来在噪声生成模式下选择屏蔽位,在三角波生成模式下选择波形的幅值

28位:DMAEN2-DAC 通道2 DMA 使能,该位由软件设置和清除,定义:0(关闭DAC 通道2DMA 模式),1(使能)

保留 0011: [3:0]/15;0100:[4:0] / 31;0101:[5:0] /63;0110:[6:0] / 127;0111:[7:0] / 255;1000:[8:0] / 三511;1001:[9:0] / 102 010(TIM7 TRGO 事件)011(TIM5 TRGO 事件)100(TIM2 TRGO 事件)101(TIM4 TRGO 事件)110(外部中断线9)111(软件触发)

12位:DMAEN1-DAC 通道1 DMA 使能(手动),定义:0(关闭DAC 通道1 DMA 模式),1(使能DAC 通道1 DMA 模式)

11-8位:MAMP1[3:0]DAC 通道1屏蔽/幅值选择器(手动)用来在噪声生成模式下选择屏蔽位,在三角波生成模式下选择波形的幅值

定义:0000:不屏蔽LSFR 位0 / 三角波幅值等于1;0001:不屏蔽LSFR 位[1:0] / 三角波幅值等于3;0010:不屏蔽LSFR 位[2:0] / 三角波幅值等于7;MAMP1[3:0]WAVE1[2:0]TSEL1[2:0] 010(TIM7 TRGO 事件)011(TIM5 TRGO 事件)100(TIM2 TRGO 事件)101(TIM4 TRGO 事件)110(外部中断线9)111(软件触发)

1010:[10:0] / 2047;≥1011: [11:0] / 4095

2位:TEN1DAC 通道1触发使能(手动)使能/关闭DAC 通道1的触发,定义:0(关闭触发,写入DAC_DHRx 寄存器的数据在1个APB1时钟周期后传入DAC_DOR2寄存器) 1:使能DAC 通道2触发,写入DAC_DHRx 寄存器的数据在3个APB1时钟周期后传入DAC_DOR1寄存器。

1位:BOFF1关闭DAC 通道1输出缓存,用来使能/关闭DAC 通道1的输出缓存,定义:0(使能DAC 通道1输出缓存)1(关闭DAC 通道1输出缓存)

注意:如果选择软件触发,写入寄存器DAC_DHRx 的数据只需要1个APB1时钟周期就可以传入寄存器DAC_DOR1。

1:使能DAC 通道2触发,写入DAC_DHRx 寄存器的数据在3个APB1时钟周期后传入DAC_DOR2寄存器。

注意:如果选择软件触发,写入寄存器DAC_DHRx 的数据只需要1个APB1时钟周期就可以传入寄存器DAC_DOR2。

17位:BOFF2关闭DAC 通道2输出缓存,用来使能/关闭DAC 通道2的输出缓存,定义:0(使能DAC 通道2输出缓存)1(关闭DAC 通道2输出缓存)

注意:该3位只能在TEN1 = 1(DAC 通道1触发使能)时设置

16位:EN2DAC 通道2使能,定义:0(关闭DAC 通道2),1(使能DAC 通道2)

0位:DAC 通道1使能,(手动),0(关闭),1(使能)

DAC_SWTRIGR (DAC 软件触发寄存器)

保留1位:SWTRIG2-DAC 通道2软件触发,定义:0(关闭DAC 通道2软件触发),1(使能DAC 通道2软件触发)

保留

DAC 相关寄存器

飞思卡尔锁相环

备战飞思卡尔智能车大赛.开始模块总结. 锁相环设置. 公式: PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1), fbus=PLLCLK/2 void INIT_PLL(void) { CLKSEL &= 0x7f; //选用外部时钟.准备设置锁相环 PLLCTL &= 0x8F; //禁止锁相环 SYNR = 0xc9; //设置SYNR REFDV = 0x81; //设置REFDV PLLCTL |=0x70; //锁相环使能 asm NOP; asm NOP; //两个机器周期缓冲时间 while(!(CRGFLG&0x08)); //等待锁相环锁定 CLKSEL |= 0x80; //设置锁相环为时钟源 } 飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频 单片机超频的原因和PC机是个一道理。分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY 这也和PC机南北桥的原理类似。总线频率设置过程 1、禁止总中断 2、寄存器CLKSEL(时钟选择寄存器)的第七位置0 即CLKSEL_PLLSEL=0。选择时钟源为外部晶振OSCCLK(外接晶振频率) 在PLL(锁相环)程序执行前 内部总线频率为OSCCLK/2 3. PLLCTL_PLLON=1 打开PLL 4.设置SYNR 时钟合成寄存器 、REFDV 时钟分频寄存器 、POSTDIV三个寄存器的参数 5、_asm(nop) _asm(nop);加入两条空指令 使锁相环稳定 6、while(!(CRGFLG_LOCK==1));//时钟校正同步 7、CLKSEL_PLLSEL=1; 下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构 VCOFRQ[1:0]控制压控振动器VCO的增益 默认值为00 VCO的频率与VCOFRQ[1:0]对应表

飞思卡尔单片机编程

关于Codewarrior 中的 .prm 文件 网上广泛流传的一篇文章讲述的是8位飞思卡尔单片机的内存映射,这几天,研究了一下Codewarrior 5.0 prm文件,基于16位单片机MC9S12XS128,一点心得,和大家分享。有什么错误请指正。 正文: 关于Codewarrior 中的.prm 文件 要讨论单片机的地址映射,就必须要接触.prm文件,本篇的讨论基于Codewarrior 5.0 编译器,单片机采用MC9S12XS128。 通过项目模板建立的新项目中都有一个名字为“project.prm”的文件,位于Project Settings->Linker Files文件夹下。一个标准的基于XS128的.prm文件起始内容如下: .prm文件范例: NAMES END SEGMENTS RAM = READ_WRITE DATA_NEAR 0x2000 TO 0x3FFF;

READ_ONLY DATA_NEAR IBCC_NEAR 0x4000 TO 0x7FFF; ROM_C000 = READ_ONLY DATA_NEAR IBCC_NEAR 0xC000 TO 0xFEFF; //OSVECTORS = READ_ONLY 0xFF10 TO 0xFFFF; EEPROM_00 = READ_ONLY DATA_FAR IBCC_FAR 0x000800 TO 0x000BFF; EEPROM_01 = READ_ONLY DATA_FAR IBCC_FAR 0x010800 TO 0x010BFF; EEPROM_02 = READ_ONLY DATA_FAR IBCC_FAR 0x020800 TO 0x020BFF; EEPROM_03 = READ_ONLY DATA_FAR IBCC_FAR 0x030800 TO 0x030BFF; EEPROM_04 = READ_ONLY DATA_FAR IBCC_FAR 0x040800 TO 0x040BFF; EEPROM_05 = READ_ONLY DATA_FAR IBCC_FAR 0x050800 TO 0x050BFF; EEPROM_06 = READ_ONLY DATA_FAR IBCC_FAR 0x060800 TO 0x060BFF; EEPROM_07 = READ_ONLY DATA_FAR IBCC_FAR 0x070800 TO 0x070BFF; PAGE_F8 = READ_ONLY DATA_FAR IBCC_FAR 0xF88000 TO 0xF8BFFF;

飞思卡尔单片机寄存器及汇编指令详解

附录I:寄存器地址列表 直接页面寄存器总结

高页面寄存器总结

非易失寄存器总结 注:直接页面寄存器表地址的低字节用粗体显示,直接寻址对其访问时,仅写地址低字节即可。第2列中寄存器名用粗体显示以区别右边的位名。有0的单元格表示未用到的位总是读为0,有破折号的单元格表示未用或者保留,对其读不定。

附录II 指令接与寻址方式 HCS08指令集概括 运算符 () = 括号种表示寄存器或存储器位置的内容 ← = 用……加载(读: “得到”) & = 布尔与 | = 布尔或 ⊕= 布尔异或 ×= 乘 ÷ = 除 : = 串联 + = 加 - = 求反(二进制补码) CPU registers A =>累加器 CCR =>条件代码寄存器 H =>索引寄存器,高8位 X => 索引寄存器,低8位 PC =>程序计数器 PCH =>程序计数器,高8位 PCL =>程序计数器,低8位 SP =>堆栈指针 存储器和寻址 M =>一个存储区位置或者绝对值数据,视寻址模式而定 M:M + 0x0001 => 两个连续存储位置的16位值.高8位位于M的地址,低8位位于更高的连续地址. 条件代码寄存器(CCR)位 V => 二进制补码溢出指示,第7位 H => 半进位,第4位 I => 中断屏蔽,第 3位 N => 求反指示器, 第2位 Z => 置零指示器, 第1位 C => 进/借, 第0位 (进位第 7位 ) CCR工作性符号 – => 位不受影响 0 = > 位强制为0 1 = > 位强制为1

= >根据运算结果设置或清除位 U = > 运算后没有定义 机器编码符号 dd =>一个直接寻址0x0000–0x00FF的低8位(高字节假设为0x00) ee => 16位偏移量的高8位 ff => 16位偏移量的低8位 ii => 立即数的一个字节 jj => 16位立即数值的高位字节 kk => 16位立即数值的低位字节 hh => 16位扩展寻址的高位字节 ll => 16位扩展寻址的低位字节 rr => 相对偏移量 n —任何表达范围在0–7之间的一个有符号数的标号或表达式 opr8i —任何一个表达8位立即值的标号或表达式 opr16 —任何一个表达16位立即值的标号或表达式 opr8a —任何一个表达一个8位值的标号或表达式.指令对待这个8位值为直接页面64K 字节地址空间(0x00xx)中地址的低8位. opr16a —任何一个表达16位值的标号或表达式.指令对待这个值为直接页面64K字节地址空间. oprx8 —任何一个表达8位无符号值的标号或表达式,用于索引寻址. oprx16 —任何一个16位值的标号或表达式.因为HCS08有一个16位地址总线,这可以为一个有符号或者无符号值. rel —任何指引在当前指令目标代码最后一个字节之后–128 to +127个字节之内的标号或表达式.汇编器会计算包括当前指令目标代码在内的8位有符号偏移量. 寻址方式 隐含寻址(Inherent)如CLRA,只有操作码,无操作数,需要操作的数据一般为CPU寄存器,因此不需要再去找操作数了。(INH) 立即寻址 (Immediate)如LDA #$0A,“$”表示16进制,此时操作数位于FLASH空间,与程序一起存放。(IMM) 直接寻址 (Direct)如 LDA $88,只能访问$0000-$00FF的存储器空间,指令短速度快; (DIR) 扩展寻址 (Extended)如果操作数地址超出了$00FF,自动为扩展寻址;(EXT) 相对寻址(Relative)如BRA LOOP,指令中一般给出8位有符号数表示的偏移量。(REL) 变址寻址 (Indexed) 采用[H:X]或SP作为指针的间接寻址方式。( IX )( IX1 )( IX2 ) 变址寻址 (Indexed) 1〉无偏移量:CLR ,X 简写(IX) 2〉无偏移量,指令完成后指针加1(H:X = H:X + 0x0001) ,简写(IX+)只用于指令MOV和CBEQ指令中;

飞思卡尔MC9S12XS128单片机中断优先级设置简易教程

本教程试图用最少的时间教你飞思卡尔XS128单片机的中断优先级设置方法和中断嵌套的使用,如果是新手请先学习中断的基本使用方法。 先来看看XS128 DataSheet 中介绍的相关知识,只翻译有用的: 七个中断优先级 每一个中断源都有一个可以设置的级别 高优先级中断的可以嵌套低优先级中断 复位后可屏蔽中断默认优先级为1 同一优先级的中断同时触发时,高地址(中断号较小)的中断先响应 注意:高地址中断只能优先响应,但不能嵌套同一优先级低地址的中断 下面直接进入正题,看看怎么设置中断优先级: XS128中包括预留的中断一共有128个中断位,如果为每个中断都分配一个优先级寄存器的话会非常浪费资源,因此飞思卡尔公司想出了这样一种办法:把128个中断分为16个组,每组8个中断。每次设置中断时,先把需要的组别告诉某个寄存器,再设置8个中断优先寄存器的某一个,这样只需9个寄存器即可完成中断的设置。 分组的规则是这样的:中断地址位7到位4相同的中断为一组,比如MC9SX128.h中 这些中断的位7到位3都为D,他们就被分成了一组。0~F正好16个组。

INT_CFADDR就是上面说到的用来设置组别的寄存器: 我们需要设置某个组别的中断时,只要写入最后8位地址就行了,比如设置SCI0的中断优先级,就写入0xD0。 设置好组别之后,我们就要该组中相应的中断进行设置,设置中断的寄存器为 这其实是一组寄存器,一共有8个,每个都代表中断组中的一个中断。对应规则是这样的:中断地址的低四位除以2 比如还是SCI0,低四位是6,除以二就是3,那么我们就需要设置INT_CFDATA3 往INT_CFDATAx中写入0~7就能设置相应的中断优先级了 拿我本次比赛的程序来举个例子:我们的程序中需要3个中断:PIT0,PORTH,SCI0。PIT0定时检测传感器数值,PORTH连接干簧管进行起跑线检测,SCI0接收上位机指令实现急停等功能。因此中断优先级要SCI0>PORTH>PIT0。 我们先要从头文件中找出相应中断的地址: PIT0【7:4】位为7,选择中断组: INT_CFADDR=0x70;

飞思卡尔寄存器整理

S12的输入/输入端口(I/O口) I/O端口功能 可设置为通用I/O口、驱动、内部上拉/下拉、中断输入等功能。 设置I/O口工作方式的寄存器有: DDR、IO、RDR、PE、IE和PS。 DDR:设定I/O口的数据方向。 IO :设定输出电平的高低。 RDR:选择I/O口的驱动能力。 PE:选择上拉/下拉。 IE:允许或禁止端口中断。 PS:1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。 I/O端口设置 1、A口、B口、E口寄存器 (1)数据方向寄存器DDRA、DDRB、DDRE DDRA、DDRB、DDRE均为8位寄存器,复位后其值均为0。 当DDRA=0、 DDRB=0、 DDRE=0 时A口、B口和E口均为输入口。 否则,A口、B口、E口为输出口。当DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。 例如,将A口设置为输出口,则其C语言程序的语句为:DDRA=0xff; (2)A口、B口、E口上拉控制寄存器PUCR PUCR为8位寄存器,复位后的值为0。当PUPAE、PUPBE、PUPEE被设置为1时,A口、B口、E口具有内部上拉功能;为0时,上拉无效。当A口、B 口、E口为地址/数据总线时,PUPAE和PUPBE无效。 (3)A口、B口、E口降功率驱动控制寄存器RDRIV RDRIV为8位寄存器,复位后的值为0,此时,A口、B口、E口驱动保持全功率;当RDPA、RDPB、RDPE为1时, A口、B口、E口输出引脚的驱动功率下降 (4)数据寄存器PORTA、PORTB、PORTE PORTA、PORTB、PORTE均为8位寄存器,复位后的值为0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。 由于PE0是/XIRQ、PE1是IRQ,因此,PE0和PE1只能设置为输入。

飞思卡尔单片机外设模块寄存器翻译

PIT 模块译: 翻译来自MC9S12X128英文原文PDF.P347-P357 PIT 块结构图: PIT0中断向量66, 1->67, 2->68, 3->69 PIT 相关寄存器详解: 1、 PITCFLMT :寄存器基本控制和基本时钟加载控制寄存器(8位) 1:PIT 使能 PITSWAI: 0:等待模式下仍然工作 1:等待模式下不工作 PITFRZ: 0:冻结模式下仍然工作 1:冻结模式下不工作 PFLMT1: 写1强制加载基本定时计数器1,写0无效,读也总为0 PFLMT0: 同PFLMT1 2、 PITFLT :PIT 计数器强制加载定时器寄存器(8位)

PFLT[3:0]写1相对应的16位计数寄存器会立即载入相对应的16位计数加载寄存器(PITLDn)中的值。 3、PITCE:PIT通道使能存器(8位) PCE[3:0]:如果PITE已经使能,对寄存器PCEn写1后,每输入一个时钟相对应的计数寄存器 开始递减,写0无效。 4、PITMUX:PIT基本时钟通道选择寄存器(8位) PMUX[3:0]:对PMUXn写1,则对应定时器通道选择基本时钟1作为输入,写0则选择基本时 钟0为输入。 5、PITINTE:PIT定时中断使能寄存器(8位) PINTE[3:0]:对PINTEn写1,当相对应的计数寄存器和基本计数寄存器归0时,产生中断请求,否则无效。 6、PITTF:PIT时钟输出标志寄存器(8位)

7、PITMTLD0-1:PIT基本时钟计数器预加载寄存器(8位) 会被加载到基本定时器n,无论什么时刻PFLMTn置“1”会立即更新基本定时器寄存器的值. 8、PITLD0–3:PIT0-3计数器预加载寄存器(16位) PITLD0-3的值用来加载到相对应计数器0-3的寄存器中。当相应通道计数器归零时,或PITFLT寄存器中相应的强制加载位置“1”时,PITLDn中的值将会被立即加载到PITCNTn。 9、PITCNT0–3:PIT0-3计数寄存器(16位) 变计数周期。

飞思卡尔单片机 DG128 Timer寄存器说明

Timer寄存器说明 1、定时器/计数器系统控制寄存器1(TSCR1) TSCR1 寄存器是定时器模块的总开关,它决定模块是否启动以及在中断等待、BDM 方式下的行为,还包括标志的管理方式。其各位的意义如下: TEN:定时器使能位,此外它还控制定时器的时钟信号源。要使用定时器模块的IC/OC 功能,必须将TEN 置位。如果因为某种原因定时器没有使能,脉冲累加器也将得不到ECLK/64 时钟,因为ECLK/64 是由定时器的分频器产生的,这种情况下,脉冲累加器将不能进行引脚电平持续时间的累加。 0:定时器/计数器被禁止,有利于降低功耗。 1:定时器/计数器使能,正常工作。 TSWAI:等待模式下计时器关闭控制位。 【注意】定时器中断不能用于使MCU 退出等待模式。 0:在中断等待模式下允许MCU 继续运行。 1:当MCU 进入中断等待模式时,禁止计时器。 TSFRZ:在冻结模式下计时器和计数器停止位。 0:在冻结模式下允许计时器和计数器继续运行。 1:在冻结模式下禁止计时器和计数器,用于仿真调试。 【注意】TSFRZ 不能停止脉冲累加。 TFFCA:定时器标志快速清除选择位。 0:定时器标志普通清除方式。 1:对于TFLGl($0E)中的各位,读输入捕捉寄存器或者写输出比较寄存器会自动清除相应的标志位CnF。对于TFLG2($0F)中的各位,任何对TCNT 寄存器($04、$05)的访问均会清除TOF 标志;任何对PACN3 和PACN2 寄存器($22,$23)的访问都会清除PAFLG 寄存器($21)中的PAOVF 和PAIF 位。任何对PACN1 和PACN0 寄存器($24,$25)的访问都会清除PBFLG 寄存器($21)中的PBOVF 位。 【说明】这种方式的好处是削减了另外清除标志位的软件开销。此外,必须特别注意避免对标志位的意外清除。 2、计时器系统控制寄存器2(TSCR2) 寄存器偏移量:$000D

飞思卡尔MC9S12XET256 SCI串口寄存器说明

串口寄存器说明 该模块指南提供了串行通信接口(SCI)模块概述。 SCI的允许与外围设备和其他CPU异步串行通信。 1.1 SCI包括这些特征: ?全双工或单线运行 ?标准标记/空间不归零(NRZ)格式 ?可选的IrDA1.4返回到零倒置(RZI)与可编程脉冲宽度格式 ?13位的波特率选择 ?可编程8位或9位数据格式 ?分别使能发射机和接收机 ?可编程极性对发射机和接收机 ?可编程发送器输出校验 ?两个接收器唤醒的方法: -唤醒空闲线 - 地址标志唤醒 ?中断驱动的操作有八个标志: -发送器空 - 传输完成 - 接收器满 - 空闲接收器输入 - 接收器溢出 -噪声误差 -帧错误 - 奇偶错误 - 接收有效边缘唤醒 - 发送冲突检测支持LIN -间隔检测支持LIN ?接收帧错误检测 ?硬件奇偶校验 ?1 / 16位时间噪声检测 1.2 操作模式 SCI的功能相同在正常、特殊和仿真模式。它有两种低功耗模式,等待和停止模式。 ?运行模式 ?等待模式 ?停止模式 1.3 寄存器说明 1、波特率控制寄存器(SCIBDH、SCIBDL) SCIBDH和SCIBDL一起构成了一个16位的波特率控制寄存器。SBR12~~SBR0为波特率常数。

IREN:红外调制模式使能位 1 使能 0 禁止 TNP[0..1]:窄脉冲发射位,这些位使能SCI是否能发送一个1 / 16,3 /16,1/ 32或1 / 4的窄脉冲。见表20-3。 SBR[0..12]:波特率设置位 When IREN = 0 then, SCI baud rate = SCI bus clock / (16 x SBR[12:0]) When IREN = 1 then, SCI baud rate = SCI bus clock / (32 x SBR[12:1]) 【说明】波特率发生器在复位后是禁止的,在设置TE、RE(在SCICR2寄存器中)后才会工作。当(SBR[12:0] = 0 and IREN = 0) 或者(SBR[12:1] = 0 andIREN = 1),波特率发生器不工作。 【注意】在未写入SCIBDL,写SCIBDH没有反应。一般地,设置IREN=0,SR=52(总线频率8MHz),波特率为9600。 2、控制寄存器(SCICR1) 一般此寄存器可默认设置。

飞思卡尔寄存器使用

PLLSEL:选定锁环位 1 选定锁相环时钟0 选定外部时钟 PSTP:选定伪停止位伪停止模式下振荡器(工作1)/(停止0) SYSWAI:选定时钟停止位等待模式下系统时钟(停止1)/(继续工作0) ROAWAI:等待模式下降低振荡器放大倍数位 1 等待模式下降低振荡器放大倍数 0 等待模式下振荡器正常放大倍数 PLLWAI:等待模式下锁相环停止工作位 1等待模式下锁相环停止工作 0等待模式下锁相环正常工作 CWAI:等待模式下内核时钟停止工作位 1 等待模式下内核时钟停止工作 0 等待模式下内核时钟正常工作 RTIWAI:等待模式下实时时钟停止工作位 1 等待模式下实时时钟停止工作 0 等待模式下实时时钟正常工作 COPWAI:等待模式下看门狗时钟停止工作位 1 等待模式下看门狗时钟停止工作 0 等待模式下看门狗时钟正常工作 CME:时钟监控使能位。 PLLON:锁相环电路使能位。 AUTO:自动带宽控制位 1 选择高频带宽控制0 选择低频带宽控制 ACQ:自动带宽控制滤波器选择位(当AUTO=1时,该位无意义)。 PRE:CPU 伪停止状态时,实时中断(RT1)允许位。 PCE:CPU 虚拟停止时,看门狗(COP)允许位。 SCEM:自给时钟方式使能位,默认为1,探测到外部晶振停振时进入自给时钟模式,为0时,

禁止自给时钟模式,探测到外部晶振停振时复位。 时钟合成寄存器SYNR 读写Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Read 0 0 SYN5 SYN4 SYN3 SYN2 SYN1 SYN0 Write VCOFRQ[1:0](BIT7 BIT6)控制压控振动器VCO的增益,默认值为00,VCO的频率与VCOFRQ[1:0]对应表如下所示: 读写Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Read/Write REFFRQ1 REFFRQ0 REFDV5 REFDV4 REFDV3 REFDV2 REFDV1 REFDV0 REFFRQ[1:0]默认值为00,表示参考时钟频率在1~2MHZ之间,要求的参考时钟频率与REFFRQ[1:0]的设置值如下表如示: 读写Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Read RTIF PORF 0 LOCKIF LOCK TRACK SCMIF SCM Write RTIF:实时中断(RTI)标志位 1 发生实时中断0 未发生实时中断PROF:上电复位标志位 1 发生上电复位0 未发生上电复位LOCKIF:锁相环中断标志位 1 锁相环锁定位发生变化时,产生中断请求 0 锁相环锁定位未发生变化

飞思卡尔MC9S12XS128(定时器)ECT寄存器详解

1、定时器IC/OC功能选择寄存器TIOS IOS[7..0]IC/OC功能选择通道 0 相应通道选择为输入捕捉(IC) 1 相应通道选择为输出比较(OC) 2、定时器比较强制寄存器 CFORC FOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。 【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。 3、输出比较7屏蔽寄存器 OC7M OC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于 OC7的管理之下。OC7M中的各位与PORTT口寄存器的各位一一对应。当通过 TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输 出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状 态。 【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn 设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7D OC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。OC7D中的各位与PORTT口寄存器的各位一一对 应。当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输 出到PORTT的对应引脚。 【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。比如:OC7M0=1,则通道0处在OC7的管理 下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。另 外,在OC7Mn置位后,相应的引脚就被设置为输出引脚,与DDRTn无关了,OC7Mn 并不改变DDR相应位的状态。 5、定时器核心计数寄存器 TCNT TCNT[15..0]XS128 Timer模块的核心是一个16位自由运行计数器(TCNT),所有输入捕捉和输出比较功能的计时信息都来源于TCNT,当定时器系统启用时,通过设置TSCR1的 TEN位,计数器从$0000开始,每经过一个模块时钟加1,直到加到$FFFF,然后自动 溢出为$0000并继续计数.16位自由记数器的当前值保存在两个8位寄存器中,高 的存在TCNTH,低的存在TCNTL中.综合这两个寄存器就形成TCNT.定义TCNT的 话,要定义为word型。 【说明】这里的模块时钟指的是,经过分频后的ECT模块所用的时钟,分频系数在TSCR2的低三位。TCNT是一个递增的计数器,有很多人一直把它当做是递减的计数器。总之,TCNT就是对ECT时钟进行计数的。

飞思卡尔入门程序总结

1.对IO口输入输出操作程序举例:A口接流水灯并实现闪烁 void main(void) { while(1) { DDRA=0xff; delay(500); PORTA=0xff; delay(500); PORTA=0; } 另外,B、E口的IO功能操作也是一样的,因为位数一样寄存器一样,其他口的寄存器就不太一样了!J,P,M,T,S这五个口除具有数据寄存器外,他们都另外多出另一个端口输入寄存器(该寄存器功能我未知)! 2.SPI总线接口 SPI是一种高速高效的同步串行接口,这种接口主要用于MCU与外部的接口芯片交换数据,只要有SPI口的芯片都可以与单片机相连形成主从机系统进行数据的传递,比如SPI用于移位寄存器74HC164,这是个串入并出的芯片这样可以实现扩展IO口。 还有AD转换芯片AD7793,可以实现数模转换,还有飞思卡尔公司的电源管理芯片MC33389。 因设备有限此功能待以后调试! 3.SCI总线接口 MC9S12DG128单片机有两个SCI模块,可以选用其中任何一个。他的使用有8个相应寄存器共设置,其中有波特率设置寄存器SCIBDH,SCIBDL,还有控制寄存器SCICR1,SCICR2,状态寄存器SCISR1,SCISR2,数据寄存器SCIDRH,SCIDRL; 简单讲SCI的使用就是寄存器初始化,数据传送方式设置,下面举个初始化使用的简单例子:SCICR2=0x08;//发送使能设置 SCIBDH=0x00;//波特率设置为9600 SCIBDL=0x9c; 就是这样这个是简单实用时的设置,发送函数如下: While(!(SCISR1&0x40))//检测是否发送完毕,一旦发送完毕就进入到死循 环里边 {} SCIDRL=C;//C代表需要传送的数据 4.有关定时器TCNT TCNT是芯片内部的16位主定时器,他不停地对内部时钟信号进行计数,从0x0000直到0xffff,计满后溢出又返回到0x0000,程序随时可以读取,但在普通模式下禁止写入。 TCNT应该按字访问,分别访问高低字节将出现错误! 可以直接利用它的来实现一些延时的功能! 例如下面的程序: #include

飞思卡尔单片机各种功能程序

流水灯四种效果: #include

飞思卡尔MC9S12G系列芯片之【GPIO】模块总结

GPIO模块总结(以MC9S12G128为例)一、常见功能 二、端口详解 1、引脚图 小注: 1)除BKGD外,其余引脚都可用作通用的输入输出口。 2)EXTAL(PE0、12脚):外部晶振(时钟)输入引脚。

3)XTAL(PE1、14脚):内部晶体驱动输出引脚 4)IRQ(PB4、47脚):可屏蔽中断(即可由用户控制),芯片接收外部事件中断的主要手段,低电平或下降沿时产生中断请求。 2、分类 1)S12G128共有100个I/O口,其中通用I/O口84个,各端口所含寄存器如下图所示: 小注: 每个端口大部分为复用端口,通过配置相关寄存器可实现I/O口与不同模块或外设之间的数据通信。 2)各端口寄存器名称、位数(含有几个通道口)及常见功能说明如下表所示:由表1)可以看出: PORTA~PORTE端口所含寄存器种类相同; PORTP、PORTJ、PORTAD三者相同; PORTS、PORTM两者相同; PORTT单独为一种类型 按类型进行总结如下:

小注: a. 由上表可知,这五个寄存器通过同一个电阻控制寄存器PUCR的0~4位分别对应控制端口A~D; b. 在学习板中(这是前提,以下模块与寄存器的连接仅限此开发板): LED灯是通过PORTA寄存器控制,LED1~LED8分别对应PORTA的P0~P7位(注意两者的对应关系)。 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0 LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8 即寄存器的位与LED的排列顺序是相反的,给寄存器赋值时应注意。

小注: 端口P和J都含有7个寄存器,其中与中断有关的寄存器有两个:中断使能寄存器PIEx及中断标志寄存器PIFx。

飞思卡尔智能车程序汇总

1.流水灯程序: #include 2.液晶屏按键程序 #include 一、输入输出端口寄存器 I/O接口包括PORTA、B、E、K、T、S、M、P、H、J、AD。其中PORTA、B、E、K属于复用扩展总线接口,单片机在扩展方式下工作时,作为总线信号。 1、PORTT、S、M、P、H、J I/O寄存器PTx 如果对应位数据方向寄存器DDRx为“0”,输入,读取该寄存器返回引脚值;“1”,输出,读取该寄存器返回I/O寄存器的内容。 数据方向寄存器DDRx 决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。 上拉/下拉使能寄存器PERx 选择使用内置上拉/下拉器件,“1”允许,“0”禁用。 中断使能寄存器PIEx PORTP、H、J三个端口具有中断功能。“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。 中断标志寄存器PIFx PORTP、H、J三个端口具有中断功能。“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。 2、PORTA、B、E、K I/O寄存器Px 若某端口的引脚被定义为输出,写入I/O寄存器中的数值会从对应引脚输出;输入,通过I/O 寄存器读取对应引脚电平。 数据方向寄存器DDRx 决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。PORTE最低两位只能为输入。 上拉电阻控制寄存器PERx 第7、4、1、0位分别控制K、E、B、A端口,“1”允许使用对应端口的上拉电阻,“0”禁止,复位后,PK、PE端口使能,PB、PA禁止。 二、中断系统 中断控制寄存器INTCR 第7位IRQE,中断电平/边沿有效选择,0为低电平有效,1为下降沿有效; 第6位IRQEN,外部中断IRQ中断请求使能,0关闭,1允许。 三、PWM模块 PWM允许寄存器PWME 对应每一位PWMEx,1启动输出,0停止输出,读写任意时刻。 PWM预分频时钟选择寄存器PWMPRCLK 为Clock A和B选择独立的预分频因子,读写任意时刻。 Clock B对应6、5、4三位,Clock A对应2、1、0三位,分别可以实现2、4、8、16、32、64、128分频。 PWM比例因子寄存器A、B,PWMSCLA、PWMSCLB Clock SA=Clock A/(2*PWMSCLA) =$00时,默认值为256 PWM时钟选择寄存器PWMCLK 对应每一位是PCLKx,7、6、3、2通道:1选择Clock SB,0选择Clock B,5、4、1、0通道:1选择Clock SA,0选择Clock A。读写任意时刻。 。 先来看看XS128 DataSheet 中介绍的相关知识,只翻译有用的: 七个中断优先级 每一个中断源都有一个可以设置的级别 高优先级中断的可以嵌套低优先级中断 复位后可屏蔽中断默认优先级为1 同一优先级的中断同时触发时,高地址(中断号较小)的中断先响应 注意:高地址中断只能优先响应,但不能嵌套同一优先级低地址的中断 下面直接进入正题,看看怎么设置中断优先级: XS128中包括预留的中断一共有128个中断位,如果为每个中断都分配一个优先级寄存器的话会非常浪费资源,因此飞思卡尔公司想出了这样一种办法:把128个中断分为16个组,每组8个中断。每次设置中断时,先把需要的组别告诉某个寄存器,再设置8个中断优先寄存器的某一个,这样只需9个寄存器即可完成中断的设置。 分组的规则是这样的:中断地址位7到位3相同的中断为一组,比如MC9SX128.h中 这些中断的位7到位3都为D,他们就被分成了一组。0~F正好16个组。 INT_CFADDR就是上面说到的用来设置组别的寄存器: 我们需要设置某个组别的中断时,只要写入最后8位地址就行了,比如设置SCI0的中断优先级,就写入0xD0。 设置好组别之后,我们就要该组中相应的中断进行设置,设置中断的寄存器为 这其实是一组寄存器,一共有8个,每个都代表中断组中的一个中断。对应规则是这样的:中断地址的低四位除以2 比如还是SCI0,低四位是6,除以二就是3,那么我们就需要设置INT_CFDATA3 往INT_CFDATAx中写入0~7就能设置相应的中断优先级了 拿我本次比赛的程序来举个例子:我们的程序中需要3个中断:PIT0,PORTH,SCI0。PIT0定时检测传感器数值,PORTH连接干簧管进行起跑线检测,SCI0接收上位机指令实现急停等功能。因此中断优先级要SCI0>PORTH>PIT0。 我们先要从头文件中找出相应中断的地址: PIT0【7:4】位为7,选择中断组: INT_CFADDR=0x70; 【3:0】为A,A/2=5,设置为第5优先级那么 1)团队有个大致分工 即团队成员有个大致的负责侧重点,但是要明白软件与硬件是分不开的,注意彼此相互学校。 2)熟悉核心控制芯片(今年是S12XS128系列的) 9S12XS128这类芯片看起来挺复杂,确实也挺复杂,不过用到的模块却不多,所以不要担心,你完全可以把它当成普通的51来学,你要用到哪里你就搞明白哪里,一个模块一个模块的做实验、调试。 核心掌握的模块有:.ECT ADC PWM MDC PLL SCI 因为要做一个智能车系统注意完成以下几个方面: ?单片机初始化模块,实时路径检测模块,舵机控制模块,驱动电机控制模块,中断速度采集模块。 ?(1)单片机的初始化模块包括:I/O模块、PWM模块、AD模块、计时器模块、定时中断模块初始化。 ?2)实时路径检测模块:光电传感器检测黑线,将返回信号输入单片机的输入端口,经单片机内部AD转换,进行分析,得出合适的PWM信号控制舵机转向。 ?3)舵机控制模块,驱动电机控制模块:通过直接输出PWM信号控制。舵机的控制采用开环控制,驱动电机采用PID算法控制。 所以让小车跑起来不难,接下来我分享下我调试各模块一些方法与经验 IO口模块程序示例 Void PORTB_Init(void){ DDRB=0xff; //PB口作输出使用,1为输出,0为输入 PORTB=0x00; //PB口数据寄存器值 } 注意:IO口要注意以下几点:(1)每个IO口的数据寄存器名可能不同(2)AN口只能作输入用(3)PH,PJ(高两位,低两位),PP可用输入中断功能使用(4)IO口作输入与输出时有不同的寄存器对应(5)IO口作复用时不能作IO口用,相反也不行 Freescale Kinetis KL25系列社区资料大全及实例汇总 介绍: Freescale 公司Kinetis KL25 MCU向L系列内增加了带集成低压稳压器的全速USB 2.0 OTG控制器,采用32位ARM Cortex-M0内核,拥有48MHz内核频率,工作电压为1.71V~3.6V,。KL25系列作为低功耗、低价格、高性能的微控制器,给工程师们提供了一个合适的入门级32位方案。 本文精选了Kinetis K25教程、例程、设计案例,以及基于Kinetis KL25的流行开发板,集结了国内外官方资料和资深工程师的经验,是学习Kinetis KL25 MCU的必备宝典。 Kinetis KL25 MCU 的功能框图 Kinetis KL25 MCU 教程篇 Kinetis KL25 MCU官方参考手册 Kinetis KL25 MCU 官方数据手册 飞思卡尔Kinetis系列产品开发资源链接总汇 包含Kinetis系列产品的参考手册、数据手册、编译环境、调试工具的相关资源链接。 KL25中文用户手册 官方Kinetis L系列三大特性演示视频(附中文说明文档) 你在设计中往往会忽略掉Kinetis L系列的重要的特性。如果你只是简单的把Kinetis L系列当做一般的Cortex-M0的单片机来使用的话,我们的设计人员估计要郁闷了。闲话少说,赶紧来看看你可能忽略的特性吧 Cortex-M0+, 到底“+”了什么(有视频,有中文文档) 飞思卡尔Kinetis L系列采用的内核是Cortex-M0+,而不是Cortex-M0。这个小小的加号到底增加了什么呢?小小视频讲的一清二楚。 根据KL系列芯片上的缩略标志识别具体型号 大家在使用kinetis芯片的时候,可能会发现一些比较小的芯片上并没有刻出芯片的具体型号,而是刻了一个缩略型号名称,那么如何根据这个缩略名称来识别具体的型号呢? 文中罗列了Kinetis L系列所有的缩略型号对应的芯片具体型号名称,方便大家识别。 KL25 TSI基本原理介绍 TSI(Touch Sensing Interface)模块是飞思卡尔为简化硬件设计人员开发而嵌入到Kinetis架构的电容触摸感应模块,本篇主要介绍TSI模块的基本原理。 KL25 ADC模块详细介绍 文中包含了ADC的模块框图以及对每个模块的详细介绍。 开发篇 FRDM-KL25 cdc win 7 DRIVER 下载 超核KL25固件库BetaV0.5 版 更新的主要内容: - 完善了几乎所有模块的注释,大家使用起来更方便飞思卡尔16位单片机寄存器分析总结

飞思卡尔XS128外部中断优先级设置简易教程

飞思卡尔主要寄存器初始化程序段

飞思卡尔 freescale Kinetis KL25系列资料大全及实例汇总

- 飞思卡尔嵌入式开发工具BDM汇总

- 飞思卡尔智能车程序汇总

- 飞思卡尔MC9S12XS128各模块初始化程序--超详细注释

- 飞思卡尔单片机 DG128 Timer寄存器说明

- 飞思卡尔单片机的讲解

- 飞思卡尔单片机

- 飞思卡尔主要寄存器初始化程序段

- 飞思卡尔MC9S12XS128单片机中断优先级设置简易教程

- 飞思卡尔寄存器使用

- 飞思卡尔MC9S12G系列芯片之【GPIO】模块总结

- 飞思卡尔单片机寄存器及汇编指令详解

- 飞思卡尔单片机编程

- 飞思卡尔单片机外设模块寄存器翻译

- 飞思卡尔入门程序总结

- 飞思卡尔S12系列寄存器和中断讲解

- 飞思卡尔XS128外部中断优先级设置简易教程

- 飞思卡尔8位单片机-第4章 寄存器与片内存储器

- 飞思卡尔智能小车算法介绍(个人总结)ppt课件

- 飞思卡尔单片机各种功能程序

- 飞思卡尔S12系列寄存器和中断