数字电路8

江西科技师范大学《数字电路》模拟试卷八

―――――――――――――――――――――――――――――――――― 一、填空题(每空1分,共20分)

1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL 与非门多余的输入端应接( )。 4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数??? ??+??? ??++=D C AB D C A B F ,该函数的反函数F =

( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。 8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )

。 9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。该ROM 有( )根地址线,有( )根数据读出线。

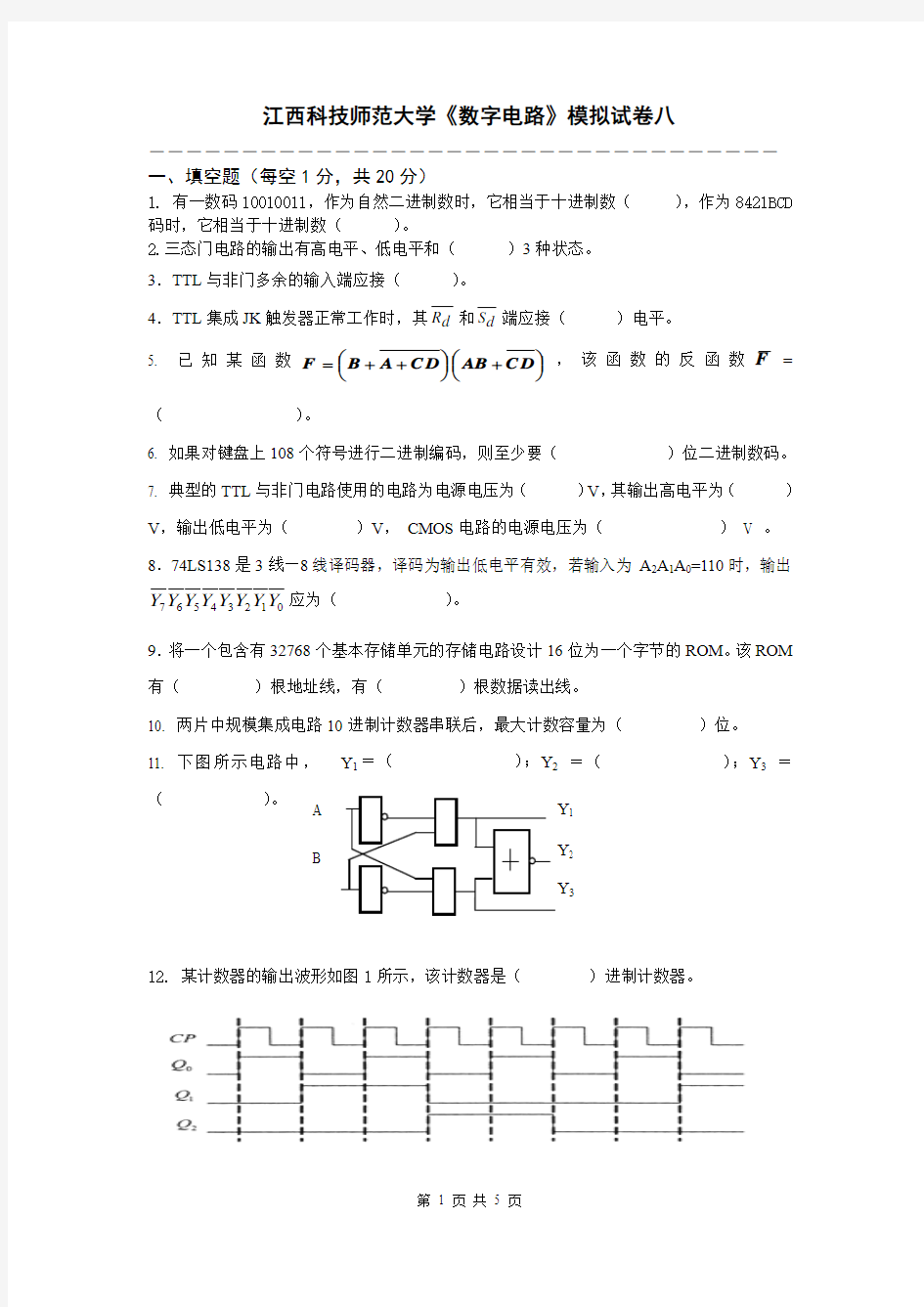

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。 11.

);Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)

(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。)

1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)

2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ??的值是( )。

A .111 B. 010 C. 000 D. 101

3.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.8

4. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。

A. 1011--0110--1100--1000--0000

B. 1011--0101--0010--0001--0000

C. 1011--1100--1101--1110--1111

D. 1011--1010--1001--1000--0111 5.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( ) 。

A. 11111101

B. 10111111

C. 11110111

D. 11111111 6. 一只四输入端或非门,使其输出为1的输入变量取值组合有( )种。 A .15 B .8 C .7 D .1 7. 随机存取存储器具有( )功能。 A.读/写 B.无读/写 C.只读 D.只写

8.N 个触发器可以构成最大计数长度(进制数)为( )的计数器。 A.N B.2N C.N 2

D.2N

9.某计数器的状态转换图如下, 其计数的容量为( )

A . 八 B. 五 C. 四 D. 三

10.已知某触发的特性表如下(A 、B 为触发器的输入)其输出信号的逻辑表达式为( )。

A . Q n+1 =A B. n n 1n Q A Q A Q +=+ C. n n 1n Q

B Q A Q +=+ D. Q n+1 = B 11. 有一个4位的D/A 转换器,设它的满刻度输出电压为10V ,当输入数字量为1101时,输出电压为( )。

A . 8.125V B.4V C. 6.25V D.9.375V

12.函数F=AB+BC ,使F=1的输入ABC 组合为( )

A .ABC=000

B .ABC=010

C .ABC=101

D .ABC=110 13.已知某电路的真值表如下,该电路的逻辑表达式为( )。

A .C Y = B. ABC Y = C .C A

B Y += D .

C C B Y +=

14.四个触发器组成的环行计数器最多有( )个有效状态。 A.4 B. 6 C. 8 D. 16

三、判断说明题(本大题共2小题,每小题5分,共10分)

(判断下列各题正误,正确的在题后括号内打“√”,错误的打“×”。) 1、逻辑变量的取值,1比0大。( )

2、D/A 转换器的位数越多,能够分辨的最小输出电压变化量就越小( )。 3.八路数据分配器的地址输入(选择控制)端有8个。( ) 4、因为逻辑表达式A+B+AB=A+B 成立,所以AB=0成立。( )

5、利用反馈归零法获得N 进制计数器时,若为异步置零方式,则状态S N 只是短暂的过渡状态,不能稳定而是立刻变为0状态。( ) 6.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。( ) 7.约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作 0。( )

8.时序电路不含有记忆功能的器件。( )

9.计数器除了能对输入脉冲进行计数,还能作为分频器用。( )

10.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码. ( )

四、综合题(共30分)

1.对下列Z 函数要求:(1)列出真值表;(2)用卡诺图化简;(3)画出化简后的逻辑图。(8分)

Z=C B A C B A B A ??+??+ BC=0

2.试用3线—8线译码器74LS138和门电路实现下列函数。(8分)

Z (A 、B 、C )=AB+A C

3.74LS161是同步4位二进制加法计数器,其逻辑功能表如下,试分析下列电路是几进制计数器,并画出其状态图。(8分)

74LS161逻辑功能表

CP

4.触发器电路如下图所示,试根据CP及输入波形画出输出端Q1、Q2 的波形。设各触发器的初始状态均为“0”(6分)。

模拟与数字电子电路基础作业答案5

作业5 截止日期:2015-5-25 要求:写出步骤,独立完成 内容:第八章、第十章 1.课本第八章练习8.2。(20分) 提示:参考例8.1。 参考解答:i DS=K/2*(V GS-V T)2=K/2*(V DS-V T)2 i ds=K/2*2*(V DS-V T)*v ds=K(V DS-V T)*v ds 2.课本第八章练习8.6。(20分) 提示:参考8.2.2和8.2.4节,图8.19。 参考解答:v O=V S-R L*K/2*(V GS-V T)2=V S-R L*K/2*(v1-V T)2 在v1=V1时的小信号模型如下: 所以:1)r o=R L; 2)R TH=R L,U TH=-R L*K(V1-V T)*vi 3)r i=

3.课本第八章问题8.2的a, b, c三小题。(20分) 提示: 参考解答:i DS=K/2*(V GS-V T)2 ;v IN=V GS+v OUT ; V GS=v IN-v OUT i DS=K/2*(V GS-V T)2=K/2*(v IN-v OUT-V T)2 ids=K/2*2*(V IN-V OUT-V T)=K(V IN-V OUT-V T)*vin;所以g m=K(V IN-V OUT-V T) vout=ids*R=RK(V IN-V OUT-V T)*vin;vout/vin=RK(V IN-V OUT-V T) 4.课本第十章练习10.16。 提示:参考10.1.3小节。 参考解答:i R1=i R2=i C;v2=R2*i R2; V1=(R1+R2)*i C+V C=(R1+R2)*C*dV C/dt+V C; V C=V1(1-e-t/((R1+R2)*C))=6(1-e-t/0.009)=6(1-e-1000t/9) V2=R2*i R2=R2*i C=R2*C*dV C/dt=2000*3*10-6*6*(-e-1000t/9*(-1000/9))=4e-1000t/9 5.课本第十章练习10.24。假设RC时间常量的值很小。 提示:参考10.7。

数字电路_第八章答案

8 数字系统设计基础习题解答 1 自我检测题 [T8.1] 什么是数字系统? 数字系统是指对数字信息进行存储、传输、处理的电子系统。只要包括控制单元和数据处理单元就称为数字系统。 [T8.2] 说明自顶向下的设计方法及步骤。 首先从系统设计入手,在顶层将整个系统划分成几个子系统,然后逐级向下,再将每个子系统分为若干功能模块,每个功能模块还可以继续向下划分成子模块,直至分成许多最基本模块实现。 练习题 [P8.1] 采用“自顶向下”设计方法设计一4位数字频率计,测量范围为0~9999Hz,假设被测信号为标准的方波信号。 解:(1)4位数字频率计的顶层原理图 AA[3..0]BB[3..0]CC[3..0]DD[3..0] (2)底层功能模块的设计 ①CNT10模块设计 根据顶层设计对CNT10模块的功能定义,其VHDL语言源程序编写如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY cnt10 IS PORT(clk:IN STD_LOGIC; clr:IN STD_LOGIC; cs:IN STD_LOGIC; qq:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

8 数字系统设计基础习题解答 2 co:OUT STD_LOGIC ); END cnt10; ARCHITECTURE one OF cnt10 IS BEGIN PROCESS(clk,clr,cs) BEGIN IF (clr=‘1’) THEN qq<=“0000”; ELSIF (clk'EVENT AND clk=‘1’) THEN IF (cs=‘1’) THEN IF (qq=9) THEN qq<=“0000”; ELSE qq<=qq+1; END IF; END IF; END IF; END PROCESS; PROCESS(qq) BEGIN IF (qq=9) THEN co<=‘0’; ELSE co<=‘1’; END IF; END PROCESS; END one; 根据频率计的原理图,前级计数器的进位输出作为下一级计数器的时钟输入。由于计数器采用时钟的上升沿触发,因此,计数器模块的进位输出设为低电平有效,以免下级计数器提前进位。 ②LOCK模块的设计 LOCK模块的功能是在锁存信号的上升沿将输入数据锁存到输出端,其VHDL语言源程序为: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

数字电子技术基础试题及答案 (1)

. 数字电子技术基础期末考试试卷 一、填空题 1. 时序逻辑电路一般由 和 两分组成。 2. 十进制数(56)10转换为二进制数为 和十六进制数为 。 3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。 4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。 5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。 二、化简、证明、分析综合题: 1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。 2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式: (2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R 1=1K Ω,R 2=8.2K Ω,C=0.1μF 。试求脉冲宽度 T ,振荡频率f 和占空比q 。 ………………………密……………………封…………………………装…………………订………………………线……………………… 系别 专业(班级) 姓名 学号

图1 5.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 时,1Y 、6Y 分别才为低电平(被译中)。 图2 6.触发器电路就输入信号的波形如图3所示,试分别写出D 触发器的Q 和Q1的表达式,并画出其波形。 图3 ………………封…………………………装…………………订………………………线………………………

D= Q n+1= Q1= 7. 已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表; ⑤电路功能。图4 三、设计题:(每10分,共20分) 1.设计一个三变量偶检验逻辑电路。当三变量A、B、C输入组合中的“1”的个数为偶数时F=1,否则F=0。选用8选1数选器或门电路实现该逻辑电路。要求: (1)列出该电路F(A,B,C)的真值表和表达式; (2)画出逻辑电路图。 2.试用74161、3-8译码器和少量门电路,实现图5所示波形VO1、VO2,其中CP为输入波形。要求: (1)列出计数器状态与V01、V02的真值表;

数字电路答案大全(DOC)

数字电路试卷答案大全 试卷A 一、选择题(从每小题的四个备选答案中,选出一个正确答案,并将其号码填在括号内,每小题2分,共 20分) 1.将十进制数(18)10转换成八进制数是 [ ] ① 20 ② 22 ③ 21 ④ 23 2. 三变量函数()BC A C B A F +=,,的最小项表示中不含下列哪项 [ ] ① m2 ② m5 ③ m3 ④ m7 3.一片64k ×8存储容量的只读存储器(ROM ),有 [ ] ①64条地址线和8条数据线 ②64条地址线和16条数据线 ③16条地址线和8条数据线 ④16条地址线和16条数据线 4.下列关于TTL 与非门的输出电阻描述中,正确的是 [ ] ①门开态时输出电阻比关态时大 ②两种状态都是无穷大输出电阻 ③门关态时输出电阻比开态时大 ④两种状态都没有输出电阻 5.以下各种ADC 中,转换速度最慢的是 [ ] ① 并联比较型 ② 逐次逼进型 ③ 双积分型 ④ 以上各型速度相同 6. 关于PAL 器件与或阵列说法正确的是 [ ] ① 只有与阵列可编程 ② 都是可编程的③ 只有或阵列可编程 ④ 都是不可编程的 7. 当三态门输出高阻状态时,输出电阻为 [ ] ① 无穷大 ② 约100欧姆 ③ 无穷小 ④ 约10欧姆 8.通常DAC 中的输出端运算放大器作用是 [ ] ① 倒相 ② 放大③ 积分 ④ 求和 9. 16个触发器构成计数器,该计数器可能的最大计数模值是 [ ] ① 16 ② 32 ③ 162 ④ 216 10.一个64选1的数据选择器有( )个选择控制信号输入端。 [ ] ① 6 ② 16 ③ 32 ④ 64 二、填空题(把正确的内容填在题后的括号内。每空1分,共15分。) 1.已知一个四变量的逻辑函数的标准最小项表示为 ()()13,11,9,8,6,4,3,2,0,,,m d c b a F ∑=,那么用最小项标准表 示 =*F ,以及=F ,使用最大项标准表示

数字电路与逻辑设计习题7第七章半导体存储器(精)

第七章半导体存储器 一、选择题 1.一个容量为1K ×8的存储器有个存储单元。 A.8 B.8K C.8000 D.8192 2.要构成容量为4K ×8的R AM ,需要片容量为256×4的R AM 。 A.2 B.4 C.8 D. 32 3.寻址容量为16K ×8的RAM 需要根地址线。 A.4 B. 8 C.14 D. 16 E.16K 4.若R AM 的地址码有8位,行、列地址译码器的输入端都为4个,则它们的 输出线(即字线加位线)共有条。 A.8 B.16 C.32 D.256 5.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。 A.8×3 B.8K ×8 C. 256×8 D. 256×256 6. 采用对称双地址结构寻址的1024×1的存储矩阵有。 A.10行10列 B.5行5列 C.32行32列 D. 1024行1024列 7.随机存取存储器具有功能。 A. 读/写 B. 无读/写 C. 只读 D. 只写 8.欲将容量为128×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译

码器的输出端数为。 A.1 B.2 C.3 D. 8 9.欲将容量为256×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译 码器的输入端数为。 A.4 B.2 C.3 D. 8 10.只读存储器ROM 在运行时具有功能。 A. 读/无写 B. 无读/写 C. 读/写 D. 无读/无写 11.只读存储器R OM 中的内容,当电源断掉后又接通,存储器中的内容。 A. 全部改变 B. 全部为0 C. 不可预料 D. 保持不变 12.随机存取存储器RAM 中的内容,当电源断掉后又接通,存储器中的内容。 A. 全部改变 B. 全部为1 C. 不确定 D. 保持不变 13.一个容量为512×1的静态RAM 具有。 A. 地址线9根,数据线1根 B. 地址线1根,数据线9根 C. 地址线512根,数据线9根 D. 地址线9根,数据线512根 14.用若干R AM 实现位扩展时,其方法是将相应地并联在一起。 A. 地址线 B. 数据线 C. 片选信号线 D. 读/写线 15.PROM 的与陈列(地址译码器)是。 A. 全译码可编程阵列 B. 全译码不可编程阵列

《数字电子技术基础》课后习题答案

《数字电路与逻辑设计》作业 教材:《数字电子技术基础》 (高等教育出版社,第2版,2012年第7次印刷)第一章: 自测题: 一、 1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路 5、各位权系数之和,179 9、01100101,01100101,01100110; 11100101,10011010,10011011 二、 1、× 8、√ 10、× 三、 1、A 4、B 练习题: 1.3、解: (1) 十六进制转二进制: 4 5 C 0100 0101 1100 二进制转八进制:010 001 011 100 2 1 3 4 十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10 所以:(45C)16=(10001011100)2=(2134)8=(1116)10 (2) 十六进制转二进制: 6 D E . C 8 0110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 000 3 3 3 6 . 6 2 十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1758.78125)10 所以:(6DE.C8)16=(011011011110. 11001000)2=(3336.62)8=(1758.78125)10

(3) 十六进制转二进制:8 F E . F D 1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 010 4 3 7 6 . 7 7 2 十六进制转十进制: (8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 所以:(8FE.FD)16=(100011111110.11111101)2=(437 6.772)8=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D 0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 010 3 6 3 6 . 7 7 2 十六进制转十进制: (79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:(8FE.FD)16=(011110011110.11111101)2=(3636.772)8=(1950.98828125)10 1.5、解: (74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD (45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD (136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD 1.8、解 (1)(+35)=(0 100011)原= (0 100011)补 (2)(+56 )=(0 111000)原= (0 111000)补 (3)(-26)=(1 11010)原= (1 11101)补 (4)(-67)=(1 1000011)原= (1 1000110)补

数字电子技术试卷及答案(免费版)

第1页(共28页) 第2页(共28页) 姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷 题 号 一 二 三 四(1) 四(2) 四(3) 四(4) 总 分 得 分 1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码 时,它相当于十进制数( )。 2.三态门电路的输出有高电平、低电平和( )3种状态。 3.TTL 与非门多余的输入端应接( )。 4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。 5. 已知某函数??? ??+??? ??++=D C AB D C A B F ,该函数的反函数F =( ) 。 6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。 7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。 8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( ) 。 9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。该ROM 有( )根地址线,有( )根数据读出线。 10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。 11. 下图所示电路中, Y 1=( );Y 2 =( );Y 3 =( )。 12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。 13.驱动共阳极七段数码管的译码器的输出电平为( )有效。 二、单项选择题(本大题共15小题,每小题2分,共30分) (在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。错 选、多选或未选均无分。) 1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。 A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7) 2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ??的值是( )。 A .111 B. 010 C. 000 D. 101 3.十六路数据选择器的地址输入(选择控制)端有( )个。 A .16 B.2 C.4 D.8 4. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。 A. 1011--0110--1100--1000--0000 B. 1011--0101--0010--0001--0000 C. 1011--1100--1101--1110--1111 D. 1011--1010--1001--1000--0111 5.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( ) 。 A. 11111101 B. 10111111 C. 11110111 D. 11111111 6. 一只四输入端或非门,使其输出为1的输入变量取值组合有( )种。 A .15 B .8 C .7 D .1 7. 随机存取存储器具有( )功能。 A.读/写 B.无读/写 C.只读 D.只写 8.N 个触发器可以构成最大计数长度(进制数)为( )的计数器。 A.N B.2N C.N 2 D.2N 9.某计数器的状态转换图如下, 其计数的容量为( ) A . 八 B. 五 C. 四 D. 三 A B Y 1 Y 2 Y 3 000 001 010 011 100 101 110 111

数字电路试题及答案

数字电路试题 一、单项选择题 1、以下代码中为无权码的为 ( ) A . 8421BCD 码 B . 5421BCD 码 C . 余三码 D .2421BCD 码 2、图示逻辑电路的逻辑式为 ( ) A .F=C B A ++ B .F= C B A ++ C .F=C B A D .F=ABC 3、下列关于异或运算的式子中,不正确的是 ( ) A .0A A =⊕ B . 1A A =⊕ C .A 0A =⊕ D .A 1A =⊕ 4、一个n 变量的逻辑函数应该有 个最小项 ( ) A .n B .n 2 C .n 2 D .2 n 5、若编码器中有50个编码对象,则要求输出二进制代码位数为 位。 ( ) A.5 B.6 C.10 D.50 6、在下列逻辑电路中,不是组合逻辑电路的是 。 ( ) A.译码器 B.编码器 C.全加器 D.寄存器 7、欲使JK 触发器按01 =+n Q 工作,可使JK 触发器的输入端 。 ( ) A.1==K J B.Q J =,Q K = C.Q J =,Q K = D.0=J ,1=K 8、同步时序电路和异步时序电路比较,其差异在于两者 。 ( ) A.没有触发器 B.是否有统一的时钟脉冲控制 C.没有稳定状态 D.输出只与内部状态有关 9、8位移位寄存器,串行输入时经 个脉冲后,8位数码全部移入寄存器中。 ( ) A.1 B.2 C.4 D.8 10、555定时器D R 端不用时,应当 。 ( ) A.接高电平 B.接低电平 C.通过F μ01.0的电容接地 D.通过小于Ω500的电阻接地 二、填空题 1、当传送十进制数5时,在8421奇校验码的校验位上值应为 。 2、(35.625)10=( )2=( )8=( )16 3、用反演律求函数D A D C ABC F ++=的反函数(不用化简)=F 。 4、消除竟争冒险的方法有 、 、 等。 5、触发器有 个稳态,存储8位二进制信息要 个触发器。 1 & A B C F 11

数字电路答案第八章

第八章脉冲产生与整形 在时序电路中,常常需要用到不同幅度、宽度以及具有陡峭边沿的脉冲信号。事实上,数字系统几乎离不开脉冲信号。获取这些脉冲信号的方法通常有两种:直接产生或者利用已有信号变换得到。 本章主要讨论常用的脉冲产生和整形电路的结构、工作原理、性能分析等,常见的脉冲电路有:单稳态触发器、施密特触发器和多谐振荡器。 第一节基本知识、重点与难点 一、基本知识 (一)常用脉冲产生和整形电路 1. 施密特触发器 (1)电路特点 施密特触发器是常用的脉冲变换和脉冲整形电路。电路主要有两个特点:一是施密特触发器是电平型触发电路;二是施密特触发器电压传输特性具有回差特性,或称滞回特性。 输入信号在低电平上升过程中,电路输出状态发生转换时对应的输入电平称为正向阈值电压U T+,输入信号在高电平下降过程中,电路状态转换对应的输入电平称为负向阈值电压U T-,U T+与U T-的差值称为回差电压ΔU T。 (2)电路构成及参数 施密特触发器有多种构成方式,如:门电路构成、集成施密特触发器、555定时器构成。主要电路参数:正向阈值电压U T+、负向阈值电压U T-和回差电压ΔU T。 (3)电路应用 施密特触发器主要应用范围:波形变换、波形整形和幅度鉴别等。 2. 单稳态触发器 (1)电路特点 单稳态触发器特点如下: ①单稳态触发器有稳态和暂稳态两个不同的工作状态; ②在外加触发信号的作用下,触发器可以从稳态翻转到暂稳态,暂稳态维持一段时间,自动返回原稳态; ③暂稳态维持时间的长短取决于电路参数R和C。 (2)电路构成及参数 单稳态触发器有多种构成方式,如:门电路构成的积分型单稳态触发器、门电路构成的微分型单稳态触发器、集成单稳态触发器、555定时器构成的单稳态触发器等。主要电路参数:暂稳态的维持时间t w、恢复时间t re 、分辨时间t d、输出脉冲幅度U m。 (3)电路应用 单稳态触发器主要应用范围:定时、延时、脉冲波形整形等。 3. 多谐振荡器 多谐振荡器是一种自激振荡器,接通电源后,就可以自动产生矩形脉冲,是数字系统中产

第八章 数字逻辑电路基础知识(清华大学出版)

第八章 数字逻辑电路基础知识 1、数字电路处理的信号是数字信号,而数字信号的时间变量是离散的,这种信号也常称为离散时间信号。 2、数字电路的特点: (1)数字信号常用二进制数来表示。 (2)数字电路中,器件常工作在开关状态,即饱和或截止状态。而模拟电路器件工作在放大状态。 (3)数字电路研究的对象是电路输入与输出的逻辑关系,即逻辑功能。而模拟电路研究的对象是电路对输入信号的放大和变换功能。 (4)数字电路的基本单元电路是逻辑门和触发器。(模拟电路单元是放大器) (5)数字电路的分析工具是逻辑代数。 (6)数字信号常用矩形脉冲表示。 脉冲幅度UM ,表示脉冲幅值; 脉冲宽度tW ,表示脉冲持续作用的时间; 周期T ,表示周期性的脉冲信号前后两次 出现的时间间隔; 3、整数转换一般采用“除基取余”法。小数的转换一般采用“乘基取整”法。 4、8421BCD 码与二进制的区别: 8421210001010001110028)()()(== BCD 码转换成二进制数是不直接的。方法是:先转成十进制数,再转成二进制数。反相转换亦是如此。 5、逻辑变量只有两个值,即0和1,0和1并不表示数量的大小,只表示两个对立的逻辑状态。 6、与逻辑运算表达式:F =A ·B =AB 7、或逻辑运算表达式: F =A+B 8、 非逻辑运算表达式: F =ā

9、数字信号常用二进制数来表示。在数字电路中,常用数字1和0表示电平的高和低。 10、当输入A 、B 均为高电平时,输出低电平当A 、B 中至少有一个。 11、TTL 是晶体管——晶体管逻辑电路的简称。输入和输出部分的开关元件均采用三极管(也称双极型晶体管),因此得名TTL 数字集成电路。 12、TTL 与非门的技术参数 : 1.电压传输特性 AB 段截止区 BC 段线性区 CD 段转折区(开门电压ON U ) DE 段饱和区 大于ON U :保证输出低电平。 13、 (1)输出高电平UOH :指逻辑门电路输出处于截止时的输出电平。(典型值UOH=3.6V , UOH (min )=2.4V 。) (2)输出低电平UOL :指逻辑门电路输出处于导通时的输出电平。(典型值UOL =0.3V ,UOL (max )=0.4V 。 (3)输入高电平UIH :由于UIH 是门电路导通时的最小输入电平,故称为开门电平UON 。 (典型值UIH =3.6V , UIH (min )=2.0V 。) (4)输入低电平UIL :保证门电路输出高电平UOH=2.4V 的最大输入电平,又称为关门电平UOFF 。(典型值UIL =0.3V , UIL (max )= 0.8V 。) 14、 扇入与扇出系数 扇入系数NI :指TTL 与非门输入端的个数。例如一个3输入端的与非门,其扇入系数NI =3。 扇出系数:用来衡量逻辑门的负载能力,它表示一个门电路能驱动同类门的最大数目。 扇出系数分为两种情况:(灌电流负载)即输出低电平:) ()(MAX IL MAX OL OL I I N = (拉电流负载)即输出为高电平:) ()(MAX IH MAX OH OH I I N =. 分别计算出低电平高电平时的扇出系数,若OH OL N N ≠,则取较小的作为电路的扇出系数。 15、平均传输延迟时间tPd 是通导延时时间tPHL 和截止延时时间tPLH 的平均值,即 tPd =(tPHL+tPLH )/2 (tPd 越小,工作速度越快) 16、前面介绍的TTL 与非门输出端不能连接在一起,否则将造成逻辑混乱和器件的损坏。(而OC 门输出端可以相连) 17、OC 门电路的特点:用外接电阻RC 代替了原来的T3、D3和R4部分。

(完整版)数字电路自试题3答案

数字电路自测题3答案 一、填空题:(每空1分,共20分) 1.八进制数 (34.2 ) 8 的等值二进制数为 11100.01 ;十进制数 98 的 8421BCD 码为 10011000 。 2.试写出下列图中各门电路的输出分别是什么状态 (高电平、低电平) ?(其中(A )(B )为TTL 门电路,而(C )为CMOS 门电路) (A ) (B ) (C ) Y 1= 02 Y 2= 1 Y 3= 1 3.一个 JK 触发器有 2 个稳态,它可存储 1 位二进制数。 4. 单稳态触发器 有一个稳定状态和一个暂稳状态。 施密特触发器 有两个稳定状态、有两个不同的触发电平,具有回差特性。 多谐振荡器 没有稳定状态,只有两个暂稳态。以上三种电路均可由 555定时器 外接少量阻容元件构成。 5.常用逻辑门电路的真值表如右图所示,则 F 1 、F 2 、F 3 分别属于何种常用逻辑门。F 1 同或 ,F 2 与非门 ,F 3 或非 。 6.OC 门的输出端可并联使用,实现__线与____功能;三态门的输出状态有______0________、 1 、 高阻 三种状态。 7.时序逻辑电路的输出不仅和____输入 ___有关,而且还与___电路原来状态____有关。 二、选择题: (选择一个正确答案填入括号内,每题2分,共20分 ) 1.在四变量卡诺图中,逻辑上不相邻的一组最小项为:( D ) A .m 1 与m 3 B .m 4 与m 6 C .m 5 与m 13 D .m 2 与m 8 2.L=AB+C 的对偶式为:( B ) A B F 1 F 2 F 3 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1 1 1 0 1

数字电路答案大全

浙江省2002年4月高等教育自学考试 数字电路试题 课程代码:02344 一、填空题(每小题2分,共20分) 1.(3AD.08)16=(_________)10=(_____)8 2.CMOS的最基本的逻辑单元是由_________和_________按照互补对称形式连接起来构成 的。 3.按照数据写入方式特点的不同,ROM可分为掩膜ROM,_________,_________。 4.基本RS触发器的约束条件,由与非门构成的为_________,由或非门构成的为________。 5.二值逻辑中,变量的取值不表示_________,而是指______。 6.开关的开通时间t on是指开关由_________状态转换到_____状态所需的时间。 7.描述时序电路的逻辑表达式为_________、_____和驱动方程。 8.施密特触发器具有_________特性,定义为参数△U T=_________。 9.TTL反相器输入接电阻R i>2.5kΩ时,输出电压u0为_________,通常把2.5kΩ电阻称为 _________。 10.用组合电路构成多位二进制数加法器有_________和_____二种类型。 二、单项选择题(在每小题的四个备选答案中,选出一个正确答案,并将正确答案的序号填在 题干的括号内。每小题2分,共20分) 1.若ABCDEFGH为最小项,则它有逻辑相邻项个数为( ) A. 8 B. 82 C. 28 D. 16 2.半导体二极管截止时,外加电压u D为( ) A. <1.4v B. <1v C. <0.7v D. <0.5v 3.如果编码0100表示十进制数4,则此码不可能是( ) A. 8421BCD码 B. 5211BCD码 C. 2421BCD码 D. 余3循环码 4.用或非门构成基本触发器,发生竞态现象时,RS变化为( ) A. 00→11 B. 01→10 C. 11→00 D. 10→01 5.构成移位寄存器不能采用的触发器为( ) A. R-S型 B. J-K型 C. 主从型 D. 同步型 6.555定时器构成的单稳态触发器输出脉宽t w为( ) A.1.3RC B.1.1RC C.0.7RC D.RC 7.A/D转换器中,转换速度最高的为( )转换。 A. 并联比较型 B. 逐次渐近型 C. 双积分型 D. 计数型 8.TTL参数由大到小排列正确的是( ) A. U OHmin、U IHmin、U ILmax、U OLmax B. U IHmin、U OHmin、U OLmax、U ILmax C. U OHmin、U IHmin、U OLmax、U ILmax D. U IHmin、U OHmin、U ILmax、U OLmax 9.4位集成数值比较器至少应有端口数( )个。 A. 18 B. 16 C. 14 D. 12 10.以下PLD中,与、或阵列均可编程的是( )器件。 A. PROM B. PAL C. PLA D. GAL 三、分析题(1、2、3题各5分,4、5、6、7题各6分,共39分) 1.用公式和定理化简

数字电子技术试卷试题答案汇总(完整版)

数字电子技术基础 试题库及答案汇总 一、 填空题(每空1分,共20分) 1、逻辑代数中3种基本运算是 , , 。 2、逻辑代数中三个基本运算规则 , , 。 3、逻辑函数的化简有 , 两种方法。 4、A+B+C= 。 5、TTL 与非门的u I ≤U OFF 时,与非门 ,输出 ,u I ≥U ON 时,与非门 ,输出 。 6、组合逻辑电路没有 功能。 7、竞争冒险的判断方法 , 。 8、触发器它有 稳态。主从RS 触发器的特性方程 , 主从JK 触发器的特性方程 ,D 触发器的特性方程 。 二、 选择题(每题1分,共10分) 1、相同为“0”不同为“1”它的逻辑关系是 ( ) A 、或逻辑 B 、与逻辑 C 、异或逻辑 2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A 3、 A 、Y=A B B 、Y 处于悬浮状态 C 、Y=B A + 4、下列图中的逻辑关系正确的是 ( ) A.Y=B A + B.Y=B A + C.Y=AB 5、下列说法正确的是 ( ) A 、主从JK 触发器没有空翻现象 B 、JK 之间有约束 C 、主从JK 触发器的特性方程是CP 上升沿有效。 6、下列说法正确的是 ( ) A 、同步触发器没有空翻现象 B 、同步触发器能用于组成计数器、移位寄存器。 C 、同步触发器不能用于组成计数器、移位寄存器。 7、下列说法是正确的是 ( ) A 、异步计数器的计数脉冲只加到部分触发器上 B 、异步计数器的计数脉冲同

时加到所有触发器上 C、异步计数器不需要计数脉冲的控制8、下列说法是正确的是() A、施密特触发器的回差电压ΔU=U T+-U T- B、施密特触发器的回差电压越大,电 路的抗干扰能力越弱 C、施密特触发器的回差电压越小,电路的抗干扰能力越强 9、下列说法正确的是() A、多谐振荡器有两个稳态 B、多谐振荡器有一个稳态和一个暂稳态 C、多谐振荡器有两个暂稳态 10、下列说法正确的是() A、555定时器在工作时清零端应接高电平 B、555定时器在工作时清零端应接低电平 C、555定时器没有清零端 三、判断题(每题1分,共10分) 1、A+AB=A+B () 2、当输入9个信号时,需要3位的二进制代码输出。() 3、单稳态触发器它有一个稳态和一个暂稳态。() 4、施密特触发器有两个稳态。() 5、多谐振荡器有两个稳态。() 6、D/A转换器是将模拟量转换成数字量。() 7、A/D转换器是将数字量转换成模拟量。() 8、主从JK触发器在CP=1期间,存在一次性变化。() 9、主从RS触发器在CP=1期间,R、S之间不存在约束。() 10、所有的触发器都存在空翻现象。() 四、化简逻辑函数(每题5分,共10分) 1、 2、Y(A,B,C,)=∑m(0,1,2,3,4,6,8,9,10,11,14) 五、画波形图(每题5分,共10分) 1、 2、 六、设计题(每题10分,共20分)

数字电子技术试卷试题答案汇总(完整版)

数字电子技术试卷试题答案汇总(完整版)

数字电子技术基础试卷试题答案汇总 一、 填空题(每空1分,共20分) 1、逻辑代数中3种基本运算是 , , 。 2、逻辑代数中三个基本运算规 则 , , 。 3、逻辑函数的化简有 , 两种方法。 4、A+B+C= 。 5、TTL 与非门的u I ≤U OFF 时,与非门 ,输出 ,u I ≥U ON 时,与 非门 ,输出 。 6、组合逻辑电路没有 功能。 7、竞争冒险的判断方法 , 。 8、触发器它有 稳态。主从RS 触发器的特性方 程 , 主从JK 触发器的特性方程 ,D 触发器的特性方 程 。 二、 选择题(每题1分,共10分) 1、相同为“0”不同为“1”它的逻辑关系是 ( ) A 、或逻辑 B 、与逻辑 C 、异或逻辑 2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A 3、 A 、Y=A B B 、Y 处于悬浮状态 C 、Y=B A + 4、下列图中的逻辑关系正确的是 ( ) A.Y=B A + B.Y=B A + C.Y=AB 5、下列说法正确的是 ( ) A 、主从JK 触发器没有空翻现象 B 、JK 之间有约束 C 、主从JK 触发器的特性方程是CP 上升沿有效。 6、下列说法正确的是 ( ) A 、同步触发器没有空翻现象 B 、同步触发器能用于组成计数器、移位寄存器。 C 、同步触发器不能用于组成计数器、移位寄存器。 7、下列说法是正确的是 ( ) A 、异步计数器的计数脉冲只加到部分触发器上 B 、异步计数器的计数脉冲 同时加到所有触发器上 C 、异步计数器不需要计数脉冲的控制 8、下列说法是正确的是 ( )

通用数字电路与数字电子技术课后答案第七章.doc

第七章 时序逻辑电路 1.电路如图P7.1所示,列出状态转换表,画出状态转换图和波形图,分析电路功能。 图P7.1 解: (1)写出各级的W.Z 。 D 1=21Q Q ,D 2=Q 1,Z=Q 2CP ( 2 ) 列分析表 ( 3 ) 状态转换表 (4 图7.A1 本电路是同步模3计数器。 2. 已知电路状态转换表如表P7.1所示,输入信号波形如图P7.2所示。若电路的初始状态为Q2Q1 = 00,试画出Q2Q1的波形图(设触发器的下降沿触发)。 Q 2 Q 1 D 2 D 1 Q 2n+1 Q 1n+1 Z 0 0 0 1 0 1 0 0 1 1 0 1 0 0 1 0 0 0 0 0 1 1 1 1 0 1 0 1 Q 2 Q 1 Q 2n+1 Q 1n+1 Z 0 0 0 1 0 0 1 1 0 0 1 0 0 0 1 1 1 1 0 1 CP 表P7.1 X Q 2 Q 1 0 1 00 01 10 11 01/1 10/0 10/0 01/1 11/1 10/0 11/0 00/1 CP X Q 1 0 Q 2 0 Z CP Q 1 0 Q 1 0 Z ( b ) Q 2 Q 1 /Z ( a ) 01/0 11/1 10/1 00/0

解:由状态转换表作出波形图 3. 试分析图P7.3所示电路,作出状态转换表及状态转换图,并作出输入信号为0110111110相应的输出波形(设起始状态Q 2Q 1 = 00 )。 ( a ) ( b ) 解:(1)写W.Z 列分析表 J 1 = XQ 2 J 2 = X Z =12Q Q X K 1 = X K 2 =1Q X ( 2 ) 作出状态转换表及状态转换图 X Q 2 Q 1 0 1 00 01 00/1 00/1 10/1 11/1 X Q 2 Q 1 J 2 K 2 J 1 K 1 Q 2n+1 Q 1n+1 Z 0 0 0 0 1 0 1 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 1 1 0 1 0 1 0 0 1 1 0 0 1 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 1 1 1 0 1 1 1 0 0 1 1 1 1 1 1 0 1 0 1 1 0 CP X 图P7.3 CP X Q 1 0 Q 1 0 Z 图P7.A2 0 /1 0 /1 0 /1 1/1 1/1 0/1 01 11 00

数字电路复习指导部分答案

第一章 逻辑代数基础 数制转换 1. 10= ( )2 =( )8=( )16 2. 16=( )2=( )10 3. 2=( )8=( )10 写出下列数的八位二进制数的原码、反码、补码 原码,就是用最高位表示数符(0表示正数、1表示负数)。正数,原码=反码=补码;负数,反码:除符号位以外,对原码逐位取反;补码:反码+1 1.(-35)10= ( )原码= ()反码=()补码 2. (+35)10 = (00100011 )原码= (00100011)反码=(00100011)补码 3. (-110101)2 = ( )原码= ()反码=()补码 4. (+110101)2 = (00110101 )原码= (00110101)反码=(00110101)补码 5. (-17)8=( )原码= ()反码=()补码 . 将下列三位BCD 码转换为十进制数 根据BCD 码的编码规则,四位一组展成对应的十进制数。 1. ()余3码 = (263)10 2. ()8421码= (596)10 分别求下列函数的对偶式Y ‘ 和反函数Y 1. D C B A Y ++=)( D C B A Y ?+?=)(' D C B A Y ?+?=)( 2. D A C B A Y ++= )()('D A C B A Y +??+= D C B A Y ?+?=)( 求下列函数的与非-与非式。 1. B A AB Y += B A AB Y ?= 将下列函数展成最小项之和的标准形式 1. Y=C B B A ?+? C B A C B A C B A C B A C B A C B A C B A A A C B C C B A Y ??+??+??=??+??+??+??=+??++??=)()( 2. Q R S Y +=

数字电路试卷及答案

一.选择题 1十进制数3.625的二进制数和8421BCD 码分别为(D ) A 、11.11和11.001 B 、11.101和11.101 C 、11.01和11.011000100101 D 、11.101和0011.011000100101 2、逻辑函数F1、F2、F3的卡诺图如图所示,他们之间的逻辑关系是(B ) A 、F3=F 1·F2 B 、F3=F1+F2 C 、F2=F1·F3 D 、F2=F1+F3 00 01 11 10 0 1 1 1 1 1 F1 F2 F3 3 、和TTL 电路相比,CMOS 电路最突出的有点在于(C ) A 、可靠性高 B 、抗干扰能力强 C 、功耗低 D 、速度快 4、用1K ×4的DRAM 设计4K ×8位的存储器的系统需要的芯片数和地址线的根数是(C ) A 、16片 10根 B 、8片 10根 C 、8片 12根 D 、16片 12根 5、在图2中用555定时器组成的施密特触发电路中,它的回差电压等于(A ) A 、2V B 、3V C 、 4V D 、5V 图2 图3 6、为将D 触发器转换为T 触发器,图3所示电路的虚线框内应是(D ) A 、或非门 B 、与非门 C 、异或门 D 、同或门 7、在下列逻辑部件中,不属于组合逻辑部件的是(A ) A .寄存器 B 、编码器 C 、全加器 D 、译码器 8、某10位D/A 转换器,当输入为D=010*******B 时,输出电压为1.6V 。当输入D=1000010000B 时,输出电压为(B ) A 、3.15V B 、3.30V C 、3.60V D 、都不是 二.填空题 1、逻辑函数F=A ·(B+C )·1的反函数F =_____0+?+C B A ___________ 2、四选一数据选择器,AB 为地址信号,D 0=D 3=1,D 1=C ,D 2=c ,当AB=10时,输出F=__C__ 3、将模拟信号转化为数字信号,需要采用A/D 转换器。实现A/D 转换一般要经过采样、保持、量化和编码等4个过程。 00 01 11 10 0 1 1 1 1 00 01 11 10 0 1 1 1 1 1 1