Allegro---导出坐标文件

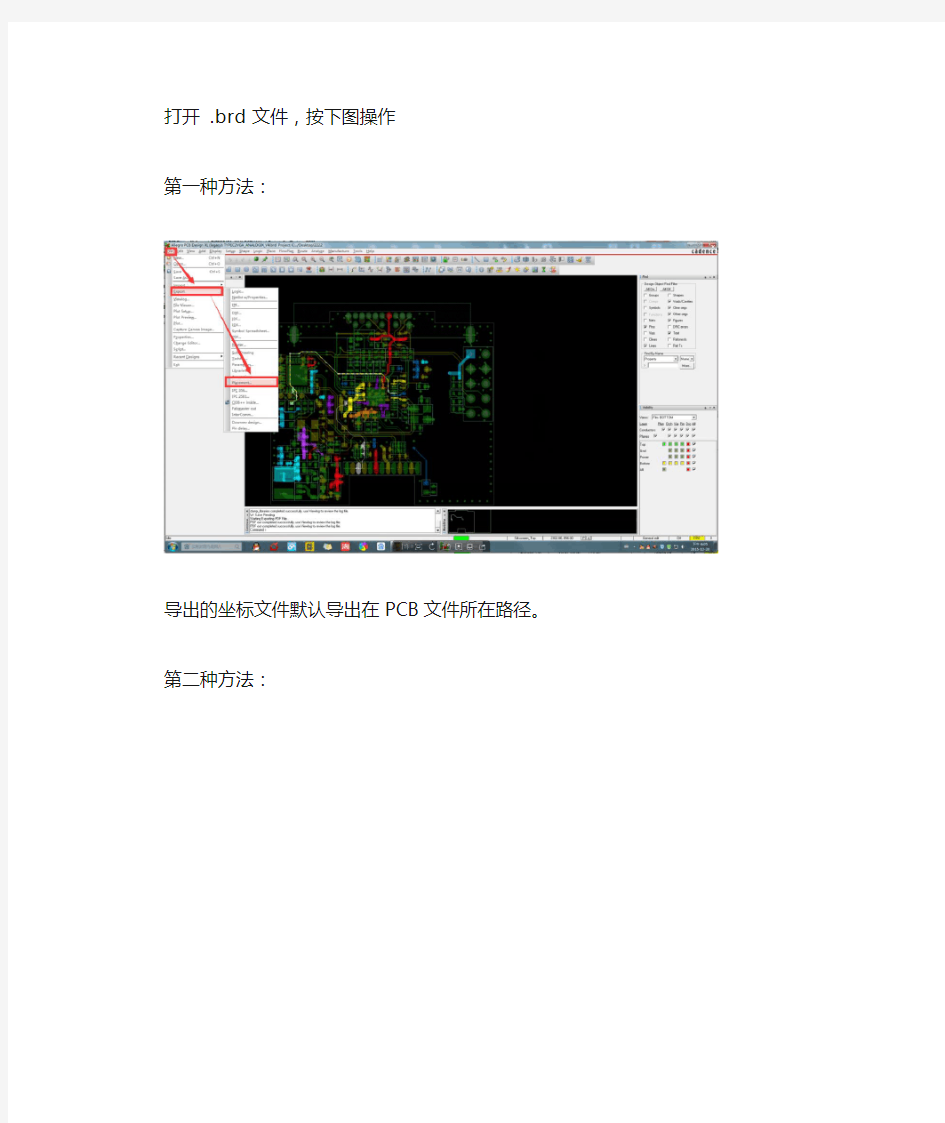

打开.brd 文件,按下图操作

第一种方法:

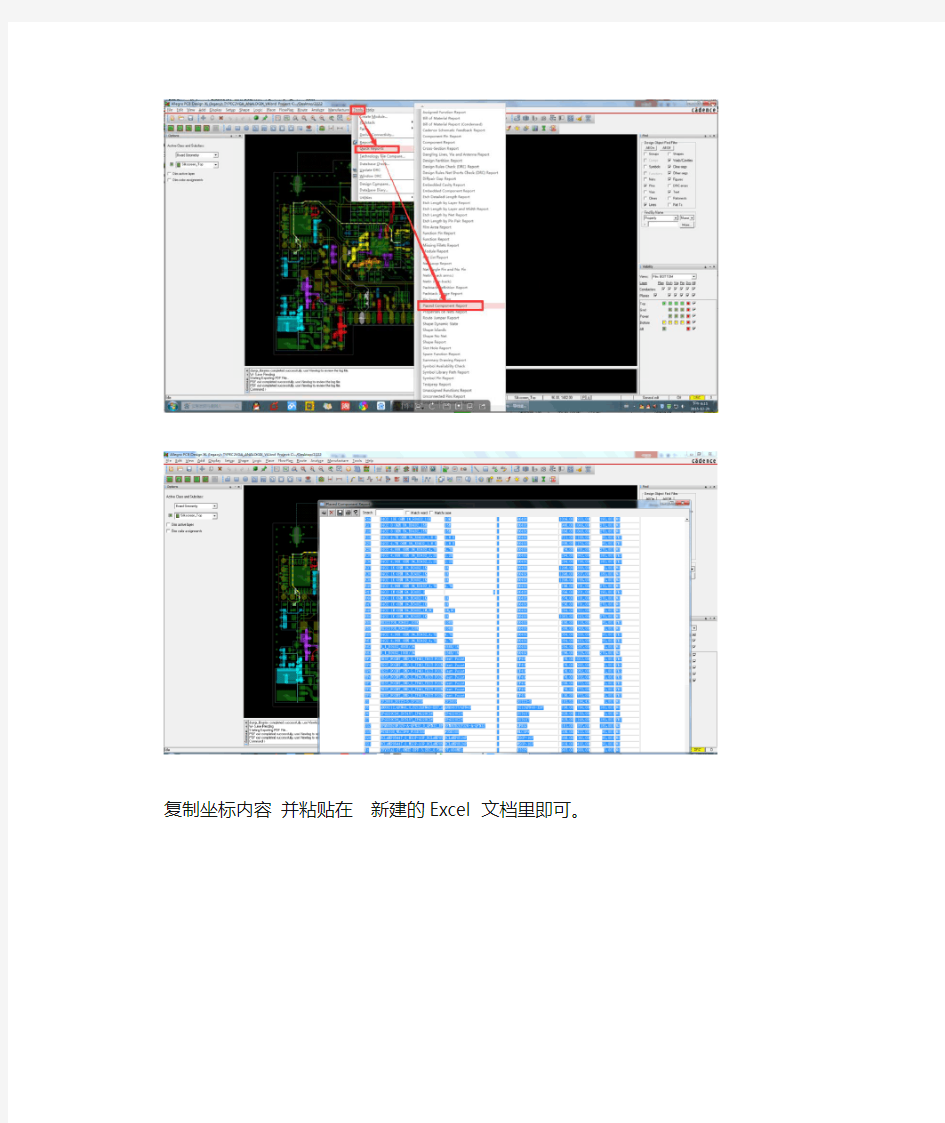

导出的坐标文件默认导出在PCB文件所在路径。第二种方法:

复制坐标内容并粘贴在新建的Excel 文档里即可。

OrCAD Capture CIS Cadence原理图绘制

OrCADCaptureCIS(Cadence原理图绘制) 1,打开软件........................................ 2,设置标题栏..................................... 3,创建工程文件................................... 4,设置颜色........................................ 2.制作原理库.......................................... 1,创建元件库...................................... 2,修改元件库位置,新建原理图封库................. 3,原理封装库的操作............................... 3.绘制原理图.......................................... 1.加入元件库,放置元件............................ 2.原理图的操作.................................... 3.browse命令的使用技巧 ........................... 4.元件的替换与更新................................ 4.导出网表............................................ 1.原理图器件序号修改.............................. 2.原理图规则检查.................................. 3.显示DRC错误信息................................ 4.创建网表........................................ 5.生成元件清单(.BOM)..................................

用AD6、AD9画完PCB生成gerber文件详细说明

用AD6、AD9画完PCB生成gerber文件详细说明 (2012-03-14 22:30:32) 转载▼ 什么是gerber文件不再说明。很多工程师将完成的PCB图直 接交由制板厂制作,但是有时候制板厂转换出来的gerber文件 不是我们想要的。例如我们用的AD作出的图,但是有的厂只 用protel,那转换出来的带有汉字的gerber文件可能就会有错误,或者我们在设计的时候将元件的参数都定义在了PCB文件中,但是我们不想让这些参数都出现在PCB成品上,如果不加说明,有的制板厂可能会将这些参数留在了PCB成品上,为避免这些不必要的麻烦,我们将PCB直接转换成gerber文件交给制板 厂就解决了。 下面以AD9.4为例,AD6.9一样,其他AD版本未测试: 一、1、画好PCB文件,在PCB文件环境中,点击左上角文件(Files)->制造输出(Fabrication Outputs)->Gerber Files,进入Gerber设置界面。

如上图,在第一常规/概要中,单位选择英寸,格式为2:5。(2:5精度较高) 2、设置“层”:如下图

在“层”选项中,将“包括未连接的中间层焊盘”打√。在“画线层”下拉选项中选择“所有使用的”,这时我们在作图时使用的图层都会被打√。在“映射层”下拉选项中选择"All Off",右边的机械层都不要选。 3、设置“光圈”和“高级”。“光圈”中将“嵌入的光圈(RS274X)”打上√即可。在“高级”里面,选中“Suppress leading zeroes(抑制前导零字符)”,其他设置不变。点击“确定”,第一次输出,至此第一大步完成。(第一步生成的.cam可不用保存)

Cadence原理图绘制流程

第一章设计流程 传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。设计人员只需要了解本阶段的基本知识及设计方法即可。但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。 细化并调整以上原理图设计阶段的流 程,并结合我们的实际情况,原理图设计 阶段应该包括如下几个过程: 1、 阅读相关资料和器件手册 在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。 2、 选择器件并开始建库 在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。 3、 确认器件资料并完成详细设计框图 为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。 4、 编写相关文档 这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。 5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。 6、使用Concept-HDL绘制原理图 7、检查原理图及相关文档确保其一致性。 以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

PADS生成GERBER文件步骤及CAM350的简单使用

PADS生成GERBER文件步骤及CAM350的简单使用 PCB画好后,我们需要输出光绘文件交给制版厂家.由此,输出光绘文件的重要性就显出来了. 首先来看一下每个powerpcb 文件应输出多少张gerber文件。输出的总数为n+8 张。其中n 为板子的层数(例如4 层板,那么 n=4),这n张图为板子每层的连线图;另外8张包括2张丝印图(silkscreen top/bottom),2张阻焊图(solder mask top/bottom),2张助焊图(paste mask top/bottom),2 张钻孔图(drill/Nc drill)。 先复习一下介绍各层的定义吧,哈哈 (1)顶层(Top Layer),也称元件层,主要用来放置元器件,对于比层板和多层板可以用来布线. (2)中间层(Mid Layer),最多可有30层,在多层板中用于布信号线. (3)底层(Bootom Layer),也称焊接层,主要用于布线及焊接,有时也可放置元器件. (4)顶部丝印层(Top Overlayer),用于标注元器件的投影轮廓、元器件的标号、标称值或型号及各种 注释字符。 (5)底部丝印层(Bottom Overlayer),与顶部丝印层作用相同,如果各种标注在顶部丝印层都含有, 那么在底部丝印层就不需要了。 (6)内部电源接地层(Internal Planes) (7)阻焊层(Solder Mask-焊接面),有顶部阻焊层(Top solder Mask)和底部阻焊层(Bottom Solder mask)两层,是Protel PCB对应于电路板文件中的焊盘和过孔数据自动生成的板层,主要用于铺设阻焊漆.本板层采用负片输出,所以板层上显示的焊盘和过孔部分代表电路板上不铺阻焊漆的区域,也就是可以进行焊接的部分.(所谓阻焊顾名思义就是不让上锡,阻焊漆就是绿油啦)(8)防锡膏层(Past Mask-面焊面),有顶部防锡膏层(Top Past Mask)和底部防锡膏层(Bottom Past mask)两层,它是过焊炉时用来对应SMD元件焊点的,也是负片形式输出.板层上显示的焊盘和过孔部分代表钢板上挖空的部分,对应电路板上要刷锡膏的地方,也就是进行焊接的部分。 (9)Drill (10)N C Drill (11)机械层(Mechanical Layers), (12)禁止布线层(Keep Ou Layer) (11)多层(MultiLayer) (13)(Connect)(DRC Errors)(Pad holes)(Via Holes)(Visible Grid1)(visible Grid2) 我们要考虑的就是1-10这几个.值得一提的是solder表示是否阻焊,就是PCB板上是否露铜;paste 是开钢网用的,是否开钢网孔.所以画板子时两层都要画,solder是为了PCB板上没有绿油覆盖(露铜),paste上是为了钢网开孔,可以刷上锡膏. 再来讲讲各显示项目. Board outline(板框),在设置每层的Layer时,将Board Outline选上. Pads(焊盘).Connections(鼠线).Vias(导通孔).Parts-Top(顶层元器件).Tracks(电气走线)Parts-Botm(底层元器件)Copper(导体铜箔)Part Refs(元器件排序标注)Lines(二维线)Part Type(元器件型号标注)Text(字符)Outlines(外框线) 准备工作: 1、重新设定外形左下角为原点 在 Setup 菜单中选择 Set Origin,输入板框外形左下角坐标,重新设定原点,并将外形尺寸(长宽)设为整数,单位mm ,特殊情况可设到小数点后一位。 2、检查字符丝印是否上焊盘、字体太小或太大、字符反字符等现象,如果有上述的现象,可先在PCB 中对字符进行移动、放大或缩小、镜像或旋转、字符线宽等操作。

Allegro如何生成光绘文件

主题:Allegro如何生成光绘文件 Allegro如何生成光绘文件: PCB 检查没有错误后,在 Allegro 的主菜单 Manufacture 下生成光绘文件(如下图): 光绘文件包括下面的文件: 1.光圈表及光绘格式文件 art_aper.txt Aperture and artwork format 2.光绘参数文件 art_param.txt Aperture parameter text 3.元件面布线层 Gerber 文件 top.art Top(comp.)side artwork 4.内部层布线层 Gerber 文件 inner.art Inner layer artwork 5.内部电源层 Gerber 文件 vcc.art Vcc layer artwork 6.内部地层 Gerber 文件 gnd.art Gnd layer artwork 7.阻焊面布线层 Gerber 文件 bot.art Bottom(solder) side artwork 8.元件面丝印层 Gerber 文件 topsilk.art Top(comp.)side silkscreen artwork 9.阻焊面丝印层 Gerber文件 botsilk.art Bottom(solder) side silkscreen artwork 10.元件面阻焊层 Gerber 文件 topsold.art Top(comp.) side solder mask artwork 11.阻焊面阻焊层 Gerber 文件 botsold.art Bottom(solder) side solder mask artwork 12..钻孔和尺寸标注文件 drill.art 13.钻带文件 ncdrill1.tap 注意: 有的公司还选了下面的两层,但我们公司不选: (表面贴)元件面焊接层 Gerber 文件 toppast.art Top(comp.) side paste mask artwork (表面贴) 阻焊面焊接层 Gerber 文件 botpast.art Bottom side paste mask artwork Allegro如何在 ARTWORK中加入所需的层 下面举例讲述如何在光绘文件中加入 SILK-TOP 层.

Cadence Capture输出带属性的PDF原理图设置步骤

Cadence Capture 输出带属性的PDF 原理图设置步骤 作者:Myedacn 2016-01-06 1.准备工作 需要安装两个工具,一个是虚拟打印机,一个是脚本运行工具 1.1虚拟打印机安装 官方推荐Adobe Acrobat ,但是这个是需要购买授权的,所以推荐安装免费开源的工具PDFCreator ,可以从网上下载到该工具。https://www.wendangku.net/doc/0418623215.html,/可以下载到最新版本的软件。 按照提示进行安装,安装完成后,可以看到打印机列表里面多了一个虚拟打印机 记住这个打印机的名称,后面会用到。1.2安装脚本运行工具基于Adobe 、PostScript 及可移植文档格式(PDF )的页面描述语言等而编译成的免费软件GhostScript 可以在官网下载到最新版本https://www.wendangku.net/doc/0418623215.html,/按照提示进行安装,安装完成后记住安装路径,比如:C:\Program Files (x86)\gs\gs9.09\bin\gswin32c.exe 后面会用到。2.修改配置文件 打开Cadence Capture 安装目录,比如: C:\Cadence\SPB_16.6\tools\capture\tclscripts\capUtils 找到文件:capPdfUtil.tcl 用文本编辑器打开此文件: 找到以下位置进行修改: set ::capPdfUtil::mPSDriver "PDFCreator " 把默认的Adobe 打印机修改为PDFCreator 修改打印机安装程序位置,红色字体位置所示 set ::capPdfUtil::mPSToPDFConverterList { { "PDFCreator " {{C:\Program Files\PDFCreator\PDFCreator.exe }/N /q /o M y e d a c n 出品

Allegro16.6光绘生成步骤

一、PCB后处理 修改丝印 Ref丝印线宽为0,而且丝印位置需要手动调整。首先根据PCB板大小,统一修改丝印尺寸和线宽,然后调整Ref位置,不要压到焊盘、过孔和其他丝印。 导入制版说明 首先再器件库Format文件夹中打开Manufacture.drc制版说明格式元件,根据PCB加工要求及阻抗要求,修改各项参数。打开PCB,单击Place Manual,如下图 然后选择Format symbol,将Manufacture格式元件添加到PCB中(制版说明文档再Board Geometry>Dimension层)。 尺寸标注 菜单栏Manufacture>DimensionEnvironment,右键弹出菜单,选择Parameters,在弹出的dimensioning parameters对话框中设置好各个参数要求(见书P226),然后右键选择标注命令。

二、光绘生成 底片参数设置 线宽为0的线在Undefined line width中可以统一定义线宽(设置为0.127即可),若是负片则按上图选Negative,Format设置为5:5(底片精度要大于当前设计文件精度,否则在加工的时候读取会精度缺失而报错),其余按上图设置。关闭后,自动在工作目录生成art_param.txt 光绘参数文件。

底片控制文件 除了TOP、Internal、BOT层默认存在,其他层都可以在Color dialog对话框中先关闭所有层,再添加以下必须层,然后新建底片,就可以直接将所需层添加到底片中。 TOP层底片 Board Geometry/OutLine VIA Class/TOP PIN/TOP ETCH/TOP Internal Board Geometry/OutLine VIA Class/Internal PIN/Internal ETCH/Internal Bottom Board Geometry/OutLine VIA Class/Bottom PIN/Bottom ETCH/Bottom SolderMask TOP Board Geometry/OutLine Board Geometry/SolderMask_TOP(ZTE板子代码) //Board Geometry/阻焊开窗层(如ZTE屏蔽筋、标识,可不用) Package Geometry/SolderMask_TOP(ZTE0.15mm焊接对齐用开窗线或热焊盘等) PIN/SolderMask_TOP VIA CLASS/SolderMask_TOP SolderMask Bottom Board Geometry/OutLine Board Geometry/SolderMask_Bottom //Board Geometry/阻焊开窗层 Package Geometry/SolderMask_Bottom PIN/SolderMask_Bottom VIA CLASS/SolderMask_Bottom PasteMask TOP Board Geometry/OutLine Package Geometry/PasteMask_TOP PIN/PasteMask_TOP //Board Geometry/屏蔽筋开窗层 PasteMask Bottom Board Geometry/OutLine Package Geometry/PasteMask_Bottom PIN/PasteMask_Bottom //Board Geometry/屏蔽筋开窗层 SilkScreen TOP

如何将altium designer的原理图和PCB转入cadence里

说明: 1)本教程适用于将altium designer的原理图和PCB转入cadence(分别对应capture CIS和allegro)里。对于protel 99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altium designer Summer 08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altium designer导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altium designer导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1. 原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》save projec as,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE 的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4 随后就可以使用新版本的cadence的capture CIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2. PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADS Projects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb

Allegro如何生成光绘文件

Allegro如何生成光绘文件 Allegro如何生成光绘文件: PCB 检查没有错误后,在Allegro 的主菜单Manufacture 下生成光绘文件(如下图): 光绘文件包括下面的文件: 1.光圈表及光绘格式文件art_aper.txt Aperture and artwork format 2.光绘参数文件art_param.txt Aperture parameter text 3.元件面布线层Gerber 文件top.art Top(comp.)side artwork 4.内部层布线层Gerber 文件inner.art Inner layer artwork 5.内部电源层Gerber 文件vcc.art Vcc layer artwork 6.内部地层Gerber 文件gnd.art Gnd layer artwork 7.阻焊面布线层Gerber 文件bot.art Bottom(solder) side artwork 8.元件面丝印层Gerber 文件topsilk.art Top(comp.)side silkscreen artwork 9.阻焊面丝印层Gerber文件botsilk.art Bottom(solder) side silkscreen artwork 10.元件面阻焊层Gerber 文件topsold.art Top(comp.) side solder mask artwork 11.阻焊面阻焊层Gerber 文件botsold.art Bottom(solder) side solder mask artwork 12..钻孔和尺寸标注文件drill.art 13.钻带文件ncdrill1.tap 注意: 有的公司还选了下面的两层,但我们公司不选:

PCB设计---AD封装库转Allegro封装库操作

AD封装库转Allegro封装库操作 此转换过程需要用到3种设计软件:Altium Designer(AD)、Pads、Allegro; 整个转换过程,完成封装库转换并生成可用的allegro封装库,共需要4三个阶段: 1.AD封装转成Pads文件; 2.在Pads文件中封装转换成ACSII文件; 3.在Allegro软件中,将Pads文件转换成Allegro文件; 4.导出Allegro库,进行编辑优化; AD封装转成Pads文件 1.在AD中新建封装库,或者从现有的PCB中导出封装库文件 从AD的PCB中导出封装库操作:打开PCB文件:design---make pcb library,生成lib文件

2.打开Altium,新建PCB文件并和PCBLIB文件保存在同一路径下; 3.在PCB中放入需要转换的封装 a)添加库路径:place-component…

b)手动在PCB文件中放置需要转换的封装库:选中对应封装,在PCB中空白区域点 击放置;点击鼠标右键可以结束当前放置,在弹出界面可以进行下一个封装放置或者点击cancel结束封装库放置;

4.将放入封装的PCB另存为4.0版本;至此,AD软件中操作完成; 在Pads文件中封装转换成ACSii文件 1.打开Pads layout,导入4.0版本的AD文件;注意文件类型选择,见下图:

2.打开的文件导出ASC文件,版本为5.0,设置见下图: 点击确定后,生成xxx.asc文件;Pads操作至此完成。

Pads文件转换成Allegro文件 1.新建brd文件,并设置库路径; 2.导入Pads生成的asc文件,操作如下: Files-→Import-→CAD Translators-→PADS…

Protel99se如何生成gerber文件

这几天工作中遇到制作gerber的问题,确实让我郁闷了一番,为了方便大家,不要再受其苦,特将这一过程写成文档供有这方面需要的同仁们参考. 1protel99se打开要生成gerber的pcb设计文档,在file->CAM Manager然后出现Output Wizard点击next 2按照下图选择gerber,然后点击next

3直至出现下图,分别选中单位millimeter和比例4:4再次点击next(其实,选择单位是无所谓的,但要与NC drill的一致才行。4:4表示小数点前面四位有效数字,小数点后4位有效数字) 在下图中选择要输出的gerber层,一路点击next

5点击tools菜单的proference出现下图,在export cam outputs栏选择要输出gerber文件的路径。然后ok 6点击tools菜单generrate CAM Files,生成gerber文件。 7生成后的gerber文件可以用CAM350软件打开。

到此,先别得意…….哈哈。。。做完以上步骤,其实漏掉了一个最重要的东西,那就是钻孔层,那么下面介绍如何产生钻孔层文件。如下图右击鼠标,选中Insert NC Drill…然后回车 8在下图中选择Units单位为milmeter,Format(格式)为4:4,然后点击ok (其实,选择单位是无所谓的,但要与NC drill的一致才行。4:4表示小数点前面四位有效数字,小数点后4位有效数字)。

10在导入的gerber文件中添加钻孔属性表,在protel的plce-〉String,此时按tab键,在出现的text文本框中点击下拉箭头,在出现的序列中选择.Legend.点击OK,将其放在pcb板框边就可以了。 9直接F9或者在tools菜单下选择Generate CAM file就会在指定的目录中加入钻孔文件。如下图。

ad绘制元件封装操作总结

聿发光二极管:颜色有红、黄、绿、蓝之分,亮度分普亮、高亮、超亮三个等级,常用的封装形式有三类:0805、1206、1210 羆二极管:根据所承受电流的的限度,封装形式大致分为两类,小电流型(如1N4148)封装为1206,大电流型(如IN4007)暂没有具体封装形式,只能给出具体尺寸:5.5X3X0.5 螁电容:可分为无极性和有极性两类,无极性电容下述两类封装最为常见,即0805、0603;而有极性电容也就是我们平时所称的电解电容,一般我们平时用的最多的为铝电解电容,由于其电解质为铝,所以其温度稳定性以及精度都不是很高,而贴片元件由于其紧贴电路版,所以要求温度稳定性要高,所以贴片电容以钽电容为多,根据其耐压不同,贴片电容又可分为A、B、C、D四个系列,具体分类如下: 荿类型封装形式耐压 腿A 3216 10V 膃B 3528 16V 薃C 6032 25V 膈D 7343 35V 艿拨码开关、晶振:等在市场都可以找到不同规格的贴片封装,其性能价格会根据他们的引脚镀层、标称频率以及段位相关联。 薄电阻:和无极性电容相仿,最为常见的有0805、0603两类,不同的是,她可以以排阻的身份出现,四位、八位都有,具体封装样式可参照MD16仿真版,也可以到设计所内部PCB库查询。 羁注: 膁A\B\C\D四类型的封装形式则为其具体尺寸,标注形式为LXSXH 莈1210具体尺寸与电解电容B类3528类型相同 羅0805具体尺寸:2.0X1.25X0.5 蚃1206具体尺寸:3.0X1.50X0.5 羀***规则 莈印制电路板(PCB)是电子产品中电路元件和器件的支撑件。它提供电路元件和器件之间的电气连接。随着电子技术的飞速发展,PCB的密度越来越高。PCB设计的好坏对抗干扰能力影响很大。实践证明,即使电路原理图设计正确,印制电路板设计不当,也会对电子产品的可靠性产生不利影响。例如,如果印制板两条细平行线靠得很近,则会形成信号波形的延迟,在传输线的终端形成反射噪声。因此,在设计印制电路板的时候,应注意采用正确的方法,遵守PCB设计的一般原则,并应符合抗干扰设计的要求。 一、PCB设计的一般原则

CADENCE从原理图到PCB步骤(精)

CADENCE从原理图到PCB步骤 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option with capture,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘; 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate (注解),在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。 6)一些细节: 画原理图时的放大和缩小分别是按键“i”(Zoom In)和“o”(Zoom Out)和Protel有所区别;在创建元件封装的时候,除了GND可以同名以外,不能有其他同名的管脚,否者报错,不过貌似报错也没有影响,因为打开OrCAD自带的元件库时(比如Xilinx的FPGA),也有除GND外的同名管脚;添加网络标号的快捷键是“n”,不过在OrCAD中网络标号无法复制,记得Protel中是可以通过复制已有的网络标号来添加新的网络标号的。

Protel DXP2004生成Gerber文件和钻孔文件的一般步骤

Protel DXP2004生成Gerber文件和钻孔文件的一般步骤 这里针对的是一般情况下、没有盲孔的板子。 1、首先是生成Gerber Files: 打开PCB文件,在DXP2004中选择菜单File-Fabrication Outputs-Gerber Files,进入生成Gerber 文件的设置对话框。 ·单位选择? 英寸,格式选择2:5 这样可以支持的精度会高一些(这些也可以先跟制板厂联系一下确认)·在Layers中,选中“include unconnected mid-layer pads”,同时Plot Layers选择All Used Mirror Layers全都不选,然后在右侧选中相关的机械层。 ·Drill Drawing中什么都不选,保持默认即可。 ·在Apertures中,选择Embedded apertures(RS274X) ·Advanced中其余项都保持默认,主要是选择“Suppress leading zeroes”(此项也可与制板厂联系确认) ·点击确认,会自动生成Gerber文件,此时生成一个cam文件,此文件可以不保存, 因为我们要交制板厂的文件已经在项目的目录里面建了个子目录叫作“Project Outputs for xxx”, 各个层的gerber都存在里面了。 2、然后是生成NC Drill Files: ·同样,在DXP2004中选择菜单File-Fabrication Outputs-NC Drill Files,进入生成NC Drill 文件的设置对话框. 此处的选择要跟前面Gerber文件中的保持一致:英寸-2:5-Suppress leading zeroes 其它选项保持默认,点击OK 确认一下随后弹出的钻孔数据对话框,然后就会自动生成NC Drill Files了, 同样的,生成的文件会在那个子目录里,而CAM文件可以不用保存 3、将含有以上生成的文件的那个子目录“Project Outputs for xxx”,打个包,就可以发给制板厂了,呵呵。 1)前提是PCB已经画好,进入导Gerber文件的菜单:File-Fabrication Outputs-Gerber Files )单位和精度设置:* E! c! L ^: d 8 ~$ W$ X. S, L' n3 v5 n0 d& A0 s 2 ,格“英寸”选择“一般”里面,“单位”在当然,式选择2:5 ,这个尺寸精

出光绘文件

Allegro如何生成光绘文件: PCB 检查没有错误后,在Allegro 的主菜单Manufacture 下生成光绘文件(如下图): 光绘文件包括下面的文件: 1.光圈表及光绘格式文件art_aper.txt Aperture and artwork format 2.光绘参数文件art_param.txt Aperture parameter text 3.元件面布线层Gerber 文件top.art Top(comp.)side artwork 4.内部层布线层Gerber 文件inner.art Inner layer artwork 5.内部电源层Gerber 文件vcc.art Vcc layer artwork 6.内部地层Gerber 文件gnd.art Gnd layer artwork 7.阻焊面布线层Gerber 文件bot.art Bottom(solder) side artwork 8.元件面丝印层Gerber 文件topsilk.art Top(comp.)side silkscreen artwork 9.阻焊面丝印层Gerber文件botsilk.art Bottom(solder) side silkscreen artwork 10.元件面阻焊层Gerber 文件topsold.art Top(comp.) side solder mask artwork 11.阻焊面阻焊层Gerber 文件botsold.art Bottom(solder) side solder mask artwork 12..钻孔和尺寸标注文件drill.art 13.钻带文件ncdrill1.tap 注意: 有的公司还选了下面的两层,但我们公司不选: (表面贴)元件面焊接层Gerber 文件toppast.art Top(comp.) side paste mask artwork (表面贴) 阻焊面焊接层Gerber 文件botpast.art Bottom side paste mask artwork Allegro如何在ARTWORK中加入所需的层 下面举例讲述如何在光绘文件中加入SILK-TOP 层. 1. 在ALLEGRO 中,选取MANUFACTURE-ARTWORK 命令:将光标移到展开窗口右边的”+”号,按右键,如图:

AD6.9中提取元件封装的几种方法

AD6.9中提取元件封装的几种方法 在电路板设计中,封装是否准确,合适美观对最终设计结果有很大影响。对于自制元件,如何快速准确地绘制封装呢?当然最简单的方法是利用查找功能找到已有的或者类似的封装提取出来稍作修改使用,其次是利用工具中的元件封装向导,根据图示的尺寸输入相应数值自动生成封装。提取封装的操作主要有以下几种办法。 1。找到封装所在的库文件,打开后从Pcb library面板中选中相应n个封装, 右键菜单选复制,然后打开自己的封装库,点开Pcb library面板执行右键菜单中的Paste n Components粘贴n个封装,当然也可以用Ctrl + C,Ctrl + V来 复制粘贴,不过这样偶尔会“失灵”。对于软件自带的集成元件库,在打开时候会提示要进行什么操作,选择提取资源就可以打开为一个原理图库和一个封装库来使用了,复制粘贴的办法如上。 2。其实封装也在于积累,在平时,看到别人电路板中有漂亮精巧的封装,也可 以提取出来为我所用。执行设计菜单中的生成PCB库命令,软件会自动提取电路板中的封装并生成一个元件库,然后要做的和上面的一样了,找到你想要的封装然后复制粘贴保存。 3。从PCB中提取单个封装。先生成PCB封装库再复制封装的办法虽然能将好的 封装一网打尽,可是大多数时候会比较麻烦,查找不便,更多时候我们仅仅是需要使用其中的一两个封装。这时候就可以在PCB中选中要提取封装的元件,复制,切换到自己的封装库,点开Pcb library面板粘贴或者新建一个封装后粘贴到封装中,这两种操作的不同之处是前一种可以保留封装的相关信息,如描述、高度等,而后一种却只是保留了封装。其实这样复制粘贴还有一个妙用,自己做的Logo、签名之类也可以用这样的方法制作成一个封装保存,在以后的使用中,更加方便。我之前都是用bmp2pcb那个小软件生成Logo,保存在一个PCB文件中,每次需要用的时候打开复制粘贴,因为其中的元素是散的每次都要全部选中了才能挪动或者复制粘贴,使用起来比较麻烦。当然,Logo的制作流程也比较复杂,有空再总结吧。

第08步 Allegro检查及生成光绘文件的方法

Allegro检查及生成光绘文件的方法 1.拼版 (1)选择某一块板,点击Tools .. Create Module… 然后点选一块区域,输入0点坐标,一般选取板的左下边缘坐标,然后生成.mdd文件。(2)将另一块板另存,然后直接导入前面生成的.mdd文件即可 (要先选中Library)

然后放入即可(最好用坐标导入) (3)删除原来板的Outline,重新在两个板的外边缘加一个整体的Outline(Board Geometry)在需要切开的地方加入Dimension(Board Geometry) 最好将板做成如下图的形状 2.添加接地过孔 ◆在PCB空隙处添加接地过孔,尽量使每层地填充均匀。 ◆沿重要线两侧添加接地过孔,保证屏蔽效果。 ◆沿PCB板边添加接地过孔,保证ESD效果。 3.添加丝印 ◆丝印线宽最细为5 mil。 ◆丝印文字高度最小为30 mil。 ◆BOTTOM面文字做镜像。 ◆添加必要的丝印说明,如板子名字(含版本)、日期、文字说明、Logo图片等。 ◆所有丝印内容不得覆盖焊盘及裸露的铜箔,过孔尽量也不要覆盖。 ◆调整丝印及文字 在PCB设计中遇到了元件文字的问题,看下图:

是不是相当的乱,从字面上可以看出好多叠加的文字,到底是怎么回事呢?我们先从元件的封装说起,我们使用Allegro在制作元件封装时,都是通过File-->New,然后在Drawing Type中选择Package Symbols创建的,这时的Allegro 菜单中会多一个Layout,而平时没有这个菜单,他专门负责上图中的文字。 在上图中的Layout中可以看到在Labels子菜单中还有六个选项: ?RefDes这个是为了在放置时产生元件序号用的,是上图的C45。 ?Device这个是元件的名称,也就是上图中那一串非常小的字母。 ?Value这个是元件的真实值,也就是上图中104和105。 ?Tolerance是容许的误差值,一般不用。 ?Part Number是零件编号,一般不用。 那我们明白了PCB中的这些元件的文字了,假如出现这种情况: 是不是很乱啊,首先是看到那个蓝色的Ref Des太大了,都与元件重叠在一起了,怎么办?改变字体大小。 Setup->Text Sizes Text Blk:字体编号 Photo Width:配置线宽 Width,Height:配置字体大小 改变字体大小:Edit->Change,然后在右边控制面板Find Tab里只选Text(只改变字体) 然后在右边控制面板Options Tab里Line Width添线的宽度和Text Block里选字体的大小。一定要注意Options 标签中的Class选择Ref Des,并且Subclass 要设置如下:

如何将altiumdesigner的原理图和PCB转入cadence里

说明: 1)本教程适用于将altiumdesigner的原理图和PCB转入cadence(分别对应captureCIS和allegro)里。对于protel99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altiumdesignerSummer08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altiumdesigner导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altiumdesigner导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1.原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》saveprojecas,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4随后就可以使用新版本的cadence的captureCIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2.PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADSProjects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb 文件和.asc文件保存在同一个目录下,即C盘的PADSProjects文件夹下面,否则allegro 转换时会出现pads_in.log找不到的现象。(关于AD的pcb文件导入pads,网上还有一种方法是AD保存为PCB二进制文件,即.PcbDoc文件,再由pads导入.PcbDoc文件。用户可以自行尝试。总之,ad转换成pads似乎较为顺畅) 1.4格式选择PowerPCBV5.0,勾选认为比较的项目。点击“OK”。 1.5随后使用allegro的import-》translator,选择pads,弹出如下的对话框。 其中第一行是指定.asc文件,第三行是指定要转换成的.brd文件。一般而言都是C盘的PADSProjects文件夹内部。第二行只要指定目录,然后在对话框里点保存即可。点击translate,即可完成转换。随后file-》open,打开刚才建立的.brd文件。

- cadence16.3光绘文件生成步骤

- Allegro如何生成光绘文件(转贴,整理)

- AD导出PCB光绘文件步骤

- AD 生成gerber文件的详细说明

- 用AD6、AD9画完PCB生成gerber文件详细说明

- 出光绘文件

- 生成GERBER文件步骤及CAM350的简单使用

- allegro 光绘文件制作2008-04-01

- 图解 Altium Designer光绘文件导出主要步骤

- Allegro16.6光绘生成步骤

- Allegro16.6光绘生成步骤

- Protel99se如何生成gerber文件

- gerber文件生成

- 生成gerber文件的各层说明

- allegro导出Gerber文件图文操作

- Protel DXP2004生成Gerber文件和钻孔文件的一般步骤

- 生成光绘文件

- Altium生成gerber文件

- Allegro制作光绘文件

- Allegro16.6光绘生成步骤