74LS73组成的单脉冲发生器

74LS73组成的单脉冲发生器

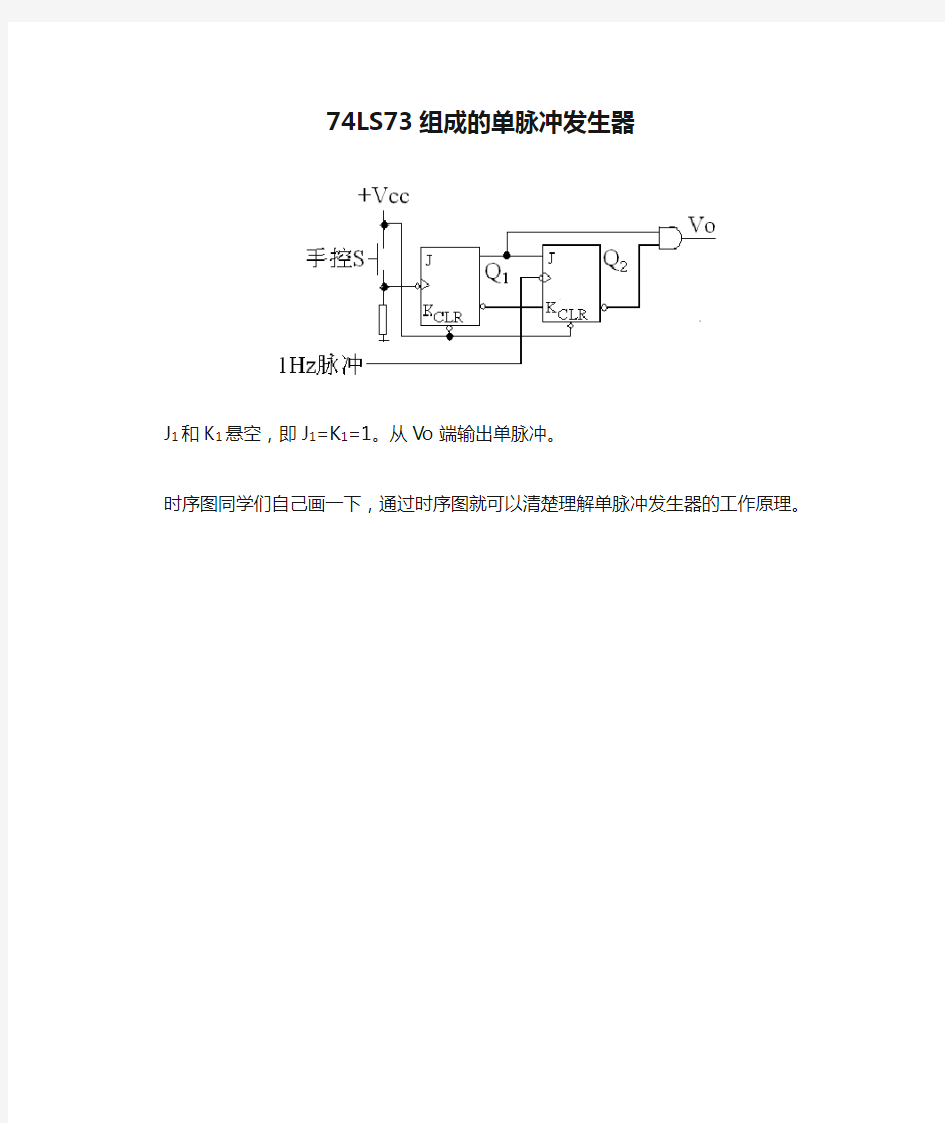

J1和K1悬空,即J1=K1=1。从V o端输出单脉冲。

时序图同学们自己画一下,通过时序图就可以清楚理解单脉冲发生器的工作原理。

FPGA_可编程单脉冲发生器设计

8.3 可编程单脉冲发生器 可编程单脉冲发生器是一种脉冲宽度可编程的信号发生器,其输出为TTL 电平。在输入按键的控制下,产生单次的脉冲,脉冲的宽度由8位的输入数据控制(以下称之为脉宽参数)。由于是8位的脉宽参数,故可以产生255种宽度的单次脉冲。 在目标板上,I0~I7用作脉宽参数输入,PULSE_OUT用做可编程单脉冲输出,而KEY和/RB作为启动键和复位键。图3示出了可编程单脉冲发生器的电路图。 图3 可编程单脉冲发生器的电路图 8.3.1 由系统功能描述时序关系 可编程单脉冲发生器的操作过程是: (1) 预置脉宽参数。 (2) 按下复位键,初始化系统。 (3) 按下启动键,发出单脉冲。 以上三步可用三个按键来完成。但是,由于目标板已确定,故考虑在复位键按下后,经过延时自动产生预置脉宽参数的动作。这一过程可用图4的时序来描述。

图4 可编程单脉冲发生器的时序图 图中的/RB为系统复位脉冲,在其之后自动产生LOAD脉冲,装载脉宽参数N。之后,等待按下/KEY键。/KEY键按下后,单脉冲P_PULSE便输出。在此,应注意到:/KEY的按下是与系统时钟CLK不同步的,不加处理将会影响单脉冲P_PULSE的精度。为此,在/KEY按下期间,产生脉冲P1,它的上跳沿与时钟取得同步。之后,在脉宽参数的控制下,使计数单元开始计数。当达到预定时间后,再产生一个与时钟同步的脉冲P2。由P1和P2就可以算出单脉冲的宽度Tw。 8.3.2 流程图的设计 根据时序关系,可以做出图5所示的流程图。 在系统复位后,经一定的延时产生一个预置脉冲LOAD,用来预置脉宽参数。应该注意:复位脉冲不能用来同时预置,要在其之后再次产生一个脉冲来预置脉宽参数。 为了产生单次的脉冲,必须考虑到在按键KEY有效后,可能会保持较长的时间,也可能会产生多个尖脉冲。因此,需要设计一种功能,使得当检测到KE Y有效后就封锁KEY的再次输入,直到系统复位。这是本设计的一个关键所在。

几种简单的函数信号发生器电路图分析

几种简单的函数信号发生器电路图分析 时间:2012-01-10 15:30 作者:赛微编辑来源:赛微电子网 引言 随着模拟电路技术和电力电子技术发展,电路设计中对信号的精度、稳定性、抗干扰能力等要求进一步提高,电子行业中将一些功能进行集成到IC芯片供其他的厂家来使用。在电路设计中,我们除了正常的电源输入之外,还需要提供三角波、方波、正弦波、脉冲波、单次脉冲等特殊的波形来给某个电路提供输入。 这种可以提供三角波、方波、正弦波、脉冲波、单次脉冲等特殊的波形的电路或者仪器(函数信号发生器的种类),我们可以称之为函数信号发生器,它对电子工程师设计的整个系统来说,发挥着重要的作用,它具有各种内置信号、自定义的任意波形和脉冲能力,能帮助您验证设计,检验新的构想,从而让整个设计更具有可靠性。 本文结合几种简单的函数信号发生器电路图,并对其工作原理(函数信号发生器原理)、可以实现的功能和性能、电路特点等方面做了详细的分析,供电子发烧友参考。 程控函数信号发生器电路图 它主要由主控制器LPC2114、MAX038、D/A转换器以及八选一模拟开关CD4051LED显示、键盘、波段切换,波形处理和峰值检波等部分组成,研究了LPC2114通过D/A转换器实现对MAX038频就绪和占空比的调控方法,并给出

了在0.1Hz~20MHz内产生精确的正弦波、方波和三角波的方法。此外,它还具有可调范围大、精度高、信号稳定等特点,可以应用于各种电子测量和控制场合。 LPC2114主要通过D/A转换器TLC5618、DAC0832和八选一模拟开关CD4051对MAX038输出的波形、频率以及占空比进行控制。通过对A1和A0端的不同设置来选择不同的波形。当A1为高电平、A0为任意时,输出波形为正弦波;当A1、A0同时为低电平时,输出波形为方波;当A1为低电平、A0为高电平时,输出波形为三角波。 MAX038输出波形的幅值为2 V(P-P),最大输出电流为+20 mA,输出阻抗的典型值为0.1 Ω。可直接驱动100 Ω的负载。为了得到更大的输出幅度和驱动能力,就需要对波形信号作进一步处理,下图为一个波形输出与驱动电路。

秒脉冲发生器

设计题目:秒脉冲发生器的设计 设计小组:第三组

1 秒脉冲发生器整体设计方案 1.1秒脉冲发生设计方案概述 秒脉冲发生器是由100HZ时钟产生电路和分频电路两部分构成,其中100HZ时钟产生电路主要由555定时器组成的时钟电路,主要用来产生100HZ的脉冲信号;分频电路主要由74LS192组成的100进制计数器电路,主要用于将100HZ 脉冲信号分成1HZ脉冲信号。该方案通过了Multisim软件仿真,并得到了1HZ的脉冲信号,基本实现了工程训练的要求。

1.2 秒脉冲发生器整体设计电路设计图 图1 秒脉冲发生器整体设计电路设计图1.3 秒脉冲发生器整体设计电路仿真图 图2 秒脉冲发生器整体设计电路仿真图

2 各分电路的元件介绍及设计方案 2.1 100HZ时钟产生电路 图3 100HZ时钟产生电路 2.1.1元件介绍 555芯片引脚图及引脚描述: 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。

信号发生器电路的焊接与调试-电路图

一、信号发生器电路安装与调试考核评分表 准考证号姓名规定时间分钟 开始时间结束时间实用时间得分 考核内容及要求配分评分标准扣分 1 元器件清点检查:在10分钟内对所有元 器件进行检测,并将不合格元器件筛选出来进 行更换,缺少的要求补发。 10 超时更换或要求补发按损坏 元件扣分,扣3分/个。 2 安装电路:按装配图进行装接,要求不装 错,不损坏元器件,无虚焊,漏焊和搭锡,元 器件排列整齐并符合工艺要求。 30 漏装,错装或虚焊、漏焊、 搭锡,扣2分/个,安装不整 齐和不符合工艺要求的扣1 分/处,损坏元件扣3分/个。 3 电源电路:接通交流电源,测量交流电压 和各直流电压+12V、-12V、V CC 、-5V。 信号发生器电路:接通+12V、-12V、V CC 、 -5V电源。测量函数信号波形:方波、正弦波、 三角波形。 20 电压测试方法不正确扣10 分,测量值有误差扣5分。 4 选择C=10uf,调节RW13、RW14、RW15, 记录方波的占空比: 1、 2、 3、 10 不会用示波观察输出信号波 形扣10分, 调节不正确扣5分, 波形记录不正确扣5分。 5 改变电容:100nf——100uf,并调节RW11, 记录正弦波输出频率f: 1、 2、 3、 10 最大不失真电压测试方法不 正确扣5分,测量值不准确 扣5分,不会计算最大不失 真功率扣5分。 6 调节RW21、RW22, 记录正弦波输出Vpp: 1、 2、 3、 10 不会测试功放电路的灵敏度 扣5分,不会计算电压放大 倍数扣5分。 7 调节电位器RW16、RW17, 记录正弦波形的失真: 1、 2、 3、 10 测量方法不正确扣5分, 测量数据每处2分,不会绘 制频响曲线扣5分 开始时间:结束时间:实用时间:

FPGA实现可编程单脉冲发生器设计

可编程单脉冲发生器设计 可编程单脉冲发生器是一种脉冲宽度可编程的信号发生器,其输出为TTL 电平。在输入按键的控制下,产生单次的脉冲,脉冲的宽度由8位的输入数据控制(以下称之为脉宽参数)。由于是8位的脉宽参数,故可以产生255种宽度的单次脉冲。 在目标板上,I0~I7用作脉宽参数输入,PULSE_OUT用做可编程单脉冲输出,而KEY和/RB作为启动键和复位键。图3示出了可编程单脉冲发生器的电路图。 图3 可编程单脉冲发生器的电路图 8.3.1 由系统功能描述时序关系 可编程单脉冲发生器的操作过程是: (1) 预置脉宽参数。 (2) 按下复位键,初始化系统。 (3) 按下启动键,发出单脉冲。 以上三步可用三个按键来完成。但是,由于目标板已确定,故考虑在复位键按下后,经过延时自动产生预置脉宽参数的动作。这一过程可用图4的时序来描述。

图4 可编程单脉冲发生器的时序图 图中的/RB为系统复位脉冲,在其之后自动产生LOAD脉冲,装载脉宽参数N。之后,等待按下/KEY键。/KEY键按下后,单脉冲P_PULSE便输出。在此,应注意到:/KEY的按下是与系统时钟CLK不同步的,不加处理将会影响单脉冲P_PULSE的精度。为此,在/KEY按下期间,产生脉冲P1,它的上跳沿与时钟取得同步。之后,在脉宽参数的控制下,使计数单元开始计数。当达到预定时间后,再产生一个与时钟同步的脉冲P2。由P1和P2就可以算出单脉冲的宽度Tw。 8.3.2 流程图的设计 根据时序关系,可以做出图5所示的流程图。 在系统复位后,经一定的延时产生一个预置脉冲LOAD,用来预置脉宽参数。应该注意:复位脉冲不能用来同时预置,要在其之后再次产生一个脉冲来预置脉宽参数。 为了产生单次的脉冲,必须考虑到在按键KEY有效后,可能会保持较长的时间,也可能会产生多个尖脉冲。因此,需要设计一种功能,使得当检测到KE Y有效后就封锁KEY的再次输入,直到系统复位。这是本设计的一个关键所在。

DDS信号发生器电路设计

1. 信号产生部分 1.1 频率控制字输入模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity ddsinput is port(a,b,c,clk,clr:in std_logic; q1,q2,q3,q4,q5:buffer unsigned(3 downto 0)); end ddsinput; architecture a of ddsinput is signal q:std_logic_vector(2 downto 0); begin q<=c&b&a; process(cp,q,clr) begin if clr='1'then q1<="0000";q2<="0000";q3<="0000";q4<="0000";q5<="0000"; elsif clk 'event and clk='1'then

DDS信号信号发生器电路设计 case q is when"001"=>q1<=q1+1; when"010"=>q2<=q2+1; when"011"=>q3<=q3+1; when"100"=>q4<=q4+1; when"101"=>q5<=q5+1; when others=>NULL; end case; end if; end process; end a; 1.2 相位累加器模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity xiangwei is port(m:in std_logic_vector(19 downto 0); clk,clr:in std_logic; data:out std_logic_vector(23 downto 0)); end xiangwei; architecture a of xiangwei is signal q:std_logic_vector(23 downto 0); begin process(clr,clk,m,q) begin if clr='1'then q<="000000000000000000000000"; elsif (clk'event and clk='1')then q<=q+m; end if; data<=q; end process; end a;

基于FPGA的单脉冲发生器

一、设计报告: 1.技术规范: 在clr的控制下置入脉宽data,在输入按键key的控制下,产生单次的脉冲pulse,脉冲的宽度由data 8位的输入数据控制(以下称之为脉宽参数)。clk_50M为系统的时钟。 2.总体设计方案: ①系统功能描述: (1)分频模块:输入为总的时钟50M,经过分频以后变为100HZ。 (2)延时模块:当clk为高电平且在复位脉冲clr有效时置入延时脉宽,延时5个始终周期后输出一个高电平load 。 (3)计数模块:脉宽参数端data接受8位的数据,经数据预置端clr 装载脉宽参数,在计数允许端有效后便开始计数。该计数器设计成为减法计数的模式,当其计数到0时,输出端pulse由高电平变为低电平。便可得到单脉冲的输出。 ②系统功能描述时序关系: 可编程单脉冲发生器的操作过程是: (1) 预置脉宽参数。 (2) 按下复位键,初始化系统。 (3) 按下启动键,发出单脉冲。 以上三步可用三个按键来完成。但是,由于目标板已确定,故考

虑在复位键按下后,经过延时自动产生预置脉宽参数的动作。

输出的信号加到灯上,输如的脉宽有开发版上的拨码开关决定,当输入脉宽后,按下复位键置入脉宽,然后按下启动键,发出单脉冲,延时一段时间后灯开始亮,亮一段时间后灯熄灭。延时模块的时序图如下: clk clr load 3.流程图的设计: 根据时序关系,可以做出图所示的流程图。 在系统复位后,经一定的延时产生一个预置脉冲load,用来预置脉宽参数。当按键key有效后产生脉冲pulse。

二、验证方案: 1.验证方案的设计: ①分频模块的设计: 分频模块的代码: module div(clk_50M,clk);//模块名及端口的定义,到endmodule。 input clk_50M;//输入端口的定义。 output clk;//输出端口的定义。 reg [31:0] a=32‘d0;//定义内部寄存器并赋初值。 reg clk=0;//给输出赋初值。 always@(posedge clk_50M) begin

脉冲信号发生器设计

脉冲信号发生器 摘要:本实验是采用fpga方式基于Alter Cyclone2 EP2C5T144C8的简易脉冲信号发生器,可以实现输出一路周期1us到10ms,脉冲宽度:0.1us到周期-0.1us,时间分辨率为 0.1us的脉冲信号,并且还能输出一路正弦信号(与脉冲信号同时输出)。输出模式 可分为连续触发和单次手动可预置数(0~9)触发,具有周期、脉宽、触发数等显示功能。采用fpga计数实现的电路简化了电路结构并提高了射击精度,降低了电路功耗和资源成本。 关键词:FPGA;脉冲信号发生器;矩形脉冲;正弦信号; 1 方案设计与比较 脉冲信号产生方案: 方案一、采用专用DDS芯片的技术方案: 目前已有多种专用DDS集成芯片可用,采用专用芯片可大大简化系统硬件制作难度,部数字信号抖动小,输出信号指标高;但专用芯片控制方式比较固定,最大的缺点是进行脉宽控制,测量困难,无法进行外同步,不满足设计要求。 方案二、单片机法。 利用单片机实现矩形脉冲,可以较方案以更简化外围硬件,节约成本,并且也可以实现灵活控制、能产生任意波形的信号发生器。但是单片机的部时钟一般是小于25Mhz,速度上无法满足设计要求,通过单片机产生脉冲至少需要三条指令,所需时间大于所要求的精度要求,故不可取。 方案二:FPGA法。利用了可编程逻辑器件的灵活性且资源丰富的特点,通过Quartus 软件的设计编写,实现脉冲信号的产生及数控,并下载到试验箱中,这种方案电路简单、响应速度快、精度高、稳定性好故采用此种方案。 2 理论分析与计算 脉冲信号产生原理:输入量周期和脉宽,结合时钟频率,转换成两个计数器的容量,用来对周期和高电平的计时,输出即可产生脉冲信号。 脉冲信号的精度保证:时间分辨率0.1us,周期精度:+0.1%+0.05us,宽度精度:

可编程脉冲信号发生器的设计说明

可编程脉冲信号发生器的设计 摘要 基于单片机的可编程脉冲信号发生器,通过4x4的非编码矩阵键盘键入脉冲信号的指标参数频率、占空比和脉冲个数,在单片机的控制处理下发出满足信号指标的脉冲信号,并在液晶显示屏的制定位置显示出相关参数。复位电路采用上电复位和手动复位的复合复位方式,保证单片机在上电和程序运行进入死循环时,单片机均能正常复位。利用在工作方式1下的定时器和计数输出低频脉冲信号,以及在工作方式2下能够自动重复赋初值的定时器输出高频脉冲信号,从而使频率和占空比满足指标要求。通过程序设计,使单片机每次发出信号后等到重置信号进行下一次脉冲信号的输出,有效的提高了单片机的使用效率。 本课题设计利用单片机技术,通过相应的软件编程和较简易的外围硬件电路来实现,其产生的脉冲信号干扰小,输出稳定,可靠性高,人机界面友好,操作简单方便,成本低,携带方便,扩展性强。关键的是,脉冲信号频率、脉冲个数和脉冲占空比可调节,可通过键盘输入并由显示器显示出来。 本课题设计所要达到的指标要求: (1)脉冲信号频率0.1HZ到50KHZ可调并在液晶显示屏指定位置显示。 (2)脉冲信号个数0到9999可调并在液晶显示屏指定位置显示。 (3)脉冲信号占空比任意可调并在液晶屏显屏指定位置示出来。 关键词:单片机,脉冲信号,频率,脉冲个数,占空比

Programmable pulse signal generator design ABSTRACT The programmable pulse signal generator based on single chip, through the 4x4 non-coding matrix keyboard inputing pulse signal parameters of frequency, duty cycle and pulse number, pulse signal is sent to meet the targets of signal processing chip.The related parameters are displayed on the setting position on the liquid crystal. The reset circuit by power-on reset and manual reset, ensure the SCM in power and run into dead circulation can be reset. Use in work mode 1 timer and counter output low frequency pulse signal, and in work mode 2 to timer output high frequency pulse signal ,automaticly repeat initialization, so as to make the frequency and duty ratio meet the requirements. Through the program design, the microcontroller each signal and then wait for the reset signal, the signal at the output of the pulse next time, effectively improve the efficiency in the use of single-chip microcomputer. The subject of the use of single-chip technology, which achieved through the corresponding software and the simple peripheral hardware circuit. The advantages of which are the small interference of the pulse signal, output stability, high reliability, friendly man-machine interface, easy operation, low cost, portability, scalability strong. The keys, pulse frequency, pulse number and pulse duty ratio are adjustable, which can be inputed through the keyboard and displayed through LCD. The requirements of this topic design: (1) The pulse signal frequency of 0.1HZ to 50KHZ is adjustable and can be displaied on the specify location in the LCD screen. (2) Pulse signal number of 0 to 9999 is adjusted and can be displaied on the specify location in the LCD screen. (3)Pulse duty ratio is adjustable and can be displaied on the specify

信号发生器的基本原理

信号发生器的基本原理- 信号发生器使用攻略 信号发生器的基本原理 现代信号发生器的结构非常复杂,与早期的简易信号发生器天差地别,但总体基本结构功能单元还是类似的。信号发生器的主要部件有频率产生单元、调制单元、缓冲放大单元、衰减输出单元、显示单元、控制单元。早期的信号发生器都采用模拟电路,现代信号发生器越来越多地使用数字电路或单片机控制,内部电路结构上有了很大的变化。 频率产生单元是信号发生器的基础和核心。早期的高频信号发生器采用模拟电路LC振荡器,低频信号发生器则较多采用文氏电桥振荡器和RC移相振荡器。由于早期没有频率合成技术,所以上述LC、RC振荡器优点是结构简单,可以产生连续变化的频率,缺点是频率 稳定度不够高。早期产品为了提高信号发生器频率稳定度,在可变电容的精密调节方面下了很多功夫,不少产品都设计了精密的传动机构和指示机构,所以很多早期的高级信号发生器体积大、重量重。后来,人们发现采用石英晶体构成振荡电路,产生的频率稳定,但是石英晶体的频率是固定的,在没有频率合成的技术条件下,只能做成固定频率信号发生器。之后 也出现过压控振荡器,虽然频率稳定度比LC振荡器好些,但依然不够理想,不过压控振荡 器摆脱了LC振荡器的机械结构,可以大大缩减仪器的体积,同时电路不太复杂,成本也不高。现在一些低端的函数信号发生器依然采用这种方式。 随着PLL锁相环频率合成器电路的兴起,高档信号发生器纷纷采用频率合成技术,其 优点是频率输出稳定(频率合成器的参考基准频率由石英晶体产生),频率可以步进调节,频率显示机构可以用数字化显示或者直接设置。早期的高精度信号发生器为了得到较小的频率步进,将锁相环做得非常复杂,成本很高,体积和重量都很大。目前的中高端信号发生器 采用了更先进的DDS频率直接合成技术,具有频率输出稳定度高、频率合成范围宽、信号频谱纯净度高等优点。由于DDS芯片高度集成化,所以信号发生器的体积很小。 信号发生器的工作频率范围、频率稳定度、频率设置精度、相位噪声、信号频谱纯度都与频率产生单元有关,也是信号发生器性能的重要指标。 信号发生器的一大特性就是可以操控仪器输出信号的幅度,信号通过特定组合衰减量的衰减器达到预定的输出幅度。早期的衰减器是机械式的,通过刻度来读取衰减量或输出幅度。现代中高档信号发生器的衰减器单元由单片机控制继电器来切换,向电子芯片化过渡,衰减单元的衰减步进量不断缩小,精度相应提高。大频率范围的高精度衰减器和高精度信号输出属于高科技技术,这也是国内很少有企业能制造高端信号发生器的原因之一。信号发生器的信号输出范围和输出电平的精度和准确度也是标志信号发生器性能的重要指标。

脉冲信号发生器的使用方法

脉冲信号发生器的使用方法 脉冲信号发生器可以产生重复频率、脉冲宽度及幅度均为可调的脉冲 信号,广泛应用于脉冲电路、数字电路的动态特性测试。脉冲信号发生器一般 都以矩形波为标准信号输出。脉冲信号发生器的种类繁多,性能各异,但 内部基本电路应包括主振级一般由无稳态电路组成,产生重复频率可调的周期 性信号。隔离级由电流开关组成,它把主振级与下一级隔开,避免下一级对主 振级的影响,提高频率的稳定度。脉宽形成级一般由单稳态触发器和相减电路 组成,形成脉冲宽度可调的脉冲信号。放大整形级是利用几级电流开关电路对 脉冲信号进行限幅放大,以改善波形和满足输出级的激励需要。输出级满足脉 冲信号输出幅度的要求,使脉冲信号发生器具有一定带负载能力。通过衰减器 使输出的脉冲信号幅度可调。 如(1)XC-15型脉冲信号发生器的面板开关、旋钮的功能及使用 ①频率粗调开关和频率细调旋钮。调节频率粗调开关和频率细调旋钮, 可实现1kHz~100MHz的连续调整。粗调分为十挡 (1kHz、3kHz、10kHz、100kHz、300kHz、1MHz、3MHz、10MHz、30MHz 和100MHz),用细调覆盖。频率细调旋钮顺时针旋转时频率增高,顺时针旋转 到底,为频率粗调开关所指频率;逆时针旋转到底,为此频率粗调开关所指刻 度低一挡。例如,频率粗调开关置于10kHz挡,频率细调旋钮顺时针旋转到底 时输出频率为10kHz;逆时针旋转到底时输出频率为3kHz。 ②延迟粗调转换开关和延迟细调旋钮。调节此组开关和旋钮,可实现延 迟时间5ns~300,tts的连续调整。延迟粗调分为十挡 (5ns、10ns、30ns、l00ns、300ns、1μs、3μs、10μs、30μs和100μs),用细调覆盖。延迟时间加上大约30ns的固有延迟时间等于同步输

(Proteus数电仿真)序列信号发生器电路设计

实验8 序列信号发生器电路设计 一、实验目的: 1.熟悉序列信号发生器的工作原理。 2.学会序列信号发生器的设计方法。 3.熟悉掌握EDA软件工具Proteus 的设计仿真测试应用。 二、实验仪器设备: 仿真计算机及软件Proteus 。 74LS161、74LS194、74LS151 三、实验原理: 1、反馈移位型序列信号发生器 反馈移位型序列信号发生器的结构框图如右图 所示,它由移位寄存器和组合反馈网络组成, 从寄存器的某一输出端可以得到周期性的序列 码。设计按一下步骤进行: (1)确定位移寄存器位数n ,并确定移位 寄存器的M 个独立状态。 CP 将给定的序列码按照移位规律每 n 位一组,划分为M 个状态。 若M 个状态中出现重复现象,则应增加移位寄存器的位数。用n+1位再重复上述过程,直到划分为M 个独立状态为止。 (2)根据M 各不同状态列出寄存器的态序表和反馈函数表,求出反馈函数F 的表达式。 (3)检查自启动性能。 (4)画逻辑图。 2、计数型序列信号发生器 计数型序列信号发生器和组合的结构框图 如图 所示。它由计数器和组合输出网络两部分 组成,序列码从组合输出网络输出。设计 过程分为以下两步: (1)根据序列码的长度M 设计模M (2)按计数器的状态转移关系和序列码的要求组合输出网络。由于计数器的状态设置和输出序列没有直接关系,因此这种结构对于输出序列的更改比较方便,而且还能产生多组序列码。 四、计算机仿真实验内容及步骤、结果: 1、设计一个产生100111序列的反馈移位型序列信号发生器。 1、根据电路图在protuse 中搭建电路图

基于FPGA的单脉冲发生器

西安邮电大学FPGA课程设计报告 题目:可编程单脉冲发生器 院系:通信与信息工程学院专业班级:电子信息科学与技术学生姓名:韩萌 导师姓名:张丽果 起止时间:2012-9-10至2012-9-22 2012年09月20日

FPGA课程设计报告提纲 1.任务 根据输入的8位的脉宽参数,输出255种宽度的单次脉冲。 可编程单脉冲发生器是一种脉冲宽度可编程的信号发生器,在输入按键的控制下,产生单次的脉冲,脉冲的宽度由8位的输入数据控制。由于是8位的脉宽参数,故可以产生255 种宽度的单次脉冲。 2.目的 产生一个脉冲宽度可根据8位输入数据(data)可变的脉冲发生器。 可变的脉冲信号可以通过把输入的data赋值给一个count,通过对count信号做减1操作控制输出的脉冲宽度。把data赋给count后,在key键启动的情况下,输出脉冲pulse信号开 始输出低电平,count同时在每来一个时钟信号的时候做减1操作,而且pulse信号一直保持高 电平,当count减为0时,把pulse信号拉低。这样就输出了一个脉冲宽度可以根据data输入信 号可变的脉冲信号。 3.使用环境(软件/硬件环境,设备等) 布局布线使用的环境是Quartus II。 仿真测试使用的环境是ModelSim SE。 4.FPGA课程设计详细内容 4.1 技术规范 (一)、功能定义如下: 本设计实现一个可编程单脉冲发生器,具体功能如下: 1.异步信号复位,复位后信号输出可以重新开始。 2.把8为脉冲宽度data赋给计数信号count。 3.当有key按键使能时,输出脉冲信号,并做count减1操作,重复再按使能键无效。 4.使能按键后产生的单脉冲的上升沿与时钟取得同步。 5.当count减为0时,脉冲信号拉低。高电平持续的宽度,即所需的脉冲宽度。 6.产生的脉冲信号的最大宽度为255。 (二)、引脚定义

4 脉冲信号产生电路共23页文档

4 脉冲信号产生电路 4.1 实验目的 1.了解集成单稳态触发器的基本功能及主要应用。 2.掌握555定时器的基本工作原理及其性能。 3.掌握用555定时器构成多谐振荡器、单稳态触发器的工作原理、设计及调试方法。 4.2 实验原理 1.集成单稳态触发器及其应用 在数字电路的时序组合工作中,有时需要定时、延时电路产生定时、展宽延时等脉冲,专门用于完成这种功能的IC,就是“单稳延时多谐振荡器”,也称“单稳触发器”。其基本原理是利用电阻、电容的充放电延时特性以及电平比较器对充放电电压检测的功能,实现定时或延时,只需按需要灵活改变电阻、电容值大小,就可以取得在一定时间范围的延时或振荡脉冲输出。常用的器件有LS121/122、LS/HC123、LS/HC221、LS/HC423、HC/C4538及CC4528B等。 集成单稳态触发器在没有触发信号输入时,电路输出Q=0,电路处于稳态;当输入端输入触发信号时,电路由稳态转入暂稳态,使输出Q=1;待电路暂稳态结束,电路又自动返回到稳态Q=0。在这一过程中,电路输 出一个具有一定宽度的脉冲,其宽度与电路的外接定时元件C ext 和R ext 的数 值有关。 图4-1

集成单稳态触发器有非重触发和可重触发两种,74LS123是一种双可重触发的单稳态触发器。它的逻辑符号及功能表如图4-1、表4-1所示。 在表4-1中“正”为正脉冲,“负”为负脉冲。 LS/HC123的特点是,复位端CLR也具有上跳触发单稳态过程发生的功能。 在C ext >1000pF时,输出脉冲宽度t w ≈0.45R ext C ext 。 器件的可重触发功能是指在电路一旦被触发(即Q=1)后,只要Q还未恢复到0,电路可以被输入脉冲重复触发,Q=1将继续延长,直至重复触发的最后一个触发脉冲的到来后,再经过一个t w (该电路定时的脉冲宽度)时间,Q才变为0,如图4-2所示: 图4-2 74LS123的使用方法: (1)有A和B两个输入端,A为下降沿触发,B为上升沿触发,只有AB=1时电路才被触发。 (2)连接Q和A或Q与B,可使器件变为非重触发单稳态触发器。 (3)CLR=0时,使输出Q立即变为0,可用来控制脉冲宽度。 (4)按图4-3、3-5-4连接电路,可组成一个矩形波信号发生器,利用开关S瞬时接地,使电路起振。 图4-3 图4-4 2.555时基电路及其应用 555时基电路是一种将模拟功能和数字逻辑功能巧妙地结合在同一硅片上的新型集成电路,又称集成定时器,它的内部电路框图如图4-5所示。 图4-5 电路主要由两个高精度比较器C 1、C 2 以及一个RS触发器组成。比较器 的参考电压分别是2/3V CC 和1/3V CC ,利用触发器输入端TR输入一个小于 1/3V CC 信号,或者阈值输入端TH输入一个大于2/3V CC 的信号,可以使触发 器状态发生变换。CT是控制输入端,可以外接输入电压,以改变比较器的参考电压值。在不接外加电压时,通常接0.01μF电容到地,DISC是放电输入端,当输出端的F=0时,DISC对地短路,当F=1时,DISC对地开路。 R D 是复位输入端,当R D =0时,输出端有F=0。 器件的电源电压V CC 可以是+5V~+15V,输出的最大电流可达200mA,当 电源电压为+5V时,电路输出与TTL电路兼容。555电路能够输出从微秒级到小时级时间范围很广的信号。 (1)组成单稳态触发器 555电路按图4-6连接,即构成一个单稳态触发器,其中R、C是外接定时元件。单稳态触发器的输出脉冲宽度t w ≈1.1RC。 图4-6 (2)组成自激多谐振荡器 图4-7 自激多谐振荡器电路 按图4-7连接,即连成一个自激多谐振荡器电路,此电路的工作过程

脉冲信号发生器与计数器

中南林业科技大学涉外学院 认识实习报告 名称:脉冲信号发生器与计数器 姓名学号: 系:理工系专业:电子信息工程班级:实习时间:实习地点:

目录 一、题目 二、任务和要求 三、内容 (1)如何用仪表测量 (2)如何焊接 (3)如何调试 四、结论 五、体会和收获

一、题目脉冲信号发生其与计数器 二、任务和要求 1:焊接电路板 2:装配电阻、安装短路线、装配芯片、装配按键S、装配电容、装配发光二极管、安装电源插座、测试 三、内容 (1)安装好后,目测检查,是否焊接好了。插入电源线,电源线额另一端接电源,一定不要接错了,印刷板上标有+的一端接电源+5V,另一端接 地。千万注意,电源不要接错了。打开电源,测试电源电压,测试芯片 上各脚电压。按下按键,试着短按和长按,观察现象。测试各发光二极 管(有亮的也有不亮的都测)的电压。短按时,每次产生一个脉冲,观 察到由发光二极管显示的二进制数加一。长按时,产生连续脉冲,观察 到由发光二极管显示的二进制数连续累加。 (2)加热焊件;移入焊锡;焊锡融化后,移开焊锡;移开电烙铁。注意掌握好时间,焊接好后,剪去焊盘外的导线 (3)打开电源,测试电源电压,测试芯片上各脚电压。按下按键,试着短按和长按,观察现象 四、结论 利用集成定时器(芯片 NE555)产生信号,当按键被单次单次地按下时,产生一个一个的单脉冲信号;当按键按下不动时,产生连续脉冲信号。可利用集成技术器(芯片4024)计数。其状态反映脉冲的个数。利用发光二级管显示已经计数的脉冲数,其中74LS04是驱动电路。 五、体会和收获 经过这次实习,了解到了如何焊接电路板、焊接电路板所需注意的事项、认识各种原配件和如何检测焊成后的电路板,同时培养了自己的动手能力和对电路这门课程的认知

多功能信号发生器课程设计

《电子技术课程设计》 题目:多功能信号发生器 院系:电子信息工程 专业:xxxxxxxx 班级:xxxxxx 学号:xxxxxxxx 姓名:xxx 指导教师:xxx 时间:xxxx-xx-xx

电子电路设计 ——多功能信号发生器目录 一..课程设计的目的 二课程设计任务书(包括技术指标要求) 三时间进度安排(10周~15周) a.方案选择及电路工作原理; b.单元电路设计计算、电路图及软件仿真; c.安装、调试并解决遇到的问题; d.电路性能指标测试; e.写出课程设计报告书; 四、总体方案 五、电路设计 (1)8038原理, LM318原理, (2)性能\特点及引脚 (3)电路设计,要说明原理 (4)振动频率及参数计算 六电路调试 要详细说明(电源连接情况, 怎样通电\ 先调试后调试,频率调试幅度调试波行不稳调试 七收获和体会

一、课程设计的目的 通过对多功能信号发生器的电路设计,掌握信号发生器的设计方法和测试技术,了解了8038的工作原理和应用,其内部组成原理,设计并制作信号发生器能够提高自己的动手能力,积累一定的操作经验。在对电路焊接的途中,对一些问题的解决能够提高自己操作能力随着集成制造技术的不断发展,多功能信号发射器已经被制作成专用的集成电路。这种集成电路适用方便,调试简单,性能稳定,不仅能产生正弦波,还可以同时产生三角波和方波。它只需要外接很少的几个元件就能实现一个多种波、波形输出的信号发生器。不仅如此,它在工作时产生频率的温度漂移小于50×10-6/℃;正弦波输出失真度小于1%,输出频率范围为0.01Hz~300kHz;方波的输出电压幅度为零到外接电源电压。因此,多功能信号发生器制作的集成电路收到了广泛的应用。 二、课程设计任务书(包括技术指标要求) 任务:设计一个能产生正弦波、方波、三角波以及单脉冲信号发生器。 要求: 1.输出频率为f=20Hz~5kHz的连续可调正弦波、方波和三角波。 2.输出幅度为5V的单脉冲信号。 3.输出正弦波幅度V o= 0~5V可调,波形的非线性失真系数γ≤

脉冲信号发生器

电子技术综合训练 设计报告 题目:脉冲信号发生器 姓名:xxx 学号:xxxxxxx 班级:xx 电气及其自动化xx 同组成员:xxx 指导教师:xxx 日期:2011年1月4日

脉冲信号发生器的原理主要分为四部分,即正弦波的产生,方波的变换,分频电路和倍频电路,并由这四部分最终产生三种不同频率的信号,其要点在于电路的线路连接及焊接。通过设计体会理论与实际结合的重要性. 关键字:正弦发生多谐振荡器降频电路锁相环

一、设计任务和要求 (5) 1.1设计任务 (5) 1.2设计要求 (5) 二、系统设计 (6) 2.1系统要求 (6) 2.2方案设计 (6) 2.3系统工作原理 (7) 三、单元电路设计 (8) 3.1 RC正弦发生器 (8) 3.1.1电路结构及工作原理 (9) 3.1.2电路仿真 (9) 3.1.3元器件的选择及参数确定 (9) 3.2 555定时器组成的多谐振荡器 (9) 3.2.1电路结构及工作原理 (9) 3.2.2电路仿真 (11) 3.3 74LS161计数器降频电路 (11) 3.3.1电路结构及工作原理 (11)

3.3.2电路仿真 (11) 3.3.3元器件的选择及参数确定 (11) 3.4 锁相环升频电路 (13) 3.4.1电路结构及工作原理 (13) 3.4.2元器件的选择及参数确定 (15) 四、系统仿真 (17) 五、电路安装、调试与测试 (18) 5.1电路安装 (17) 5.2电路调试 (17) 5.3系统功能及性能测试 (17) 5.3.1测试方法设计 (18) 5.3.2测试结果及分析 (18) 结论 (19) 参考文献 (20) 总结、体会和建议 (21) 附录 (22)

如何正确使用脉冲信号发生器

如何正确使用脉冲信号发生器 脉冲信号发生器可以产生重复频率、脉冲宽度及幅度均为可调的脉冲信号,广泛应用于脉冲电路、数字电路的动态特性测试。脉冲信号发生器一般都以矩形波为标准信号输出。 脉冲信号发生器的种类繁多,性能各异,但内部基本电路应包括图1所示的几个部分。 主振级一般由无稳态电路组成,产生重复频率可调的周期性信号。隔离级由电流开关组成,它把主振级与下一级隔开,避免下一级对主振级的影响,提高频率的稳定度。脉宽形成级一般由单稳态触发器和相减电路组成,形成脉冲宽度可调的脉冲信号。放大整形级是利用几级电流开关电路对脉冲信号进行限幅放大,以改善波形和满足输出级的激励需要。输出级满足脉冲信号输出幅度的要求,使脉冲信号发生器具有一定带负载能力。通过衰减器使输出的脉冲信号幅度可调。 所示为xc-15型脉冲信号发生器的面板示意图,xc-15型脉冲信号发生器是高重复频率ns(纳秒)级脉冲信号发生器。其重复频率范围为1kHz~100MHz,脉冲宽度为5ns~300μs,幅度为150mV~5V,并输出正、负脉冲及正、负倒置脉冲,性能比较完善。 (1)XC-15型脉冲信号发生器的面板开关、旋钮的功能及使用 ① “频率”粗调开关和“频率细调”旋钮。调节“频率”粗调开关和“频率细调”旋钮,可实现 1kHz~100MHz的连续调整。粗调分为十挡(1kHz、 3kHz、10kHz、100kHz、300kHz、1MHz、3MHz、10MHz、30MHz和100MHz),用细调覆盖。“频率细调”旋钮顺时针旋转时频率增高,顺时针旋转到底,为“频率”粗调开关所指频率;逆时针旋转到底,为此“频率”粗调开关所指刻度低一挡。例如,“频率”粗调开关置于 10kHz挡,“频率细调”旋钮顺时针旋转到底时输出频率为10kHz;逆时针旋转到底时输出频率为3kHz。 ②“延迟”粗调转换开关和“延迟细调”旋钮。调节此组开关和旋钮,可实现延迟时间5ns~300,tts的连续调整。延迟粗调分为十挡(5ns、10ns、30ns、l00ns、 300ns、1μs、3μs、10μs、30μs和100μs),用细调覆盖。延迟时间加上大约30ns的固有延迟时间等于同步输出负方波的下降沿超前主脉冲前沿的时间。 “延迟细调”旋钮逆时针旋转到底为粗调挡所指的延迟时间。顺时针旋转延迟时间增加,顺时针旋转到底为此粗调挡位高一挡的延迟时间。例如,“延迟”粗调开关置于30ns挡,“延迟细调”旋钮顺时针旋转到底时输出延迟时间为100ns;逆时针旋转到底时输出延迟时间为30ns。 ③ “脉宽”粗调开关和“脉宽细调”旋钮。通过调节此组开关和旋钮,可实现脉宽5ns~300μs的连续调整。“脉宽”粗调分为十挡(5ns、10ns、 30ns、100ns、300ns、1μs、3μs、10μs、30μs和100μs),用细调覆盖。“脉宽细调”旋钮逆时针旋转到底为粗调挡所指的脉宽时间。顺时针旋转脉宽增加,顺时针旋转到底为此粗调挡位高一挡的脉宽。例如,“脉宽”粗调开关置于10ns挡,“脉宽细调”旋钮顺时针旋转到底时输出脉宽为30ns;逆时针旋转到底时输出延迟时间为10ns。 ④“极性”选择开关。转换此开关可使仪器输出四种脉冲波形中的一种。 ⑤“偏移”旋钮。调节偏移旋钮可改变输出脉冲对地的参考电平。 ⑥“衰减”开关和“幅度”旋钮。调节此组开关和旋钮,可实现150mV~5V的输出脉冲幅度调整。