VHDL选择运算器SEL

选择运算器

1 实验目的:

● 通过设计选择运算器以进一步掌握VHDL 硬件描述语言;

● 熟悉比较器、乘法器的原理与设计风格;

● 熟悉包集和元件的使用。

2 实验原理及设计思路

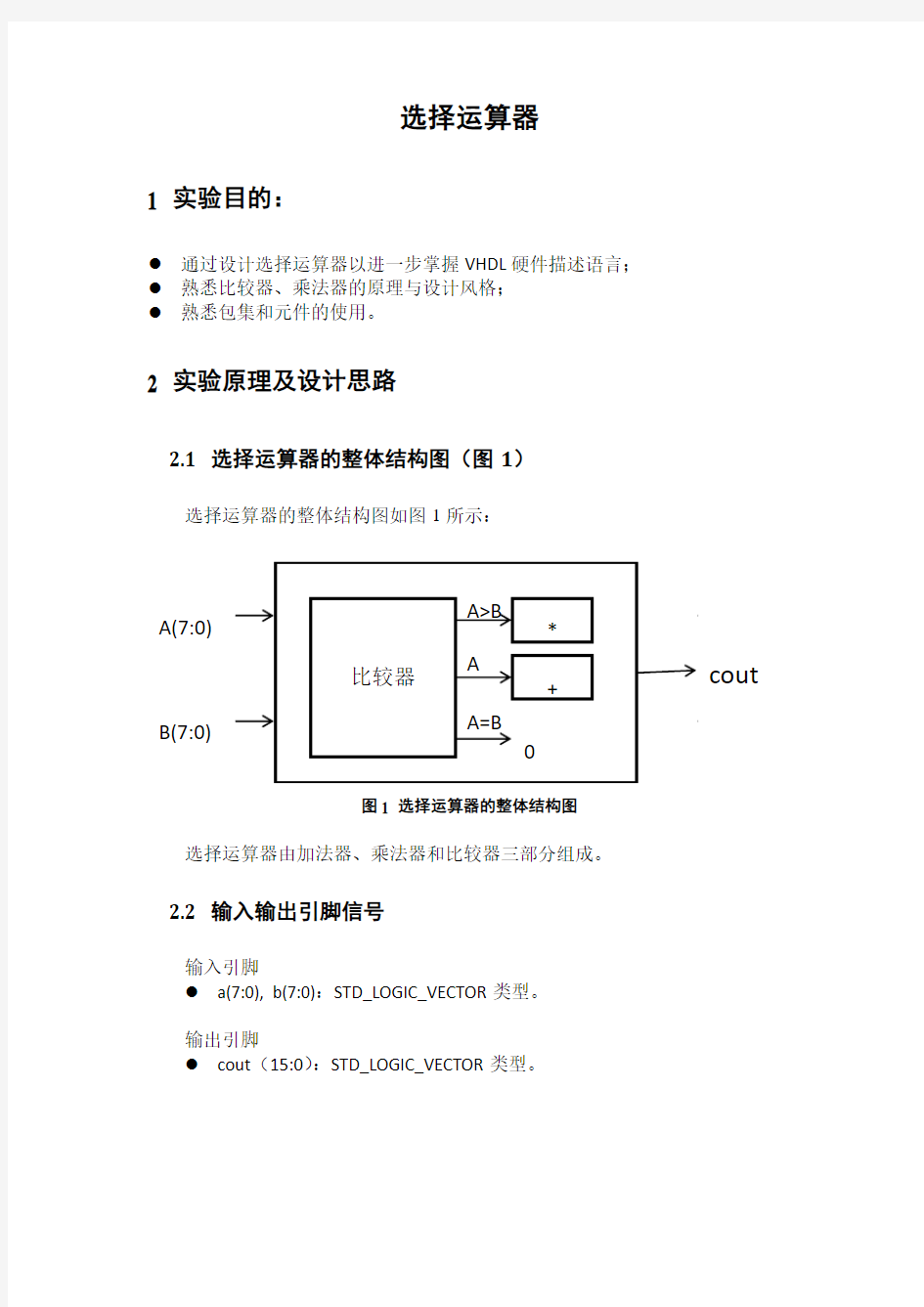

2.1 选择运算器的整体结构图(图1)

选择运算器的整体结构图如图1所示:

图1 选择运算器的整体结构图

选择运算器由加法器、乘法器和比较器三部分组成。

2.2 输入输出引脚信号

输入引脚

● a(7:0), b(7:0):STD_LOGIC_VECTOR 类型。

输出引脚

● cout (15:0):STD_LOGIC_VECTOR 类型。

A(7:0)

B(7:0) cout

2.3 设计原理

2.3.1 加法器设计原理

本实验使用包集和元件调用的方式来实现加法器。因此,先要构建4位加法器的基本原件,然后在8位加法器中调用2次使用。

(1)4位加法器的设计

加法器是最常用的运算器件,根据不同的系统需求具有多种不同的结构。本实验的4位加法器采用超前进位加法器。对于输入的两个4位加数a(3:0)、b(3:0)和进位信号cin,首先要构建传播信号p(3:0)和进位产生信号g(3:0)。算法如下所示:

p <= axor b;

g <= a and b;

各级进位信号的产生算法如下所示:

c(0) <= cin;

c(1) <= (cin and p(0)) or g(0);

c(2) <= (cin and p(0) and p(1)) or (g(0) and p(1)) or g(1);

c(3) <= (cin and p(0) and p(1) and p(2)) or (g(0) and p(1) and p(2)) or (g(1) and p(2)) or g(2);

c(4) <= (cin and p(0) and p(1) and p(2) and p(3)) or (g(0) and p(1) and p(2) and p(3)) or (g(1) and p(2) and p(3)) or (g(2) and p(3)) or g(3);

输出的4位运算结果和进位信号cout的产生算法如下所示:

cout<= c(4);

s <= p xor c;

(2)8位加法器的设计

在设计8位加法器时,需要调用4位加法器。因此需要声明4位加法器原件。元件的声明可以放在主代码的结构体中,也可以放在包集中。为了增强代码的通用性,本实验将声明放在包集中。故在主代码的库和包集调用部分,需要声明定义加法器的包集。然后就可以使用包集中定义的4位超前进位加法器了。

2.3.2 乘法器设计原理

本实验采用并行乘法器的结构。

乘法器的本身使用很多子模块实现的本实验要进行8位的并行乘法器的设计,其原理与4位并行乘法器相同。

2.3.3 比较器设计原理

比较器是个比较简单的模块。将输入A与B进行比较,如果A>B则实现A 与B的乘运算;如果A 3 实验程序源代码 libraryieee; use ieee.std_logic_1164.all; useieee.std_logic_arith.all; useieee.std_logic_unsigned.all; entitymul is port(a,b:instd_logic_vector(7 downto 0); c:out std_logic_vector(15 downto 0) ); end entity; architecture be of mul is begin process(a,b) variabletemp:std_logic_vector(15 downto 0); begin temp:=(others=>'0'); if(b(7)='1') then temp:=temp+a; end if; for i in 0 to 7 loop temp:=temp(14 downto 0)&'0'; if(b(7-i)='1') then temp:=temp+a; end if; end loop; c<=temp; end process; end architecture be; libraryieee; use ieee.std_logic_1164.all; entity adder is port(a,b:instd_logic_vector(3 downto 0); cin:instd_logic; cout:outstd_logic; s:out std_logic_vector(3 downto 0) ); end entity; architecture be of adder is signalg,p:std_logic_vector(3 downto 0); signal c:std_logic_vector(4 downto 0); begin g1: for i in 0 to 3 generate g(i)<=a(i) and b(i); p(i)<=a(i) xor b(i); s(i)<=p(i) xor c(i); end generate; c(0)<=cin; c(0)<=cin; c(1)<=(cin AND p(0)) OR g(0); c(2)<=(p(0) AND p(1) AND cin) OR (p(1) AND g(0)) OR g(1); c(3)<=(p(0) AND p(1) AND cin AND p(2)) OR (p(2) AND p(1) AND g(0))OR (p(2) AND g(1)) OR g(2); c(4)<=(p(0) AND p(1) AND cin AND p(2) AND P(3)) OR (g(0) AND p(1) AND P(2) AND p(3)) OR (g(1) AND p(2) AND p(3)) OR (g(2) AND p(3)) OR g(3); cout<=c(4); end architecture; libraryieee; use ieee.std_logic_1164.all; useieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entitysel is port(a,b:instd_logic_vector(7 downto 0); cout:outstd_logic_vector(15 downto 0) ); end entity; architecture be of sel is component adder is port(a,b:instd_logic_vector(3 downto 0); cin:instd_logic; cout:outstd_logic; s:out std_logic_vector(3 downto 0) ); end component; componentmul is port(a,b:instd_logic_vector(7 downto 0); c:out std_logic_vector(15 downto 0) ); end component; signal t:std_logic; signal s1,s2:std_logic_vector(15 downto 0); begin v1:mul port map (a,b,s1); v2:adder port map (a(3 downto 0),b(3 downto 0),'0',t,s2(3 downto 0)); v3:adder port map (a(7 downto 4),b(7 downto 4),t,s2(8),s2(7 downto 4)); s2(15 downto 9)<=(others=>'0'); process(a,b,s1,s2) begin if(a>b) then cout<=s1; elsif(a cout<=s2; else cout<=(others=>'0'); end if; end process; end be; 4 实验仿真结果 得到的仿真结果如图3所示。 图3仿真结果 由实验仿真结果可知,原程序可以实现所要求的选择运算功能,实验成功。5感想与收获 本次实验较为系统的使用了包集和元件。通过设计选择运算器以进一步掌握VHDL硬件描述语言,熟悉了比较器、乘法器的原理与设计风格,熟悉了包集和元件的使用。 三次的实验设计由简单到复杂,三次实验的过程中,使我对LINUX编系统环境,了解了VHDL的编程环境,学习并实践了状态机、元件例化、端口映射等的实现,收获颇多。 《集成电路设计实践》报告 题目:8选1数据选择器 院系:自动化学院电子工程系 专业班级:微电121班 学生学号:3120433003 学生姓名:王瑜 指导教师姓名:王凤娟职称:讲师起止时间:2015-12-21---2016-1-9 成绩: 一、设计任务 1) 依据8选1数据选择器的真值表,给出八选一MUX电路图,完成由电路图到晶体管级的转化(需提出至少2种方案); 2) 绘制原理图(Sedit),完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间; 3) 遵循设计规则完成晶体管级电路图的版图,流程如下:版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图); 4) 版图检查与验证(DRC检查); 5) 针对自己画的版图,给出实现该电路的工艺流程图。 二、电路设计方案的确定 数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。它的作用相当于多个输入的单刀多掷开关,其示意图如下所示 数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路,函数发生器及数码比较器 等,常见的数据比较器有2选1,4选1,8选1,16选1电路。 示意图 在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器。 数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。 本次设计的是8选1数据选择器。选择控制端(地址端)为K2,K1,K0,按二进制译码,从8个输入数据D0-D7中,选择一个需要的数据送到输出端Y。 根据多路开关的开关状态(地址码)K2,K1,K0的状态选择D0-D7中某一个通道的数据输送到输出端Y。 如:K2K1K0=000,则选择D0数据到输出端,即Y=D0。 如:K2K1K0=001,则选择D1数据到输出端,即Y=D1,其余类推。 8选1 MUX功能表如下: K2 K1 K0 Y 0 0 0 D0 0 0 1 D1 0 1 0 D2 0 1 1 D3 1 0 0 D4 1 0 1 D5 1 1 0 D6 1 1 1 D7 Verilog HDV 数字设计与综合 实验报告 微电子0901班 姓名:袁东明 _ 学号:_04094026 一、实验课题: 1.八选一数据选择器 2.四位数据比较器 二、八选一数据选择器Verilog程序: 2.1主程序 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out); input [2:0] a,b,c,d,e,f,g,h; input s0,s1,s2; output [2:0] out; reg [2:0] out; always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begin case({s0,s1,s2}) 3'd0 : out=a; 3'd1 : out=b; 3'd2 : out=c; 3'd3 : out=d; 3'd4 : out=e; 3'd5 : out=f; 3'd6 : out=g; 3'd7 : out=h; endcase end endmodule 2.2激励程序 module sti; reg [2:0] A,B,C,D,E,F,G,H; reg S0,S1,S2; wire [2:0] OUT; option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT); initial begin A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1; 运算放大器的电路仿真设计 一、电路课程设计目的 错误!深入理解运算放大器电路模型,了解典型运算放大器的功能,并仿真实现它的功能; 错误!掌握理想运算放大器的特点及分析方法(主要运用节点电压法分析); ○3熟悉掌握Multisim软件。 二、实验原理说明 (1)运算放大器是一种体积很小的集成电路元件,它包括输入端和输出端。它的类型包括:反向比例放大器、加法器、积分器、微分器、电 压跟随器、电源变换器等. (2) (3)理想运放的特点:根据理想运放的特点,可以得到两条原则: (a)“虚断”:由于理想运放,故输入端口的电流约为零,可近似视为断路,称为“虚断”。 (b)“虚短”:由于理想运放A,,即两输入端间电压约为零,可近似视为短路,称为“虚短”. 已知下图,求输出电压。 理论分析: 由题意可得:(列节点方程) 011(1)822A U U +-= 0111 ()0422 B U U +-= A B U U = 解得: 三、 电路设计内容与步骤 如上图所示设计仿真电路. 仿真电路图: V18mV R11Ω R22Ω R32Ω R44Ω U2 DC 10MOhm 0.016 V + - U3 OPAMP_3T_VIRTUAL U1 DC 10MOhm 0.011 V + - 根据电压表的读数,, 与理论结果相同. 但在试验中,要注意把电压调成毫伏级别,否则结果误差会很大, 致结果没有任何意义。如图所示,电压单位为伏时的仿真结 果:V18 V R11Ω R22Ω R32Ω R44Ω U2 DC 10MOhm 6.458 V + - U3 OPAMP_3T_VIRTUAL U1 DC 10MOhm 4.305 V + - ,与理论结果相差甚远。 四、 实验注意事项 1)注意仿真中的运算放大器一般是上正下负,而我们常见的运放是上负下正,在仿真过程中要注意。 课程设计任务书 学生姓名:助人为乐专业班级:不计得失 指导教师:一定过工作单位:信息工程学院 题目: 二输入数据选择器版图设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务: 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件软件。 (2)设计一个二输入数据选择器电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对二输入数据选择器电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日 目录 1.绪论 (2) 2.软件简介 (3) 2.1Cadence简介 (3) 2.2L-edit简介 (3) 3.二输入多路选择器电路设计及仿真 (4) 3.1数据选择器原理 (4) 3.2电路原理图的绘制 (5) 3.3电路图仿真 (6) 4.集成电路版图设计 (7) 4.1CMOS数字电路基本单元版图设计 (7) 4.1.1反相器版图设计 (7) 4.1.2与非门版图设计 (8) 4.2整体版图设计 (9) 4.3设计规则的验证及结果 (9) 5.总结 (10) 参考文献 (11) 8选1数据选择器74LS151 简介 74LS151是一种典型的集成电路数据选择器,为互补输出的8选1数据选择器,它有3个地址输入端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。 74LS151引脚图 选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。 (1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。 (2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。 如:CBA=000,则选择D0数据到输出端,即Y=D0。 如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。 74LS151功能表 数据选择器的应用 数据选择器除实现有选择的传送数据外,还有其他用途,下面介绍几种典型应用。 (1)逻辑函数产生器 从74LS151的逻辑图可以看出,当使能端G=0时,Y是C、B、A和输入数据D0~D7的与或函数。 式中mi是C、B、A构成的最小项。显然。当Di=1时,其对应的最小项mi在与或表达式中出现,当Di=0时,对应的最小项就不出现。利用这一点,不难实现组合逻辑函数。 已知逻辑函数,利用数据选择器构成函数产生器的过程是,将函数变换成最小项表达式,根据最小项表达式确定各数据输入端的二元常量。将数据选择器的地址信号C、 B、A作为函数的输入变量,数据输入D0~D7,作为控制信号,控制各最小项在输出 逻辑函数中是否出现,使能端G始终保持低电平,这样8选1数据选择器就成为一个3变量的函数产生器。 IC课程设计论文题目:运算放大器电路的设计 2012/1/5 摘要 本次课程设计主要内容为:利用MOS管设计一个运算放大器。放大器具有放大小信号并抑制共模信号的功能。首先从放大器理论参数及结构下手,然后经过Hspice网表的生成及仿真调整最后得到满足参数要求的MOS管设定。 关键词:运算放大器,共模电压,电压摆幅,功耗电流 Hspice仿真,增益带宽 ABSTRACT The main content of course design for: use the design a MOS operational amplifier. Amplifier has put size and control signal common mode signal function. Starting from the first amplifier parameters and structure theory laid a hand on him, and then after the formation of the Hspice nets table and adjust the final simulation parameters of the requirements to meet the MOS set. K eywords: operational amplifier ,common-mode voltage ,voltage swing current consumption ,Hspice simulation ,Gain bandwidth 1.4’b1001<<2=(6‘b100100),4’b1001>>2=(4’b0010 )。 2、完整的条件语句将产生(组合逻辑电路)电路,不完整的条件语句将产生(时序逻辑电路)电路。 3、用EDA技术进行电子系统设计的目标是最终完成(专用集成电路ASIC)的设计。 4、可编程器件分为(现场可编程列阵FPGA)和(复杂可编程逻辑器件 PLD) 5、系统函数和任务函数的首字符标志为($),预编译指令首字符标志为(#)。 6、一个基本的Verilog-HDL程序由(Verilog-HDL )模块构成。 7、EDA技术在应用设计领域主要包含哪四个方面的内容(HDL)、(PLD )、( EDA工具软件)、(EDA开发系统) 8、EDA技术的基本特征主要有哪5个方面:(自顶向下的设计方法)、(采用硬件描述语言)、(高层综合和优化).(并行工程)、(开放性和标准化) 9、当前最流行的并成为IEEE标准的硬件描语言是( VHDI )和( Verilog-HDL) 10、一个完整的Verilog-HDL设计模块包括:(模块关键字和模块名)、(端口列表)、(端口定义)、(功能描述)这4部分。 11Verilog-HDL模块的I/O端口声明用来声明模块端口定义中各端口数据流动方向,包括(输入端口)、(输出端口)、和(双向端口) 12、Verilog-HDL语言的三种常用的模型描述方法为(行为描述)、(数据描述)和(结构描述) 13、Verilog-HDL的数值集合由哪四种基本的值组成( 0)、(1 )、 x)、( z ) 14、10’hxf=( 10’xxxxxx1111 ) 10’hzf=( 10’zzzzzz1111 ) 15、若a=5’b10x01,b=5’b10x01,则a= =b的结果为( X )、a= = =b的结果为( 1 ) 16、Wire[15:0] wire-b表示连线宽度为(16 )位,其最高位为(15),最低位为(0)。 17、若A=5’b11011,B=5’b10101,则有&A=(0)|B=(1) ~A=(5’b00100)A&B(5’b10001) 18、若A=8’b1000_0100则A<<3的结果为(11’b10000100000)A>>3的结果为(8’b00010000) 19、对于Verilog-HDL语言中的关键字,在建模时都必须(小)写。 20、if(a) out1<=int1; else out1<=int2;当a= (1)执行out1<=int1 ;当a=(0)执行out1<=int2 二、选择题: 21、在verilog语言中整型数据与( C )位寄存器数据在实际意义上是相同的。 A、8 B、16 C、32 D、64 22、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C )。 A.FPGA全称为复杂可编程逻辑器件; B.FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 23. 子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化( B )。 ①流水线设计②资源共享③逻辑优化④串行化 ⑤寄存器配平⑥关键路径法 A.①③⑤B.②③④C.②⑤⑥D.①④⑥ 24、下列标识符中,(A)是不合法的标识符。 A、9moon B、State0 C、Not_Ack_0 D、signall 25、下列语句中,不属于并行语句的是:(D ) A、过程语句 B、assign语句 C、元件例化语句 D、case语句 26、在verilog中,下列语句哪个不是分支语句?( D ) A.if-else B、case C、casez D、repeat 27、下列标示符哪些是合法的( B ) A、$time B、_date C、8sum D、mux# 28、如果线网类型变量说明后未赋值,起缺省值是( D ) A、x B、1 C、0 D、z 29、现网中的值被解释为无符号数。在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A ) 成绩评定表 课程设计任务书 摘要 本设计是根据要求进行的集成运算放大器的设计,用Protel软件设计实验电路,并绘制出PCB电路板,根据电路图对设计进行制作,最后进行调试测试。通过对Protel软件的学习与应用,加深对相关原理的理解,并对protel软件有初步的认识和一定的操作能力,为后续相关课程和相关软件的学习与应用打下坚实的基础。并根据通信电子线路所学的知识,掌握电路设计,熟悉电路的制作,运用所学理论和方法进行一次综合性设计训练,从而培养独立分析问题和解决问题的能力。根据相关课题的具体要求,按照指导老师的指导,进行具体项目的设计,提高自己的动手能力和综合水平。 本设计采用LM324芯片,它是一个四运算放大器的基本电路,在四运算放大器电路中起到了至关重要的作用。通过LM324芯片与其他相关电子元件的组合,画出调制与解调电路图,并完成PCB电路的绘制,完成课题的设计,可以算是对自我综合能力的一次有益尝试。 关键字:Protel、PCB、LM324、四运算放大器 目录 1 Protel的简要介绍 (5) 1.1 Protel的发展历史 (5) 1.2 Protel99SE简介 (5) 2 设计任务及要求 (6) 2.1设计任务 (6) 2.2设计要求 (6) 3 电路原理介绍 (7) 3.1 反向运算放大器 (7) 3.2 反向加法器 (7) 3.3 差动运算放大器 (7) 3.4积分器电路 (8) 4 原理图设计 (10) 4.1电路元件明细表 (10) 4.2 绘制原理图 (10) 4.3 元件生成清单 (12) 5 印刷版图的绘制 (12) 5.1 准备电路原理图和网络表 (12) 5.2 创建PCB文件以及网络表的装入 (15) 5.3 元件的布局以及印刷板的布线 (15) 6收获和体会 (16) 7 主要参考文献 (17) 8选1数据选择器74LS151 74LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。 选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。 (1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。838电子(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。 如:CBA=000,则选择D0数据到输出端,即Y=D0。新艺图库 如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。工作原理ab126计算公式大全 74LS151功能表: 在数字系统中,往往要求将并行输出的数据转换成串行输出,用数据选择器很容易完成这种转换。例如将四位的并行数据送到四选一数据选择器的数据端上,然后在A1,A0地址输入端周期性顺序给出00 01 10 11,则在输出端将输出串行数据,不断重复。 数据选择器除了能从多路数据中选择输出信号外,还可以实现并行数据到串行数据的转换,作函数发生器等。 1.逻辑特性 (1) 逻辑功能:从多路输入中选中某一路送至输出端,输出对输入的选择受选择控制量控制。通常,对于一个具有2n路输入和一路输出的多路选择器有n个选择控制变量,控制变量的每种取值组合对应选中一路输入送至输出。 (2) 构成思想: 多路选择器的构成思想相当于一个单刀多掷开关,即 数据选择器的原理 o74LS151为互补输出的8选1数据选择器,引脚排列如图3-2,功能如表3-1。 选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择 一个需要的数据送到输出端Q,为使能端,低电平有效。 图74LS151引脚排列 使能端=1时,不论A2~A0状态如何,均无输出(Q=0,=1),多路开关被禁止。 1)使能端=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7 中某一个通道的数据输送到输出端Q。 如:A2A1A0=000,则选择D0数据到输出端,即Q=D0。 如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推。 数据选择器的定义及功能 数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。实现数据选择功能的逻辑电路称为数据选择器。它的作用相当于多个输入的单刀多掷开关,其示意图如下所示。 下面以4选1数据选择器为例,说明工作原理及基本功能。其逻辑图为: 功能表为: 为了对4个数据源进行选择,使用两位地址码BA产生4个地址信号。由BA等于00、01、10、11分别控制四个与门的开闭。显然,任何时候BA只有一种可能的取值,所以只有一个与门打开,使对应的那一路数据通过,送达Y端。输入使能端G是低电平有效,当G=1时,所有与门都被封锁,无论地址码是什么,Y总是等于0;当G=0时 ,封锁解除,由地址码决定哪一个与门打开。 同样原理,可以构成更多输入通道的数据选择器。被选数据源越多,所需地址码的位数也越多,若地址输入端为N,可选输入通道数为2n。 二、集成电路数据选择器 1.74LS151集成电路数据选择器的功能 74LS151是一种典型的集成电路数据选择器,它有3个地址输入端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。其逻辑图和引脚图分别如下所示:由逻辑图可知,该逻辑电路的基本结构为“与一或一非”形式。输入使能G为低电平有效。输出Y的 《集成电路CAD》课程设计报告 课题:基于Spectre运算放大器的设计 一:课程设计目标及任务 利用Cadence软件设计使用差分放大器,设计其原理图,并画出其版图,模拟器各项性能指标,修改宽长比,使其最优化。 二:运算放大器概况 运算放大器(operational amplifier),简称运放(OPA),如图1.1所示: 图1.1运放示意图 运算放大器最早被设计出来的目的是将电压类比成数字,用来进行加、减、乘、除的运算,同时也成为实现模拟计算机的基本建构方块。然而,理想运算放大器的在电路系统设计上的用途却远远超过加减乘除的计算。今日的运算放大器,无论是使用晶体管或真空管、分立式元件或集成电路元件,运算放大器的效能都已经接近理想运算放大器的要求。早期的运算放大器是使用真空管设计的,现在多半是集成电路式的元件。但是如果系统对于放大器的需求超出集成电路放大器的需求时,常常会利用分立式元件来实现这些特殊规格的运算放大器。 三:原理图的绘制及仿真 3.1原理图的绘制 首先在Cadence电路编辑器界面绘制原理图如下: 图3.1电路原理图 原理图中MOS管的参数如下表: Instance name Model W/m L/m Multiplier Library Cell name View name M1 nmosl 800n 500n 1 Gpdk180 nmos symbol M2 nmosl 800n 500n 1 Gpdk180 nmos symbol M3 pmosl 1.1u 550n 1 Gpdk180 pmos symbol M4 pmosl 1.1u 550n 1 Gpdk180 pmos symbol M5 nmosl 800n 500n 1 Gpdk180 nmos symbol 实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8” 的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在随后弹 出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对话框中 选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命 令保存。 四.综合适配 1.选择Processing =>Start Compilation命令,检查发现无程序语法错误。 2.执行Tools =>Netlist Viewer =>RTL Viewe, 生成RTL图。 五.模拟仿真 1.在 File 菜单下,点击 New 命令。在随后弹出的对话框中,切换到 Other Files 页。选中 Vector Waveform File 选项,点击 OK 按钮。 2.选择命令 Edit=>End Time ,时间设置为30000ns , 进入到波形编辑界 面。在 Edit 菜单下,点击Insert Node or Bus… 命令,或在结点名字区连续双击鼠标左键两次,在新出现的框图中点击Node Finder出现结点查找器窗口搜索结点名, 在上一个框图中点击 Node Finder… 按钮后,打开Node Finder 对话框。点击 List 按钮,列出电路所有的端子。点击 >> 按钮,全部加入。点击 OK 按钮,确认。 3.回到 Insert Node or Bus 对话框,点击 OK 按钮,确认。 4.编辑输入激励信号波形.选中 a 信号,在 Edit 菜单下,选择 Value => Clock… 命令。在随后弹出的对话框的 Period 栏目中设定参数为10ns,点击 OK 按钮,重复前面的操作,设置输入信号b的参数为20ns ,c信号的参数为30ns,d信号的参数为40ns,e信号的参数为50ns,f信号的参数为60ns,g信号的参数为70ns,h信号的参数为80ns,输入激励信号波形编辑完毕。同样的,s[0]、s[1]、s[2]的参数分别设置为10ns、20ns、30ns。 5.功能仿真:(1)Processing=>Generate Functional Simulation Netlist 目录 第1章摘要 (2) 第2章设计目的及设计要求 (2) 第3章基本原理 (2) 3.1 基本文氏振荡器 (2) 3.2 振荡条件 (3) 3.3 振荡频率与振荡波形 (5) 第4章参数设计及运算 (6) 4.1 器件选择 (6) 4.2 参数计算 (6) 4.3 波形仿真图 (9) 第5章结论及误差分析 (13) 心得体会 (14) 参考文献 (15) 第1章摘要 本文中介绍了一种基于运算放大器的文氏电桥正弦波发生器。经测试,该发生器能产生频率为100-1000Hz的正弦波,且能在较小的误差范围内将振幅限制在2.5V以内,通过电位器的调节使频率在100HZ-1000HZ内变化。 无论是从数学意义上还是从实际的意义上,正弦波都是最基本的波形之一——在数学上,任何其他波形都可以表示为基本正弦波的傅里叶组合;从实际意义上来讲,它作为测试信号、参考信号以及载波信号而被广泛的应用。在运算放大电路中,最适于发生正弦波的是文氏电桥振荡器与正交振荡器,本文将对文氏桥振荡器进行讨论。 第2章设计目的及要求 2.1、设计目的: (1).掌握波形产生电路的设计、组装和调试的方法; (2).熟悉集成电路:集成运算放大器LN356N。并掌握其工作原理,组成文氏电桥振路。 2.2、设计要求: (1)设计波形产生电路。 (2)信号频率范围:100Hz——1000Hz。 (3)信号波形:正弦波。 (4)画出波形产生电路原理图,写出终结报告。 第3章基本原理 3.1正弦振荡器的组成 (1)放大电路:放大信号 (2)反馈网络:必须是正反馈,反馈信号即是放大电路的输入信号 (3)选频网络:保证输出为单一频率的正弦波,即使电路只在某一特定频率下满足自激振荡条件 8选1数据选择器74L S15 1 74LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。? 选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。 (1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。838电子(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。 如:CBA=000,则选择D0数据到输出端,即Y=D0。新艺图库 如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。工作原理ab126计算公式大全 74LS151功能表: 在数字系统中,往往要求将并行输出的数据转换成串行输出,用数据选择器很容易完成这种转换。例如将四位的并行数据送到四选一数据选择器的数据端上,然后在A1,A0地址输入端周期性顺序给出00 01 10 11,则在输出端将输出串行数据,不断重复。 数据选择器除了能从多路数据中选择输出信号外,还可以实现并行数据到串行数据的转换,作函数发生器等。 1.逻辑特性 (1) 逻辑功能:从多路输入中选中某一路送至输出端,输出对输入的选择受选择控制量控制。通常,对于一个具有2n路输入和一路输出的多路选择器有n个选择控制变量,控制变量的每种取值组合对应选中一路输入送至输出。 (2) 构成思想: 多路选择器的构成思想相当于一个单刀多掷开关,即 数据选择器的原理 o74LS151为互补输出的8选1数据选择器,引脚排列如图3-2,功能如表3-1。 选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择 一个需要的数据送到输出端Q,为使能端,低电平有效。 课程设计说明书课程名称:音响放大器的设计 专业名称: 学生班级: 学生姓名: 学生学号: 指导老师: 课程设计任务书 设计目的 1)了解集成功率放大器内部电路工作原理 2)掌握其外围电路的设计与主要性能参数测试方法 3)掌握音响放大器的设计方法与电子线路系统的装调技术 设计要求和技术指标 1)技术指标 额定功率P≥0.3W,负载阻抗为10Ω,频率响应范围为50Hz-20KHz,输入阻抗大于20KΩ,放大倍数≥20dB。 2)设计要求 (1)设计话音放大与混合前置放大器、音调控制级、功率放大级; (2)选定元器件和参数,并设计好电路原理图; (3)在万能板或面包板或PCB板上进行电路安装调测; (4)测试输出功率; (5)测试输入阻抗; (6)撰写设计报告。 3)设计扩展要求 (1)能驱动额定功率P≥8W的扬声器; (2)电路电压放大级输出阻抗低,能带500Ω负载。 目录 第1章绪论 (1) 1.1 引言 (1) 1.2 音频功率放大器概述 (1) 1.3 音频功率放大器概述 (2) 第2章音响放大器设计 (3) 2.1 音响放大器简介 (3) 2.2 单元电路的设计 (3) 2.2.1 话音放大器 (3) 2.2.2 混响前置放大器............................................................................... 错误!未定义书签。 2.2.3 电子混响器....................................................................................... 错误!未定义书签。 2.2.4 音调控制器 (5) 2.2.5 功率放大器 (9) 2.3 总电路设计 (9) 第3章电路仿真结果 (13) 3.1 话放与混合级仿真 (13) 3.2 音调控制器的电路仿真 (13) 3.3 功率放大器的电路仿真 (15) 第4章音响放大器的安装与调试 (16) 4.1 电路安装 (16) 4.2 电路调试技术 (16) 4.3 整机功能试听 (17) 第5章心得体会 (18) 参考文献 (19) 附录A 音响放大器元件清单 (19) 附录B PCB板图 (20) DM74150,DM74151A Data Selectors/Multiplexers General Description These data selectors/multiplexers contain full on-chip decod-ing to select the desired data source.The150selects one-of-sixteen data sources;the151A selects one-of-eight data sources.The150and151A have a strobe input which must be at a low logic level to enable these devices.A high level at the strobe forces the W output high and the Y output (as applicable)low. The151A features complementary W and Y outputs, whereas the150has an inverted(W)output only. The151A incorporates address buffers which have sym-metrical propagation delay times through the complementary paths.This reduces the possibility of transients occurring at the output(s)due to changes made at the select inputs,even when the151A outputs are enabled(i.e.,strobe low).Features n150selects one-of-sixteen data lines n151A selects one-of-eight data lines n Performs parallel-to-serial conversion n Permits multiplexing from N lines to one line n Also for use as Boolean function generator n Typical average propagation delay time,data input to W output 15011ns 151A9ns n Typical power dissipation 150200mW 151A135mW n Alternate Military/Aerospace device(54150,54151A)is available.Contact a Fairchild Semiconductor Sales Office/Distributor for specifications. Connection Diagrams Dual-In-Line Package DS006546-1 Order Number54150DQMB,54150FMQB, DM54150J or DM74150N See Package Number J24A,N24A or W24C Dual-In-Line Package DS006546-2 Order Number54151ADMQB,54151AFMQB, DM54151AJ,DM54151AW or DM74151AN See Package Number J16A,N16E or W16A 辽宁工业大学 模拟电子技术基础课程设计(论文)题目:集成运算放大器简易测试仪 院(系):电气工程及其自动化 专业班级:电气092 学号:09030305 学生姓名:李新 指导教师: 起止时间:1111111111111111111 课程设计(论文)任务及评语 院(系):电子与信息工程学院教研室:电子信息工程 摘要 集成运算放大器简易测试仪由四部分组成:直流稳压电源、正弦波产生电路、被测运放电路和毫伏表电路。用于判断集成运算放大器放大功能的好坏。直流稳压电源使正弦波电路和毫伏表电路工作,为集成运放提供偏置电流。本实验涉及集成电路运算放大器的内部组成单元,带有源负载的射极耦合差分式放大电路,利用二极管进行偏置的互补对称电路.正弦波信号经集成运放放大后,放大A倍,毫伏表测出其电压最大值并与正弦波产生的信号最大值比较,若他们满足A倍的关系,则能测试出此集成运放能正常工作,否则不能 关键词:偏置电流;恒流源;毫伏表电路;反馈。 目录 第1章绪论 (4) 1.1集成运算放大器的应用意义 (4) 1.2课程技术要求 (4) 第2章总体设计方案框图及其方案论证 (5) 2.1方案论证 (5) 2.2 总体设计方案及分析 (5) 第3章单元电路设计 (7) 3.1正弦波产生电路 (7) 3.2 集成电路放大器 (8) 3.3直流稳压电源 (8) 第4章集成运算放大器简易测试仪整体电路设计 (10) 4.1 整体电路及原理 (10) 4.2电路参数设计 (10) 第5章设计总结 (12) 参考文献 (13) 附录1原理图 (14) 附录2元件表 (14) 《模拟电路》课程设计报告运算放大器组成函数信号发生器 设计时间2008年1月 目录 一、设计任务与要求 (2) 二、方案设计 (3) 三、各部分电路设计 (4) 四、总原理图 (9) 五、安装与调试 (10) 六、电路的实验结果 (12) 七、实验心得 (14) 八、参考文献 (14) 一、设计任务与要求 1.1.设计目的 1.掌握电子系统的一般设计方法 2.掌握模拟IC器件的应用 3.培养综合应用所学知识来指导实践的能力 4.掌握常用元器件的识别和测试 5.熟悉常用仪表,了解电路调试的基本方法 1.2.设计任务 运算放大器设计方波——三角波——正弦波函数信号发生器1.3.课程设计的要求及技术指标 1.设计、组装、调试函数发生器 2.输出波形:正弦波、方波、三角波; 3.频率范围:在10-10000Hz范围内可调; 4.输出电压:方波U P-P≤24V,三角波U P-P =8V,正弦波U P-P >1V; 二、方案设计 2.1. 原理框图 2.2.函数发生器的总方案 函数发生器一般是指能自动产生正弦波、三角波、方波及锯齿波、阶梯波等电压波形的电路或仪器。根据用途不同,有产生三种或多种波形的函数发生器,使用的器件可以是分立器件 (如低频信号函数发生器S101全部采用晶体管),也可以采用集成电路(如单片函数发生器模块8038)。为进一步掌握电路的基本理论及实验调试技术,本课题采用由集成运算放大器与晶体管差分放大器共同组成的方波—三角波—正弦波函数发生器的设计方法。 产生正弦波、方波、三角波的方案有多种,如首先产生正弦波,然后通过整形电路将正弦波变换成方波,再由积分电路将方波变成三角波;也可以首先产生三角波—方波,再将三角波变成正弦波或将方波变成正弦波等等。本课题采用先产生方波—三角波,再将三角波变换成正弦波的电路设计方法。 本课题中函数发生器电路组成框图如下所示: 由比较器和积分器组成方波—三角波产生电路,比较器输出的方波经积分器得到三角波,三角波到正弦波的变换电路主要由差分放大器来完成。差分放大器具有工作点稳定,输入阻抗高,抗干扰能力较强等优点。特别是作为直流放大器时,可以有效地抑制零点漂移,因此可将频率很低的三角波变换成正弦波。波形变换的原理是利用差分放大器传输特性曲线的非线性。 FPGA实验报告 姓名朱聪聪学号 39 姓名武帅学号 课 题 名 称 8选1数据选择器设计 实验目的1、理解数据选择器功能。 2、掌握VHDL并行语句中条件信号赋值的格式和用法。 设计要求 设计一个8选1数据选择器使其满足如下真值表: 8选1数据选择器真值表 地址码(选择信号)输出Q A0 A1 A2 0 0 0 D0 0 0 1 D1 0 1 0 D2 0 1 1 D3 1 0 0 D4 1 0 1 D5 1 1 0 D6 1 1 1 D7 表一 1.利用条件信号赋值语句实现8选1数据选择器器功能。 2.完成设计的仿真,并记录、分析仿真波形。 设计思路 条件信号赋值语句也是一种并行信号赋值语句。条件信号赋值语句可以根据不同的条件将不同的表达式赋值给目标信号,格式如下: 信号<=表达式1WHEN 赋值条件1ELSE 表达式2WHEN 赋值条件2ELSE …… 表达式n; 设计原理图及源程序LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX8 IS PORT(D:IN STD_LOGIC_VECTOR(7 DOWNTO 0); A:IN STD_LOGIC_VECTOR(2 DOWNTO 0); Q:OUT STD_LOGIC); END ENTITY MUX8; ARCHITECTURE one OF MUX8 IS BEGIN Q<=D(0) WHEN A="000" ELSE D(1) WHEN A="001" ELSE D(2) WHEN A="010" ELSE D(3) WHEN A="011" ELSE D(4) WHEN A="100" ELSE D(5) WHEN A="101" ELSE D(6) WHEN A="110" ELSE D(7) WHEN A="111" ELSE 'Z'; END one; 目录 1 版图设计概要 (1) 2 数据选择器简介 (2) 3 八选一数据选择器的设计 (4) 4 各模块设计 (6) 4.1五输入与门的设计 (6) 4.2八输入或门的设计 (8) 4.3反相器 (10) 4 实验总结 (12) 参考文献 (13) 巢湖学院11微电子学《集成电路CAD》课程设计 1 版图设计概要 IC(“集成电路”)产业是全球高新技术产业的前沿与核心,是最具活力和挑战性的战略产业。自2000年来,在国家政策的大力支持下,我国集成电路产业得到了长足的发展,而作为集成电路产业最前沿的设计业更是呈现出“百花齐放”的繁荣景象,作为产业命脉的IC设计人才,在IC产业最集中的长三角地区也仅仅只有几千人。所以拥有一定工作经验的设计工程师,据国内知名猎头公司烽火猎聘公司数据显示IC已成为人才猎头公司争相角逐的“宠儿”。 IC版图设计是指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程。其主要工作职责有:芯片物理结构分析、逻辑分析、建立后端设计流程、版图布局布线、版图编辑、版图物理验证、联络代工厂并提交生产数据。作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。 版图设计在大学阶段课程教学使用软件为Tanner该软件有L-Edit、S-Edit、T-Spice、W-Edit和LVS组成。 Tanner集成电路设计软件是由Tanner Research公司开发的基于Windows平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-EditPro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计版图的系统。八选一数据选择器

八选一数据选择器和四位数据比较器verilog实验报告)

运算放大器的电路仿真设计

2输入数据选择器(mux2)集成电路课设报告

数字电子技术基础实验-8选1数据选择器74LS151

运算放大器。ic设计

八选一数据选择器

集成运算放大器

8选1数据选择器74LS151

基于Spectre运算放大器的设计

实验三8选1数据选择器实验报告

基于运算放大器的正弦波发生器

8选1数据选择器74LS151

音响放大器的设计 课程设计DOC

74151 TTL 8选1数据选择器

集成运算放大器的简易测试--模拟电子课程设计改完可教

运算放大器组成函数信号发生器《模拟电路》课程设计报告

fpga选数据选择器

八选一数据选择器