关于同步电路以及亚稳态的讨论

关于同步电路以及亚稳态的讨论

Kesir:

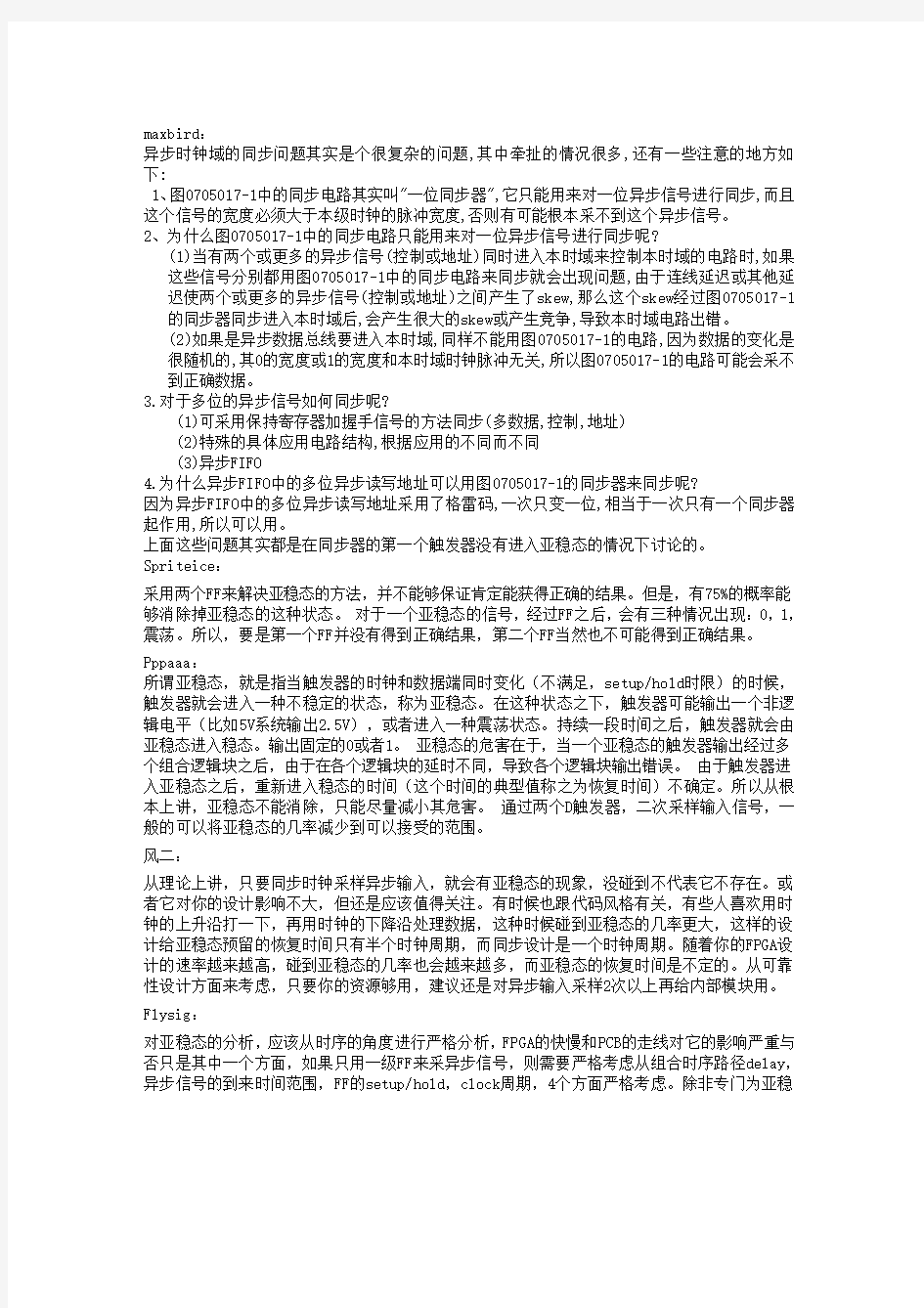

如下图所示的一个同步电路,该电路是用于异步信号的每个pulse至少有1个周期宽度的情况的。其中的第二个Flip-flop图中所说是为了避免亚稳态的发生的,那它应该是如何避免亚稳态的阿?如果输入数字刚好在clk上升沿跳变,FF1的输出是亚稳值,FF2值是不是就维持原值不变阿?如果输入的异步pulse宽度刚好为1个周期呢?

图0705017-1 同步电路设计示意图

evergreen:

对于图0705017-1,是一个典型的对异步信号进行同步的电路。在本论坛中已经有很多帖子提到过。我再重复一下。

“其中的第二个Flip-flop图中所说是为了避免亚稳态的发生的,那它应该是如何避免亚稳态的啊?

答(1)注意,第二个触发器并不是避免“亚稳态的发生”,确切地说,该电路能够防止亚稳态的传播。也就是说,一旦第一个触发器发生了亚稳态(可能性存在),由于有了第二个触发器,亚稳态不会传播到第二个触发器以后的电路中去。

(2)第一级触发器发生了亚稳态,需要一个恢复时间来稳定下来,或者叫退出亚稳态。当恢复时间加上第二级触发器的建立时间(更精确的,还要减去clock skew)小于等于时钟周期的时候(这个条件还是很容易满足的,一般要求两级触发器尽量接近,中间没有任何组合逻辑,时钟的skew较小),第二级触发器就可以稳定的采样,得到稳定的确定的数据了,防止了亚稳态的传播。

“FF1的输出是亚稳值,FF2值是不是就维持原值不变啊?”

答:FF2是采样了FF1的输出,当然是FF1输出什么,FF2就输出什么。仅仅延迟了1个周期。注意,亚稳态之所以叫做亚稳态,是指一旦FF1进入,其输出电平不定,可能正确也可能错误。所以必须说明的是,虽然这种方法可以防止亚稳态的传播,但是并不能保证两级触发器之后的数据是正确的,因此,这种电路都有一定数量的错误电平数据,所以,仅适用于少量对于错误不敏感的地方。对于敏感的电路,可以采用双口RAM或FIFO。

楼主的题目中说“如图所示的一个同步电路,该电路是用于异步信号的每个pulse至少有1

个周期宽度的情况的。” 更确切地说,输入脉冲宽度必须大于同步时钟周期与第一级触发器所需的保持时间之和。最保险的脉冲宽度是两倍同步时钟周期。 所以,这样的同步电路对于从较慢的时钟域来的异步信号进入较快的时钟域比较有效,对于进入一个较慢的时钟域,则没有作用

亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。当一个触发器进入亚稳态时,即无法预测该输出电平,也无法预测何时输出才能稳定在某个电平上。在这期间,触发器输出一些中间电平,或者可能出于振荡状态。

maxbird:

异步时钟域的同步问题其实是个很复杂的问题,其中牵扯的情况很多,还有一些注意的地方如下:

1、图0705017-1中的同步电路其实叫"一位同步器",它只能用来对一位异步信号进行同步,而且这个信号的宽度必须大于本级时钟的脉冲宽度,否则有可能根本采不到这个异步信号。

2、为什么图0705017-1中的同步电路只能用来对一位异步信号进行同步呢?

(1)当有两个或更多的异步信号(控制或地址)同时进入本时域来控制本时域的电路时,如果

这些信号分别都用图0705017-1中的同步电路来同步就会出现问题,由于连线延迟或其他延迟使两个或更多的异步信号(控制或地址)之间产生了skew,那么这个skew经过图0705017-1的同步器同步进入本时域后,会产生很大的skew或产生竞争,导致本时域电路出错。

(2)如果是异步数据总线要进入本时域,同样不能用图0705017-1的电路,因为数据的变化是

很随机的,其0的宽度或1的宽度和本时域时钟脉冲无关,所以图0705017-1的电路可能会采不到正确数据。

3.对于多位的异步信号如何同步呢?

(1)可采用保持寄存器加握手信号的方法同步(多数据,控制,地址)

(2)特殊的具体应用电路结构,根据应用的不同而不同

(3)异步FIFO

4.为什么异步FIFO中的多位异步读写地址可以用图0705017-1的同步器来同步呢?

因为异步FIFO中的多位异步读写地址采用了格雷码,一次只变一位,相当于一次只有一个同步器起作用,所以可以用。

上面这些问题其实都是在同步器的第一个触发器没有进入亚稳态的情况下讨论的。 Spriteice:

采用两个FF来解决亚稳态的方法,并不能够保证肯定能获得正确的结果。但是,有75%的概率能够消除掉亚稳态的这种状态。 对于一个亚稳态的信号,经过FF之后,会有三种情况出现:0,1,震荡。所以,要是第一个FF并没有得到正确结果,第二个FF当然也不可能得到正确结果。

Pppaaa:

所谓亚稳态,就是指当触发器的时钟和数据端同时变化(不满足,setup/hold时限)的时候,触发器就会进入一种不稳定的状态,称为亚稳态。在这种状态之下,触发器可能输出一个非逻辑电平(比如5V系统输出2.5V),或者进入一种震荡状态。持续一段时间之后,触发器就会由亚稳态进入稳态。输出固定的0或者1。 亚稳态的危害在于,当一个亚稳态的触发器输出经过多个组合逻辑块之后,由于在各个逻辑块的延时不同,导致各个逻辑块输出错误。 由于触发器进入亚稳态之后,重新进入稳态的时间(这个时间的典型值称之为恢复时间)不确定。所以从根本上讲,亚稳态不能消除,只能尽量减小其危害。 通过两个D触发器,二次采样输入信号,一般的可以将亚稳态的几率减少到可以接受的范围。

风二:

从理论上讲,只要同步时钟采样异步输入,就会有亚稳态的现象,没碰到不代表它不存在。或者它对你的设计影响不大,但还是应该值得关注。有时候也跟代码风格有关,有些人喜欢用时钟的上升沿打一下,再用时钟的下降沿处理数据,这种时候碰到亚稳态的几率更大,这样的设计给亚稳态预留的恢复时间只有半个时钟周期,而同步设计是一个时钟周期。随着你的FPGA设计的速率越来越高,碰到亚稳态的几率也会越来越多,而亚稳态的恢复时间是不定的。从可靠性设计方面来考虑,只要你的资源够用,建议还是对异步输入采样2次以上再给内部模块用。

Flysig:

对亚稳态的分析,应该从时序的角度进行严格分析,FPGA的快慢和PCB的走线对它的影响严重与否只是其中一个方面,如果只用一级FF来采异步信号,则需要严格考虑从组合时序路径delay,异步信号的到来时间范围,FF的setup/hold,clock周期,4个方面严格考虑。除非专门为亚稳

态进行一些特殊实验(IEEE有大量文章),应用开发人员想要直接看到亚稳态的现象是极困难的。而要判断是否有亚稳态的问题,只有具体问题,具体分析了,当然排除法是最简单可行的。亚稳态是客观存在的,而且会对系统可靠性影响较大,当然,从实际的角度而言,要统计出影响程度也是较困难的,但遵循一个好的原则是确保你的设计优秀的重要保障(the art of design)。,ASIC和FPGA设计中经常建议不用异步复位,我认为主要原因就在于此,(当然解决办法也是有的,即两个FF实现异步复位同步化),对多时钟域的信号处理,也存在此问题,如楼主所讨论。解决方法,风二兄已经指明,这也是最可简单可靠的方法。

Pppaaa:

首先,亚稳态恢复成稳态的过程。众所周知,触发器的构造是一个反馈电路,因此亚稳态恢复到稳态的时间特性,又两个参数来确定,第一,反馈电路一次反馈的时间T0。第二,一次反馈之后仍然保留在亚稳态的几率P0。这样子经过时间t之后,留在亚稳态的几率为P=P0^(t/t0)。

从这个方程,可以看出,无论经过多长时间,亚稳态都仍有忧一定的几率停留在亚稳态,也就是说,亚稳态问题不可能彻底避免。而且有3个途径来降低,

1.改变器件的工艺,以改变输入输出电压特性为目标,从而改变P0;

2.加快器件速度,减少传播延时,从而降低t0。

3.在使用可能进入亚稳态的D触发器信号之前,等待更长的时间。

从而有下面进一步的结论,

1.考虑组合,路径延时,用两个触发器同步,效果不会比时钟频率降低为1/2更有效。

2.改变pcb的布线不会对亚稳态产生任何影响。

3.亚稳态对温度影响特别敏感,因为t0对温度很敏感。

下面回到FPGA中同步的问题,如果一个人做了一个200M的设计,用了两个触发器来同步,那么,效果比不上一个人100M的设计,却只用了一个触发器同步。(以上假设异步信号使用时的组合延迟相同)

材料亚稳态

第9章材料的亚稳态 材料的稳定状态是指其体系自由能最低时的平衡状态,通常相图中所显示的即是稳定的平衡状态。但由于种种因素,材料会以高于平衡态时自由能的状态存在,处于一种非平衡的亚稳态。同一化学成分的材料,其亚稳态时的性能不同于平衡态时的性能,而且亚稳态可因形成条件的不同而呈多种形式,它们所表现的性能迥异,在很多情况下,亚稳态材料的某些性能会优于其处于平衡态时的性能,甚至出现特殊的性能。因此,对材料亚稳态的研究不仅有理论上的意义,更具有重要的实用价值。 材料在平衡条件下只以一种状态存在,而非平衡的亚稳态则可出现多种形式,大致有以下几种型: 1).细晶组织。当组织细小时,界面增多,自由能升高,故为亚稳状态。其中突出的例子是超细的纳米晶组织,其晶界体积可占材料总体积的50%以上; 2).高密度晶体缺陷的存在。晶体缺陷使原子偏离平衡位置,晶体结构排列的规则性下降,故体系自由能增高。另外,对于有序合金,当其有序度下降,甚至呈无序状态(化学无序)时,也使自由能升高; 3).形成过饱和固溶体。即溶质原子在固溶体中的浓度超过平衡浓度,甚至在平衡状态是互不溶解的组元发生了相互溶解; 4).发生非平衡转变,生成具有与原先不同结构的亚稳新相,例如钢及合金中的马氏体。贝氏体,以及合金中的准晶态相等; 5).由晶态转变为非晶态,由结构有序变为结构无序,自由能增高。 9.1纳米晶材料 霍尔—佩奇(Hall-Petch)公式指出了多晶体材料的强度与其晶粒尺寸之间的关系,晶粒越细小则强度越高。但通常的材料制备方法至多只能获得细小到微米级的晶粒,霍尔—佩奇公式的验证也只是到此范围。如果晶粒更为微小时,材料的性能将如何变化?制得这种超细晶材料,是一个留待解决的问题。自20世纪80年代以来,随着材料制备新技术的发展,人们开始研制出晶粒尺寸为纳米(nm)级的材料,并发现这类材料不仅强度更高(但不符合霍尔一佩奇公式),其结构和各种性能都具有特殊性,引起了极大的兴趣和关注。纳米晶材料(或称纳米结构材料)已成为国际上发展新材料领域中的一个重要内容,并在材料科学和凝聚态物理学科中引出了新

关于亚稳态

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。 1.亚稳态发生的原因 在同步系统中,如果触发器的setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。这段之间成为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是究竟是0还是1,这是随机的,与输入没有必然的关系。 2.亚稳态的危害 由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。逻辑误判有可能通过电路的特殊设计减轻危害(如异步FIFO中Gray码计数器的作用),而亚稳态的传播则扩大了故障面,难以处理。 3.亚稳态的解决办法 只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致错误的发生,其次要使系统对产生的错误不敏感。前者要*同步来实现,而后者根据不同的设计应用有不同的处理办法。用同步来减少亚稳态发生机会的典型电路如图1所 示。 左边为异步输入端,经过两级触发器同步,在右边的输出将是同步的,而且该输出基本不存在亚稳态。其原理是即使第一个触发器的输出端存在亚稳态,经过一个CLK周期后,第二个触发器D端的电平仍未稳定的概率非常小,因此第二个触发器Q端基本不会产生亚稳态。注意,这里说的是―基本‖,也就是无法―根除‖,那么如果第二个触发器Q出现了亚稳态会有什么后果呢?后果的严重程度是有你的设计决定的,如果系统对产生的错误不敏感,那么系统可能正常工作,或者经过短暂的异常之后可以恢复正常工作,例如设计异步FIFO时使用格雷码计数器当读写地址的指针就是处于这方面的考虑。如果设计上没有考虑如何降低系统对亚稳态的敏感程度,那么一旦出现亚稳态,系统可能就崩溃了。 4 亚稳态与系统可靠性 使用同步电路以后,亚稳态仍然有发生的可能,与此相连的是平均故障间隔时间MTBF(mean time between failure),亚稳态的发生概率与时钟频率无关,但是MTBF与时钟有密切关系。有文章提供了一个例子,某一系统在20MHz 时钟下工作时,MTBF约为50年,但是时钟频率提高到40MHz 时,MTBF 只有1 分钟!可见降低时钟频率可以大大减小亚稳态导致系统错误的出现,其原因在于,时钟周期如果尽可能的大于resolution time 可减小亚稳态传递到下一级的机会,可提高系统的MTBF,

理解FPGA中的亚稳态

理解FPGAs中的亚稳态 这篇论文描述了在FPGA中的亚稳态,它是怎样产生的,还有它是怎样导致设计的失败。介绍了如何计算亚稳态的平均无故障时间(MTBF),并且总结了各种器件和设计参数是如何影响平均无故障时间的。 介绍 亚稳态是当信号在无关的电路中或异步时钟域之间传输时导致数字器件包括FPGA系统失效的一种现象。这篇论文描述了FPGA中的亚稳态,解释了它是如何发生的,并讨论了它是如何导致设计失败的。 由亚稳态得出的平均无故障时间可以告诉设计者是否应该去降低出现失效的几率。这篇论文将告诉你如何由各种设计和器件参数计算出平均无故障时间,FPGA供应商和设计者是如何提高平均无故障时间的。通过一些设计技巧和优化降低亚稳态造成的失效,系统可靠性是可以提高的。 什么是亚稳态 在所有的数字器件如FPGA中的寄存器都定义了一个信号时序要求,满足了这个要求寄存器才可以正确地在输入端获取(capture)数据在输出端产生数据。为了确保可靠的操作,输入信号在时钟沿之前必须稳定一段时间(寄存器建立时间Tsu)并且在时钟沿之后稳定一段时间(寄存器保持时间Th),然后寄存器输出经过一个特定的时钟到输出延时(clock to output ,Tco)后有效。如果一个数据信号在翻转中违反了一个寄存器的建立和保持时间的要求,寄存器的输出可能就会是亚稳态。在亚稳态中,寄存器的输出值在高和低之间徘徊一段时间,这就意味着输出翻转到一个确定的高或低的延时会超过固定的时钟到输出延时。 在同步系统中,输入信号必须总是满足寄存器时序要求,所以亚稳态不会发生。亚稳态问题通常发生在当一个信号在无关的线路中或异步时钟域中传输。在这种情况下设计者不能保证信号会满足建立时间(Tsu)和保持时间(Th)的要求,因为相对于目标时钟信号可以在任何时间到达。但是,不是每个违反寄存器建立保持时间的信号翻转都会导致亚稳态。一个寄存器进入亚稳态和从亚稳态进入稳态的时间依赖于制造商的制造工艺和使用环境。大部分情况下,寄存器会很快的进入一个定义的稳态中。 一个寄存器在时钟边沿取样一个数据信号可以形象地比喻成往一个小丘上抛球,如图1所示。这个小丘的每一侧代表一个稳态——信号翻转后的新旧数据值——小丘的顶部代表亚稳态,球可能会平衡在这儿,但在实际中它会慢慢地滑向(falls slightly)一侧。球落的离丘顶部越远,它就越快地到达在底部达到稳态。(The further the ball lands from the top of the hill, the faster it reaches a stable state at the bottom.) 如果一个数据信号在时钟边沿之后不超过最小保持时间之内翻转,类似于球落在小丘的“旧数据”端,对于这次时钟翻转输出信号仍旧保持原始值。当一个寄存器的数据输入在时钟沿的最小建立时间之前翻转并且保持超过最小建立时间,这类似于球落在小丘的 “新数据”端,输出很快的达到一个新问题以满足Tco的定义。然而当一个寄存器的数据输入违反了建立和保持时间,这类似于球落在了丘的顶部。如果球落在丘顶部附近,球将花费很长时间去到达底部,这将增大从时钟到输出的延迟并超过定义的Tco。 图1 亚稳态抛球图示

亚稳态(@)

基于FPGA的跨时钟域信号处理——亚稳态 所有数字器件(例如FPGA)的信号传输都会有一定的时序要求,从而保证每个寄存器将捕获的输入信号正确输出。为了确保可靠的操作,输入寄存器的信号必须在时钟沿的某段时间(寄存器的建立时间Tsu)之前保持稳定,并且持续到时钟沿之后的某段时间(寄存器的保持时间Th)之后才能改变。而该寄存器的输入反映到输出则需要经过一定的延时(时钟到输出的时间Tco)。如果数据信号的变化违反了Tsu后者Th的要求,那么寄存器的输出就会处于亚稳态。此时,寄存器的输出会在高电平1和低电平0之间盘旋一段时间,这也意味着寄存器的输出达到一个稳定的高或者低电平的状态所需要的时间会大于Tco。 在同步系统中,输入信号总是能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生在一些跨时钟域信号的传输上。由于数据信号可能在任何时间到达异步时钟域的目的寄存器,所以设计者无法保证满足Tsu和Th 的要求。然而,并非所有违反寄存器的Tsu或Th要求的信号会导致输出亚稳态。某个寄存器进入了亚稳态后重新回到稳定状态的时间取决于器件的制造工艺及工作环境。在大多数情况下,寄存器将会快速的返回稳定状态。 寄存器在时钟沿采样数据信号好比一个球从小山的一侧抛到另一侧。如图1所示,小山的两侧代表数据的稳定状态——旧的数据值或者新的数据值;山顶代表亚稳态。如果球被抛到山顶上,它可能会停在山顶上,但实际上它只要稍微有些动静就会滚落到山底。在一定时间内,球滚的越远,它达到稳定状态的时间也就越短。 如果数据信号的变化发生在时钟沿的某段时间之后(Th),就好像球跌落到了小山的“old data value”一侧,输出信号仍然保持时钟变化前的值不变。如果数据信号的变化发生在时钟沿的某段时间(Tsu)之前,并且持续到时钟沿之后的某段时间(Th)都不再变化,那就好像球跌落到了小山的“new data value”一侧,输出数据达到稳定状态的时间为Tco。然而,当一个寄存器的输入数据违反了Tsu或者Th,就像球被抛到了山顶。如果球在山顶停留的越久,那么它到达山底的时间也就越长,这就相应的延长了从时钟变化到输出数据达到稳定状态的时间(Tco)。

材料科学基础-材料的亚稳态

材料科学基础-材料的亚稳态 (总分:180.00,做题时间:90分钟) 一、论述题(总题数:18,分数:180.00) 1.从内部微观结构角度简述纳米材料的特点。 (分数:10.00) __________________________________________________________________________________________ 正确答案:(纳米材料是指在三维空间中至少有一维处于纳米尺度范围或由它们作为基本单元构成的性能有突变的材料。按维数分,纳米材料的基本单元可分为3类:(1)零维,指在空间三维尺寸均处在纳米尺度,如纳米粉体材料;(2)一维,指在空间有二维处于纳米尺度,如纳米丝、纳米棒、纳米管等;(3)二维.指在三维空间中有一维处在纳米尺度,如超薄膜、多层膜、超晶格等。 由于纳米微粒的超细尺寸,它与光波波长、中子波长、平均自由程等为同一数量级,因此量子尺寸效应、小尺寸效应、表面效应、宏观量子隧穿效应,以及体积分数超过50%晶界结构的影响使纳米材料呈现出特殊的力学、物理和化学性能。) 解析: 2.试分析的Ni3Al粒子尺寸对Ni-Al合金流变应力影响的作用机制。 (分数:10.00) __________________________________________________________________________________________ 正确答案:(此例中的Ni3Al纳米颗粒是作为第二相分布于基体中的,故应以第二相微粒的弥散强化机制来分析之。) 解析: 3.说明晶体结构为何不存在5次或高于6次的对称轴? (分数:10.00) __________________________________________________________________________________________ 正确答案:(5次或高于6次对称轴不能满足阵点周围环境相同的条件,不具有平移对称性,不能实现有规则周期排列的晶体结构。) 解析: 4.何谓准晶?如何描绘准晶态结构? (分数:10.00) __________________________________________________________________________________________ 正确答案:(准晶系不具有平移对称性,然而是呈一定周期性有序排列的类似于晶态的一种原子聚集态固体。在三维空间中,它们除了具有5次对称轴外,还有8,10或12次对称轴,其衍射花样呈现出非晶体学对称性。大多数准晶相是亚稳的,只能用快速凝固的方法获得。众所周知,用正三角形、正方或正六边形可做平面的周期拼砌,然而用正五边形来拼砌,不能无重叠或无任何间隙铺满整个平面。因此,准晶态结构不能如同晶体那样取一个晶胞来代表其结构,即无法通过平移操作实现周期性。目前较常用的是拼砌花砖方式的模型来表征准晶结构。例如:5次对称的准周期结构可用边长相等、角度分别为36°和144°(窄),以及72°和108°(宽)的两种菱形,遵照特别的匹配法将其构造出来。) 解析:

建立时间和保持时间和亚稳态之类一直都是概念类题的经典

建立时间和保持时间和亚稳态之类一直都是概念类题的经典! 题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问,触发器D2的建立时间T3和保持时间应满足什么条件。 Tffpd:触发器输出的响应时间,也可以理解为触发器输出在clk上升沿到来后的时间内发生变化, 之后稳定,也可以理解输出延迟。 Tcomb: 触发器输出的变化经过组合逻辑元件所需的附加时间,也就是题目中的组合逻辑延迟 tsetup:建立时间 thold:保持时间 tclk: 时钟周期 建立时间容限:这里用容限的概念是为了数学推导方便,时间容限仅仅是一个概念,在这里我们对建立时间容限的要求是大于0,当然有的地方可能就是小于0了。 同样保持时间容限也是需要大于0的。 从图中,我们可以很清楚的看出,建立时间容限=tclk-tffpd(max)-tcomb(max)-tsetup 这里应该理解到,tffpd和tcomb都是要考虑最大值的那么根据建立时间容限>=0 推导出tsetup<=tclk-tffpd(max)-tcomb(max) 这里,我们是不是很清楚了理解了建立时间的要求是<=T-T2MAX,因为题目中没有考虑 tffpd。 同理,保持时间容限tffpd(min)+tcomb(min)-thold,这里是要取最小值,那么根据保持时间容限>=0推导出thold<=tffpd(min)+tcomb(min) 因为题目中没有考虑tffpd,而tcomb就是t2min,所以thold<=t2min。取最小值的原因就是在延时最小的情况下都应该满足保持时间。否则触发器输入无效。 在这里我们应该发现,从数学上看,虽然既有max又有min,但是thold,和tsetup都是小于最小值,因为tsetup 亚稳态(recovery time) 2009-06-23 22:12 亚稳态:是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态[1]时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。 亚稳态(metastability) 时序电路采用触发器和锁存器作为存储单元,这两种器件都易进入亚稳态[1]。所谓亚稳态是指触发器无法在某个规定的时间段内达到一个可确认的状态。如图1所示,对任何一种触发器,在时钟触发沿前后存在一个小的时间窗口(称为判决窗口,decision window),输入信号在判决窗口内必须保持稳定,否则,触发器就会进入亚稳态,既无法预测该单元的的输出电平,也无法预测何时输出才能稳定在某个电平上。 这个判决窗口由建立时间(setup time)和保持时间(hold time)两部分组成。并 且时间窗口也是多种因素的函数,包括触发器设计、实现技术、运行环境以及无缓冲输出的负载等。输入信号陡峭的边沿可以将此窗口减至最小,随着时钟频率的升高,会出现更多有问题的时间窗口,而随着数据频率的提升,这种窗口的命中概率会增加,即进入亚稳态的概率会增加。 亚稳态不能从根本上消除,但可以通过采取一定的措施使其对电路造成的影响降低。[2]通常我们用故障间隔平均时间(MTBF,mean time between failures)来衡量亚稳态的影响。MTBF越大则说明亚稳态对电路产生地影响越小,反之亦然。如当MTBF等于几十年或者上百年时,我们就认为它对电路的影响基本上可以忽略。实验结果表明:对于输入为异步信号的电路,其MTBF与从亚稳态状态下恢复的时间长度(如图1所示的)有着指数的关系[3]。 2 同步器(synchronizer) 在实际中,我们常用的是采用两级触发器串联的同步器(如图1)[4]。这种用两级触发器串联的同步器亦称为电平同步器(the level synchronizer),它是其他同步器的基础。对于电平同步器,它能将输入第一级触发器的异步电平信号(保险起见,电平信号应保持大于两个同步时钟周期),转换成第二级触发器输出的同步电平信号。第一级触发器对输入的判决时间有整个同步时钟周期的长度。因此,它的MTBF比单触发器的同步器更大,即亚稳态所产生的影响更小,通常是在我们的可以容忍的范围之内。 因此,对于高速率数字电路的同步器,通常采取的策略是用触发器级联来实现时间缓冲,为电路从亚稳态下恢复过来提供时间,即以时间延迟为代价,降低亚稳态的发生对电路的影响。 下面再分别介绍另外两种常用的同步器。 第三章高聚物的相及相转变中的亚稳态现象 (The condensed phase and the sub-stable phase in phase transition of polymers ) §3-1 引言 物质在自然界中存在的相态和相态间的转变是凝聚态物理的核心研究内容,由于发生相转变时材料的性质发生显著变化,因此在材料科学领域研究物质相态和相态间的转变规律具有突出的重要性。 对高分子材料而言,相变显得更加复杂,更加丰富多彩。绪论中已指出,高分子材料比人们常见的物质具有更多的聚集状态,除通常的固态、液态外,还有玻璃态、半结晶态、液晶态、高弹态、粘流态及形形色色的共混-共聚态等。这些状态间的变化规律各不相同。与小分子相比,大分子链有其尺寸、形状及运动形式上的特殊性。大分子链尺寸巨大,分子链形状具有显著各向异性特征,分子运动时间长,松弛慢,松弛运动形式多样化,松弛时间谱宽广。这些特征决定了高分子材料的相转变要比小分子材料“慢”得多。 从宏观上,我们可以运用热力学原理说明相变过程始态和终态的关系,但是相转变过程的快慢却决定于微观分子运动的速度,即主要由动力学因素所决定。大分子整链的“慢”运动特征决定了高分子材料的最终热力学稳定态往往是很难达到的,许多高分子材料的相变过程中存在着各种类型的亚稳定态。由于达到亚稳定态的时间相对来说要“快”得多,又由于亚稳定态也具有相当的稳定性,因此亚稳态成为高分子材料相变过程中一种普遍存在,并能观察到的有趣的物理现象。 半个世纪以来对高分子相变的研究往往只停留在静止态,即只观察其始态和终态,而作为一个动态过程,即对一步一步从无序态(始态)到亚稳态再到有序态(终态)的发展过程却很少了解。因此,了解亚稳态的存在、演变和终结是真正全面认识高分子相变的基础,不仅在高分子凝聚态物理领域开辟了新的学科分支,而且对高分子材料的发展和应用有重要指导作用。 对亚稳态的认识实际上始于19世纪。1873年,van der Walls发现了气-液相变中的亚稳态;1897年Ostwald提出“态定律”,即相变是一步一步从无序态向有序态的发展,第一次描述了中间态的概念。然而在高分子科学中,把亚稳态的概念与相变联系起来是近几年的事情,是程正迪和Keller等人联合提出来的新概念。 本章的目的是运用经典亚稳态和亚稳性的概念和原理,解释聚合物相变中所观察到的亚稳现象。与小分子相比,高分子往往更容易形成亚稳区。复杂的组成、小的相区 1、简介 这篇文章是我对电子设计中,亚稳态问题的一种分析和总结。文章通过对数字电路中器件的工作机制的介绍,引出亚稳态问题的发生机制。并通过对亚稳态问题发生机制的探讨,用以得到一种能够清楚地,有的放矢地解决亚稳态问题的能力。而这种能力,将会成为你作为一个工程师的价值所在。希望通过这个探讨,可以使你设计出属于自己的预防亚稳态的方法。对于常用的预防亚稳态的方法,由于网上已经有大量介绍,并且涉及到具体问题的分析,这里将不做重点介绍。 2、CMOS中的信息保存 Fig. 1. MOS管的电容模型 当一个MOS工艺晶体管被制造之后,在不同极之间,因为介电物质的存在,会形成电容。当晶体管工作时,这些电容会被充/放电。当充放电回路上的R,C有不同取值的时候,回路的时间常数(由RC表示)会不同。 在数字电路中,最简单的结构是反向器(inverter)。在CMOS工艺中,它由一个NMOS加一个PMOS组成。 Fig. 2. 反向器 对于这个反向器,可以简化成由工作电阻Ron,结点电容CL组成的充放电电路。 Fig. 3. 反向器充放电模型 当Inverter输入为0时,PMOS导通,对CL充电,时间由Rp*CL决定 当Inverter输入为1时,NMOS导通,对CL放电,时间由Rn*CL决定 其中CL由P/NMOS的漏极结点上所有相关的电容组成,这是一种近似的计算方法(将分布的电容进行集总)。 CL=Cdb+Cgd(Miller效应)+Cwire+Cg_fanout 从这里我们得到 1,任何信号都需要时间才能从输入端口传递到输出端口。 2,对CL的充放电影响系统的动态(翻转)功耗,如果想降低功耗,可以对不使用的信号添加使能。 3,由于Rp != Rn,所以Rp*CL != Rn*CL,所以rising time != falling time 对于分析亚稳态的问题,只需要记住第一条,任何信号从输入端口传递到输出端口都需要一定的时间。对于任何其他门电路,分析过程都一样。 3、SETUP/HOLD 时间的意义 S/H时间是时序器件的属性。下面我们来说一下,这两个时间是如何产生的。任何器件“原则”上都是电平有效的,边沿触发的器件是一种“把戏”。 首先我们看一下D锁存器。 Fig. 4. D锁存器 真值表: E D Q 0 x PreQ 1 0 0 1 1 1 在数字集成电路中,触发器要满足setup/hold的时间要求。当一个信号被寄存器锁存时,如果信号和时钟之间不满足上面这个要求,输出的值就不确定,并且在位置的时刻会固定到高电平或低电平,这个过程称为亚稳态。 亚稳态必定会发生在异步时钟电路中。 下面是一EETOP的一网友发表的言论: 个人认为,亚稳态不能叫消除,只能说减低发生概率,减低到工程可接受范围!! 措施无非就是: 1、2级缓冲 2、握手信号(总线或者从高频时钟域进入低频时钟域) 3、异步FIFO(利用Gray Code传输地址信号) 《异步时钟亚稳态及FIFO标志位》一文中认为: 亚稳态是不可避免的,但采用以下几种方法可以将其发生的概率降到一个可以接受的程度:1.格雷码编码:写地址/读地址采用格雷码。由实践可知, 同步多个异步输入信号出现亚稳态的概率远远大于同步一个异步信号的概率2.双触发器法:采用触发器来同步异步输入信号, 如图2 中的两级触发器可以将出现亚稳态的概率降低到一个很小的程度。 虽然两级触发器能有效地抑制亚稳态, 但增加了一 级的 D 触发器, 这和格雷码编码法一样会增加版图面积。这种方法在clka 与clkb 的采样周期相差不大的情况下比较适合。 module levesynchronizer(clk,clk2,data1,data2); input clk,clk2; input data1; output reg data2; reg q1,q2; always@(posedge clk) begin q1<=data1; end always@(posedge clk2) begin q2<=q1; end always@(posedge clk2) begin data2<=q2; end//其综合后的电路如下图所示 关于同步电路以及亚稳态的讨论 Kesir: 如下图所示的一个同步电路,该电路是用于异步信号的每个pulse至少有1个周期宽度的情况的。其中的第二个Flip-flop图中所说是为了避免亚稳态的发生的,那它应该是如何避免亚稳态的阿?如果输入数字刚好在clk上升沿跳变,FF1的输出是亚稳值,FF2值是不是就维持原值不变阿?如果输入的异步pulse宽度刚好为1个周期呢? 图0705017-1 同步电路设计示意图 evergreen: 对于图0705017-1,是一个典型的对异步信号进行同步的电路。在本论坛中已经有很多帖子提到过。我再重复一下。 “其中的第二个Flip-flop图中所说是为了避免亚稳态的发生的,那它应该是如何避免亚稳态的啊? 答(1)注意,第二个触发器并不是避免“亚稳态的发生”,确切地说,该电路能够防止亚稳态的传播。也就是说,一旦第一个触发器发生了亚稳态(可能性存在),由于有了第二个触发器,亚稳态不会传播到第二个触发器以后的电路中去。 (2)第一级触发器发生了亚稳态,需要一个恢复时间来稳定下来,或者叫退出亚稳态。当恢复时间加上第二级触发器的建立时间(更精确的,还要减去clock skew)小于等于时钟周期的时候(这个条件还是很容易满足的,一般要求两级触发器尽量接近,中间没有任何组合逻辑,时钟的skew较小),第二级触发器就可以稳定的采样,得到稳定的确定的数据了,防止了亚稳态的传播。 “FF1的输出是亚稳值,FF2值是不是就维持原值不变啊?” 答:FF2是采样了FF1的输出,当然是FF1输出什么,FF2就输出什么。仅仅延迟了1个周期。注意,亚稳态之所以叫做亚稳态,是指一旦FF1进入,其输出电平不定,可能正确也可能错误。所以必须说明的是,虽然这种方法可以防止亚稳态的传播,但是并不能保证两级触发器之后的数据是正确的,因此,这种电路都有一定数量的错误电平数据,所以,仅适用于少量对于错误不敏感的地方。对于敏感的电路,可以采用双口RAM或FIFO。 楼主的题目中说“如图所示的一个同步电路,该电路是用于异步信号的每个pulse至少有1 个周期宽度的情况的。” 更确切地说,输入脉冲宽度必须大于同步时钟周期与第一级触发器所需的保持时间之和。最保险的脉冲宽度是两倍同步时钟周期。 所以,这样的同步电路对于从较慢的时钟域来的异步信号进入较快的时钟域比较有效,对于进入一个较慢的时钟域,则没有作用 亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。当一个触发器进入亚稳态时,即无法预测该输出电平,也无法预测何时输出才能稳定在某个电平上。在这期间,触发器输出一些中间电平,或者可能出于振荡状态。 第 9章 材料的亚稳态 一、简答题 1.亚共析钢TTT 图如图9-1所示,按图中所示的不同冷却和等温方式热处理后,分析其形成的组织并作显微组织示意图。 图9-1 答:(1)α+珠光体(α先形成于γ晶界处); (2)细片珠光体(屈氏体); (3)屈氏体+马氏体(屈氏体先形成于γ晶界处); (4)上贝氏体+马氏体(贝氏体呈羽毛状,从晶界向晶内生长); (5)马氏体组织。 2.w (C )为1.2%钢淬火后获得马氏体和少量残留奥氏体组织,如果分别加热至180℃,300℃和680℃保温2h ,各将发生怎样的变化?说明其组织特征并解释之。 答:180℃回火:马氏体针叶中开始分解出微细碳化物,易浸蚀,呈暗色。 300℃回火:残留奥氏体发生分解,转变成α+细碳化物,马氏体也分解成α+细 碳化物,原马氏体形态不太明显。 680℃回火:碳化物呈粒状分布于铁素体基体中,组织为粒状珠光体。 3.共析钢的奥氏体化有几个主要过程?合金元素对奥氏体化过程有什么影响? 答:共析钢奥氏体化有四个主要过程:奥氏体形成、渗碳体溶解、奥氏体均匀化、晶粒长大。合金元素的主要影响通过碳的扩散体现,碳化物形成元素阻碍碳的扩散,降低奥氏体形成、渗碳体溶解、奥氏体均匀化速度。 4.何谓钢的冷脆性?是怎样产生的?如何防止? 答:(1)随着温度的降低,大多数钢材的强度会有所增加,而韧性下降。金属材料在低温下呈现的脆性称为冷脆性。值得一提的是,具有面心立方晶格结构的奥氏体不会发生低温脆性,而体心立方晶格的铁素体会发生低温脆性。钢材中磷含量的增加会显著增加钢材的冷脆性。 (2)产生原因:磷在纯铁中溶解度高,强度升高,塑韧性降低,钢的脆性转变温度急剧降(低温脆性)。 (3)防止措施:炼钢时控制磷的含量。 5.简述金相显微试样制备步骤。 答:金相显微试样的制备步骤主要包括取样、镶样、磨制、抛光、侵蚀等工序。 (1)取样。显微试样的选取应根据研究的目的,取其具有代表性的部位。确定好部位后就可把试样截下,试样的尺寸通常采用直径Φ12~15mm,高12~15mm的圆柱体或边长12~15mm的方形试样。 试样的截取方法视材料的性质不同而异,软的金属可用手锯或锯床切割,硬而脆的材料(如白口铸铁)则可用锤击打下,对极硬的材料(如淬火钢)则可采用砂轮片切割或电脉冲加工。不论采用那种方法,在切取过程中均不宜使试样的温度过于升高,以免引起金属组织的变化,影响分析结果。 (2)镶样。当试样的尺寸太小(如金属丝、薄片等)时,直接用手来磨制很困难,需要使用试样夹或利用样品镶嵌机,把试样镶嵌在低熔点合金或塑料(如胶木粉、聚乙烯及聚合树脂等)中。 (3)磨制。试样的磨制一般分粗磨和细磨两道工序。粗磨的目的是为了获得一个平整的表面。经粗磨后试样表面虽较平整,但仍还存在有较深的磨痕。细磨的目的就是为了消除这些磨痕,以得到平整而光滑的磨面,为下一步的抛光作好准备。 (4)抛光。细磨后的试样还需进一步抛光。抛光的目的是去除细磨时遗留下来的细微磨痕而获得光亮的镜面。抛光方法一般分为机械抛光、电解抛光和化学抛光三种。 (5)侵蚀。经抛光后的试样若直接放在显微镜下观察,只能看到一片亮光,除某些非金属夹杂物(如MnS及石墨等)外,无法辨别出各种组成物及其形态特征。必须使用浸蚀剂对试样表面进行浸蚀,才能清楚地显示出显微组织的真实情况。 浸蚀方法是将试样磨面浸入浸蚀剂中,或用棉花沾上浸蚀剂擦拭表面。浸蚀时间要适 亚稳态的原理、起因、危害、解决办法及影响和消除仿真详解 1.亚稳态与设计可靠性设计数字电路时大家都知道同步是非常重要的,特别当要输入一个信号到一个同步电路中,但是该信号由另一个时钟驱动时,这是要在接口处采取一些措施,使输入的异步信号同步化,否则电路将无法正常工作,因为输入端很可能出现亚稳态(Metastability),导致采样错误。 下面我们会对亚稳态的原理、起因、危害、解决办法、对可靠性的影响和消除仿真做一些介绍。 2. 什么是亚稳态?亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。 3.亚稳态发生的原因在同步系统中,如果触发器的setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。这段之间成为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是究竟是0还是1,这是随机的,与输入没有必然的关系。 4.亚稳态的危害由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。逻辑误判有可能通过电路的特殊设计减轻危害(如异步FIFO中Gray码计数器的作用),而亚稳态的传播则扩大了故障面,难以处理。 5.亚稳态的解决办法只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致错误的发生,其次要使系统对产生的错误不敏感。前者要同步来实现,而后者根据不同的设计应用有不同的处理办法。用同步来减少亚稳态发生机会的典型电路如图1所示。 在图1中,左边为异步输入端,经过两级触发器同步,在右边的输出将是同步的,而且该 1. 应用背景 1.1 亚稳态发生原因 在FPGA系统中,如果数据传输中不满足触发器的T su和T h不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为决断时间(resolu tion time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。 1.2 亚稳态发生场合 只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。 1.3 亚稳态危害 由于产生亚稳态后,寄存器Q端输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值。在信号传输中产生亚稳态就会导致与其相连其他数字部件将其作出不同的判断,有的判断到“1”有的判断到“0”,有的也进入了亚稳态,数字部件就会逻辑混乱。在复位电路中产生亚稳态可能会导致复位失败。怎么降低亚稳态发生的概率成了FPGA设计需要重视的一个注意事项。 2. 理论分析 2.1 信号传输中的亚稳态 在同步系统中,输入信号总是系统时钟同步,能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生在一些跨时钟域信号传输以及异步信号采集上。 它们发生的原因如下: (1)在跨时钟域信号传输时,由于源寄存器时钟和目的寄存器时钟相移未知,所以源寄存器数据发出数据,数据可能在任何时间到达异步时钟域的目的寄存器,所以无法保证满足目的寄存器Tsu和Th的要求; (2)在异步信号采集中,由于异步信号可以在任意时间点到达目的寄存器,所以也无法保证满足目的寄存器Tsu和Th的要求; 论亚稳态 张善文(20041001096) 摘要:人们习惯上把相变分为一级相变和连续相变。在连续相变的相变点,两相的化学势和化学势的一级偏导数连续,在相变点的每一侧都只能允许一个相存在,而不允许两相共存和亚稳态的存在。但是,对于一级相变,如固相、液相和气相之间的转变存在相变潜热和体积突变,而且可能存在亚稳态。本文讨论的就是液相和气相转变中的亚稳态,一般认为在这个过程中的亚稳态有两个:过饱和蒸气和过热液体。但我认为更准确地说法应该是存在四种亚稳态:过饱和蒸气、过冷气体、过热液体、过稀液体。过饱和蒸气、过冷气体和过热液体、过稀液体的说法又是相对的,在一定情况下过饱和蒸气又可称为过冷气体,过热液体又可称为过稀液体。这些问题在本文中都将给出解释 。 正文: I 液滴和气泡的形成 考虑一个由气液两相构成的孤立系统,当整个系统达到平衡时,两相的温度,压强和化学势分别相等。上述结论成立的条件是气液两相的分界面是平面时,即没有考虑表面相的影响。如果我们考虑液滴在蒸气中的形成或液体中形成气泡的问题时,那么表面相的影响就不可忽略了。下面我们先来考虑液滴在蒸气中的形成问题。 设液滴为α相,蒸气为β相,表面为γ相。在热平衡条件满足的条件(温度不变)下,我们用自由能判据来推求系统的力学平衡条件和相变平衡条件。设想在T、V 不变的条件下,系统发生一个虚变动。在此虚变动中,三相的物质的量,体积和面积分别有δnα,δVα;δnβ,δVβ;δA 的变化(我们把表面理想化为几何面,因此表面相的物质的量为零)。因为系统总的物质的量和总体积保持不变,应有 0n n αβδδ+= 0V V αβδδ+=三相的自由能的变化分别为 F p V u n F p V u n F A ααααα ββββγβ δδδδδδδσδ=?+=?+= 因此,整个系统 自由能的变化是 ()(F F F F p p V u u n αβγ αβααβαδδδδA δδσδ=++=??+?+) 我们假定液滴是球形的 23 244,3 8,4A r V r A r r V r r ππδπδδπδ==== 1、简介 这篇文章是对电子设计中,亚稳态问题的一种分析和总结。文章通过对数字电路中器件的工作机制的介绍,引出亚稳态问题的发生机制。并通过对亚稳态问题发生机制的探讨,用以得到一种能够清楚地,有的放矢地解决亚稳态问题的能力。而这种能力,将会成为你作为一个工程师的价值所在。希望通过这个探讨,可以使你设计出属于自己的预防亚稳态的方法。 2、CMOS中的信息保存 Fig. 1. MOS管的电容模型 当一个MOS工艺晶体管被制造之后,在不同极之间,因为介电物质的存在,会形成电容。当晶体管工作时,这些电容会被充/放电。当充放电回路上的R,C有不同取值的时候,回路的时间常数(由RC表示)会不同。 在数字电路中,最简单的结构是反向器(inverter)。在CMOS工艺中,它由一个NMOS加一个PMOS组成。 Fig. 2. 反向器 对于这个反向器,可以简化成由工作电阻Ron,结点电容CL组成的充放电电路。 Fig. 3. 反向器充放电模型 当Inverter输入为0时,PMOS导通,对CL充电,时间由Rp*CL决定 当Inverter输入为1时,NMOS导通,对CL放电,时间由Rn*CL决定 其中CL由P/NMOS的漏极结点上所有相关的电容组成,这是一种近似的计算方法(将分布的电容进行集总)。 CL=Cdb+Cgd(Miller效应)+Cwire+Cg_fanout 从这里我们得到 1,任何信号都需要时间才能从输入端口传递到输出端口。 2,对CL的充放电影响系统的动态(翻转)功耗,如果想降低功耗,可以对不使用的信号添加使能。 3,由于Rp != Rn,所以Rp*CL != Rn*CL,所以rising time != falling time 亚稳态分析 1,简介 这篇文章是我对电子设计中,亚稳态问题的一种分析和总结。文章通过对数字电路中器件的工作机制的介绍,引出亚稳态问题的发生机制。并通过对亚稳态问题发生机制的探讨,用以得到一种能够清楚地,有的放矢地解决亚稳态问题的能力。而这种能力,将会成为你作为一个工程师的价值所在。希望通过这个探讨,可以使你设计出属于自己的预防亚稳态的方法。对于常用的预防亚稳态的方法,由于网上已经有大量介绍,并且涉及到具体问题的分析,这里将不做重点介绍。 2,CMOS中的信息保存 Fig. 1. MOS管的电容模型 当一个MOS工艺晶体管被制造之后,在不同极之间,因为介电物质的存在,会形成电容。当晶体管工作时,这些电容会被充/放电。当充放电回路上的R,C有不同取值的时候,回路的时间常数(由RC表示)会不同。 在数字电路中,最简单的结构是反向器(inverter)。在CMOS工艺中,它由一个NMOS加一个PMOS组成。 Fig. 2. 反向器 对于这个反向器,可以简化成由工作电阻Ron,结点电容CL组成的充放电电路。 Fig. 3. 反向器充放电模型 当Inverter输入为0时,PMOS导通,对CL充电,时间由Rp*CL决定 当Inverter输入为1时,NMOS导通,对CL放电,时间由Rn*CL决定 其中CL由P/NMOS的漏极结点上所有相关的电容组成,这是一种近似的计算方法(将分布的电容进行集总)。 CL=Cdb+Cgd(Miller效应)+Cwire+Cg_fanout 从这里我们得到 1,任何信号都需要时间才能从输入端口传递到输出端口。 2,对CL的充放电影响系统的动态(翻转)功耗,如果想降低功耗,可以对不使用的信号添加使能。 3,由于Rp != Rn,所以Rp*CL != Rn*CL,所以rising time != falling time 对于分析亚稳态的问题,只需要记住第一条,任何信号从输入端口传递到输出端口都需要一定的时间。对于任何其他门电路,分析过程都一样。 3,SETUP/HOLD 时间的意义 S/H时间是时序器件的属性。下面我们来说一下,这两个时间是如何产生的。 任何器件“原则”上都是电平有效的,边沿触发的器件是一种“把戏”。 首先我们看一下D锁存器。 Fig. 4. D锁存器 在REFPROP中获取亚稳态物性的方法 1.首先简单介绍什么是流体的亚稳态 如下图所示,流体的p-V图上,双节线即为饱和液相线+饱和气相线组成的一条曲线,饱和气、液相线在临界点处汇聚。在双节线曲线左侧为过冷液体,右侧为过热气体。 在双节线内侧有一条旋节线,旋节线与双节线在临界点处交汇。处在双节线和旋节线之间灰色区域的流体状态即为亚稳态,其中左半部分灰色区域内为过热液体(亚稳态液体),液体的温度高于对应压力下的饱和温度,或者说压力低于对应温度下的饱和压力。一般来说液体过热时会气化吸热,因此平衡状态下“过热液体”是不应该存在的,而是变为气体或者气液两相状态。然而在很多非平衡过程中,例如流体快速降压的过程(如超音速喷管),真实的相变速率是有限值,因此会存在一部分液体来不及气化而处于亚稳态。右半部分的灰色区域内为过冷气体(亚稳态气体),原理类似。 2.在REFPROP(演示版本为9.1)中可以手动获取亚稳态流体的物性 例如对于CO2而言,7 MPa对应的饱和温度为301.83 K,此时饱和液、气的密度分别为638.31 kg/m3和304.03 kg/m3,平衡时的状态参数如图 如果液体CO2在302 K下压力下降到7 MPa,那么此时液体CO2为亚稳态(过热)液体,要求此时的过热液体的密度,如果直接在REFPROP中输入302 K和7 MPa,由于302 K > 301.83 K,默认返回的将是过热气体,密度值也是气体的密度295.97 kg/m3 正确的方法是,压力一栏输入7MPa后,在温度一栏输入“>302” 最后再按回车,Quality一栏返回的将是“Metastable”,此时密度是624.36kg/m3,略小于同等压力下饱和液体的密度638.31 kg/m3亚稳态&同步器

高聚物的相及相转变中的亚稳态现象

锁存器与触发器亚稳态的分析,

亚稳态问题

关于同步电路以及亚稳态的讨论

胡赓祥《材料科学基础》(第3版)配套题库(章节题库 材料的亚稳态)【圣才出品】

亚稳态的原理、起因、危害、解决办法及影响和消除仿真详解

FPGA中的亚稳态问题

论亚稳态

FPGA设计中的亚稳态问题研究

亚稳态分析

在REFPROP中获取亚稳态物性的方法