3 MOS电容、亚阈值

3 MOS 电容、亚阈值

陈启武,2014200557

一、亚阈值条件下I D 与V GS 的关系?

答:在MOS 的I-V 特性中,当V GS 略小于V T 时, MOS 管已开始导通,仍会产生一个弱反型层,从而会产生由漏流向源的电流,称为亚阈值导通,而且I D 与V GS 呈指数关系,关系表达式为:

其中,ξ>1是一非理想的因子;I D0为特征电流: ;m 为工艺因子,因此I D0与工艺有关;而V T 称为热电压:

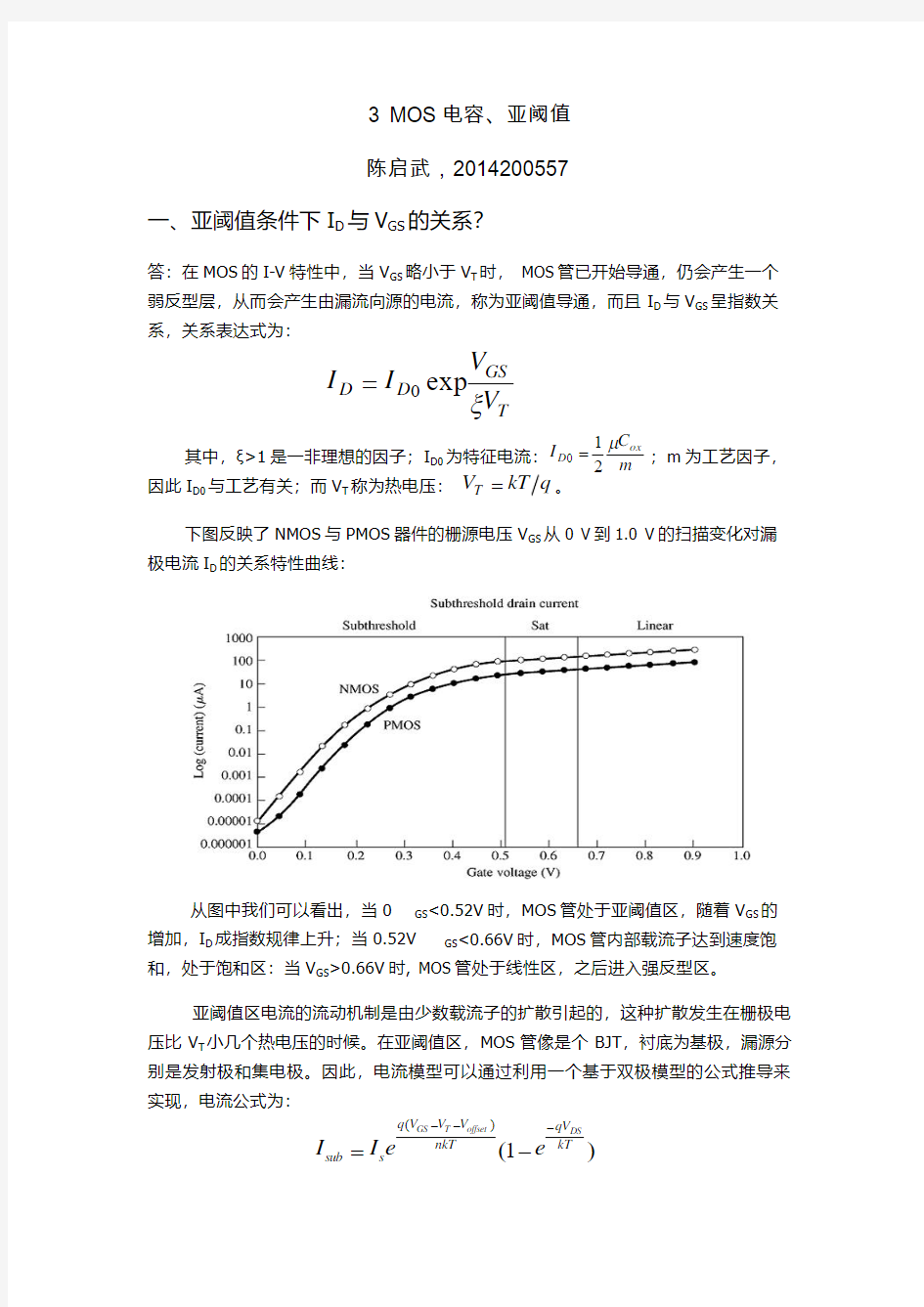

。 下图反映了NMOS 与PMOS 器件的栅源电压V GS 从0 V 到1.0 V 的扫描变化对漏极电流I D 的关系特性曲线:

从图中我们可以看出,当0

亚阈值区电流的流动机制是由少数载流子的扩散引起的,这种扩散发生在栅极电压比V T 小几个热电压的时候。在亚阈值区,MOS 管像是个BJT ,衬底为基极,漏源分别是发射极和集电极。因此,电流模型可以通过利用一个基于双极模型的公式推导来实现,电流公式为:

exp 0T

GS D D V V I I ξ=m C I ox D μ210=q kT V T =)

1()(kT qV nkT V V V q s sub DS offset T GS e e I I ----=

由上式可知:在亚阈值区中,希望降低V GS时电流也会显著降低。

二、短沟器件I-V其它模型?

答:短沟器件除了基于速度饱和的I –V模型外,还有一种基于α功率定律的I –V模型。α功率定律是一种对线性区和饱和区都适用的简单模型,并且该模型在两个区域的边界上失谐。当MOS管处于饱和区时,该模型是根据经验将真实的数据代入以下形式的饱和电流I DS的公式中:

(2-1)

在这个公式中,可以根据测量的标准数据设置K S和α的值。显然,α应该设置成比较接近于1(而不是2)的值。一般,α的值大约是1.25,但随着工艺的等比例减小,α将继续向1逼近。

对于线性区,这种模型的一个实例设置为:

(2-2)

通过使以上两式相等,可以得到饱和电压V Dsat:

(2-3)

基于α功率定律的I – V曲线如下图所示:

饱和区MOS管的特性由式(2-1)描述,线性区MOS管特性由式(2-2)描述。这两个区域之间界面的临界点由式(2-3)得到。需要注意的是,只有当图中的数据点与特性曲线相匹配时,α功率定律模型才适用于手工计算。如果开发了一种新的工艺,则必须提取一套新的参数。因此,基于速度饱和的I – V模型是一种更普遍的模型。

三、器件的导通电阻?

答:MOS器件的导通电阻一般指的是MOS导通时漏源间的电阻R ds(ON),它的大小是一种非线性变化,既跟管子工作状态有关,也与器件的性质有关。

(1)对于长沟器件,当管子处于线性区时,漏极电流为:

线性区的导通电阻R

正好等于漏电导的倒数,其大小为:

ds(ON)

此时,导通电阻相当于一个受V

控制的电阻,这个电阻大概有几欧到几十欧。

GS

当管子处于饱和区时,考虑到沟道调制效应,漏极电流为:

求偏导即可到到饱和区的导通电阻,该电阻与沟道调制参数有关,一般对V

DS

这个电阻会下降到零点几欧甚至零点几毫欧,非常小。

(2)对于短沟道器件,在未达到速度饱和时,器件工作在线性区,漏极电流为:

当达到速度饱和后,器件工作在饱和区时,漏极电流为:

同理,我们只需求出I D对V DS偏导的倒数,即可得到短沟器件的导通电阻。

四、MOS电容与栅源(衬底)电压、漏源电压间的关系?

答:MOS晶体管中有两类非线性电容或由电压决定的电容:薄氧化物电容和结电容。如图所示,薄氧化物电容是由Cgs,Cgd和Cgb组成,适用Cg表示;结电容是由Csb和Cdb组成。其中薄氧化物电容Cg受栅源电压影响,是Vgs的函数;结电容主要与漏源电压有关,下面分别作相关介绍:

1)薄氧化物电容Cg与栅源电压Vgs间的关系

下图为薄氧化物电容Cg与栅源电压Vgs间的函数关系曲线:

当 Vgs< 0时,器件处于截止区,此时所有的电容都取决于栅-衬底电容Cgb,Cgb=Cgd=0。由于栅极下面有一个耗尽区,所以我们将Cg和沟道结电容Cjc串联起

来。结果,在到达累积区之前,总电容一直小于Cg (因为与Cjc 串联)。在这一点上,沟道区充的是正电荷,而栅极充的是负电荷,从而产生总电容Cg 。当Cgs=0时,Cgb 的值大约是1/2Cg 。在栅极电压等于平带电压之前,Cgb 的值一直小于Cg 。

当器件处于线性区时,因为沟道一直从源端一直扩展到漏端,所以Cgs 和Cgd 大约等于(1/2)Cg 。在饱和区中,沟道一直从源端扩展到接近于漏端的距离,所以大多数栅电容都可以归因于源节点,并且归因于漏节点的数量是可以忽略的。对于饱和区,Cgs=(2/3)Cg ,并且Cgd=0。下表显示了薄氧化物电容Cg 与栅源电压Vgs 间的关系表:

2)薄氧化物电容Cg 与漏源电压Vds 间的关系

PN 结自身具有电容效应,这种电容存在于MOS 管的漏区—衬底和源区—衬底,称为结电容或耗尽电容。其计算是相当复杂的三维立体形状。正常工作情况下,这些PN 结是反向偏置的,结电容是所加载的漏源电压Vds 的函数。结电容的计算公式为:

其中,V D 是所加的漏源电压Vds ,Cj0是零偏置结电容,A 是结的面积,Φ0为耗尽层中的內建电势,m 是结的阶梯系数,对于突变结(n +p/p +n )m 约0.5,缓变结m 在0.3~0.5之间。下图显示了这个函数的曲线图:

()m

D j j V C A C 00

/1φ-?=

MOSFET的短沟道效应,DOC

MOSFET 的短沟道效应3 第8章MOSFET 的短沟道效应 MOSFET 的沟道长度小于3um 时发生的短沟道效应 阈值电压到底能缩小到最小极限值。 对于长沟道器件而言,亚阈值电流由下式给出 也可以写成如下的形式 式中的d C 为单位面积耗尽区电容。 t kT V q = 是热电压,1/d ox C C ξ=+,在DS V 大于几个热电压时有

2 对上式两边取对数 上式也可以写成 从式(8.4)中可以看出,当0GS T V V -=时,即当栅-源 电压等于亚阈值电压时有亚阈值电流: 为了使GS T V V <时,器件可以关断,我们可以令(8.4) 制造工艺引起的最小变化也在50mV 之间。工艺和温度引起的变化合计为135mV 左右。因此,对增强型的MOS 器件其阈值电压一般都控制在0.50.9T V V V <<之间。 (B ) 短沟道效应使阈值电压减小 对理想MOSFET 器件,我们是利用电荷镜像原理导出阈

值电压的表达式。见下图。 () ()'''max 8.11mT ss SD Q Q Q +=式中忽略了沟道中的反型层电 荷密度' n Q ,()' max SD a dT Q eN x =为最大耗尽层单位面积电荷密 度。这个电荷密度都由栅的有效面积控制。并忽略了由于源/漏空间电荷区进入有效沟道区造成的对阈值 效应对阈值电压造成的影响。假设源/漏结的扩散横向与纵向相等,都为j x 。这种假设对扩散工艺形成的结 来说是合理的,但对例子注入形成的结则不那么准确。我们首先考虑源端、漏端和衬底都接地的情况。 在短沟道情况下,假定栅极梯形区域中的电荷有栅极

MOSFET的短沟道效应

MOSFET 的短沟道效应3 第8章 MOSFET 的短沟道效应 MOSFET 的沟道长度小于3um 时发生的短沟道效应较为明显。短沟道效应是由以下五种因素引起的,这五种因素又是由于偏离了理想按比例缩小理论而产生的。它们是: (1) 由于电源电压没能按比例缩小而引起的电场 增大; (2) 内建电势既不能按比例缩小又不能忽略; (3) 源漏结深不能也不容易按比例减小; (4) 衬底掺杂浓度的增加引起载流子迁移率的降低; (5) 亚阈值斜率不能按比例缩小。 (A ) 亚阈值特性 我们的目的是通过MOSFET 的亚阈值特性来推断阈值电压到底能缩小到最小极限值。 对于长沟道器件而言,亚阈值电流由下式给出 也可以写成如下的形式 式中的d C 为单位面积耗尽区电容。 t kT V q = 是热电压,1/d ox C C ξ=+,在DS V 大于几个热电压时有 对上式两边取对数 上式也可以写成 从式(8.4)中可以看出,当0GS T V V -=时,即当栅-源电压等于亚阈 值电压时有亚阈值电流: 为了使GS T V V <时,器件可以关断,我们可以令(8.4)中的0GS V =,

则有 如果规定关断时(当0GS V =)的电流比在(当GS T V V =)的电流小5个 数量级,式(8.7)和式(8.8)的两边相除则有 得到亚阈值电压的最小值为 如果1/10.76 1.76d ox C C ξ=+=+=则亚阈值电压的最小值是 5ln105 1.6726 2.3500T t V V mV mV ξ==???=。 如果还想将阈值电压降低到400mV 左右,那么就要减小1/d ox C C ξ=+的值,使1/ 1.34d ox C C ξ=+=。 考虑到温度对阈值电压的影响,按比例缩小阈值电压将更加困难。阈值电压的温度系数1/T dV mV K dT =-。。导致阈值电压在温度范围(0- 85℃)内的变化是85mV 。制造工艺引起的最小变化也在50mV 之间。工艺和温度引起的变化合计为135mV 左右。因此,对增强型的MOS 器件其阈值电压一般都控制在0.50.9T V V V <<之间。 (B ) 短沟道效应使阈值电压减小 对理想MOSFET 器件,我们是利用电荷镜像原理导出阈值电压的表达式。见下图。 () ()'''max 8.11mT ss SD Q Q Q +=式中忽略了沟道中的反型层电荷密度'n Q , ()' max SD a dT Q eN x =为最大耗尽层单位面积电荷密度。 这个电荷密度都由栅的有效面积控制。并忽略了由于源/漏空间电荷区进入有效沟道区造成的对阈值电压值产生影响的因素。 图8.2a 显示了长沟道的N 沟MOSFET 的剖面图。在平带的情况下,且源-漏电压为零,源端和漏端的空间电荷区进入了沟道区,但只占沟道长度的很小一部分。此时的栅电压控制着沟道

3 MOS电容、亚阈值

3 MOS 电容、亚阈值 陈启武,2014200557 一、亚阈值条件下I D 与V GS 的关系? 答:在MOS 的I-V 特性中,当V GS 略小于V T 时, MOS 管已开始导通,仍会产生一个弱反型层,从而会产生由漏流向源的电流,称为亚阈值导通,而且I D 与V GS 呈指数关系,关系表达式为: 其中,ξ>1是一非理想的因子;I D0为特征电流: ;m 为工艺因子,因此I D0与工艺有关;而V T 称为热电压: 。 下图反映了NMOS 与PMOS 器件的栅源电压V GS 从0 V 到1.0 V 的扫描变化对漏极电流I D 的关系特性曲线: 从图中我们可以看出,当0

由上式可知:在亚阈值区中,希望降低V GS时电流也会显著降低。 二、短沟器件I-V其它模型? 答:短沟器件除了基于速度饱和的I –V模型外,还有一种基于α功率定律的I –V模型。α功率定律是一种对线性区和饱和区都适用的简单模型,并且该模型在两个区域的边界上失谐。当MOS管处于饱和区时,该模型是根据经验将真实的数据代入以下形式的饱和电流I DS的公式中: (2-1) 在这个公式中,可以根据测量的标准数据设置K S和α的值。显然,α应该设置成比较接近于1(而不是2)的值。一般,α的值大约是1.25,但随着工艺的等比例减小,α将继续向1逼近。 对于线性区,这种模型的一个实例设置为: (2-2) 通过使以上两式相等,可以得到饱和电压V Dsat: (2-3) 基于α功率定律的I – V曲线如下图所示:

半导体器件物理II必背公式+考点摘要

半二复习笔记 1.1MOS结构 1.费米势:禁带中心能级(EFi)与费米能级(EF)之差的电势表示 2.表面势:半导体表面电势与体内电势之差,体内EFi和表面EFi之差的电势表示 3.金半功函数差 4.P沟道阈值电压

注意faifn是个负值 1.3 MOS原理 1.MOSFET非饱和区IV公式 2. 跨导定义:VDS一定时,漏电流ID随VGS变化率,反映了VGS 对ID 的控制能力 3. 提高饱和区跨导途径

4.衬底偏置电压VSB>0,其影响 5. 背栅定义:衬底能起到栅极的作用。VSB变化,使耗尽层宽度变化,耗尽层电荷变化;若VGS不变,则反型沟道电荷变化,漏电流变化 1.4 频率特性 1. MOSFET频率限制因素:①沟道载流子的沟道运输时间(通常不是主要的限制因素) ②栅电容充放电需要时间 2. 截止频率:器件电流增益为1时的频率 高频等效模型如下:

栅极总电容CG看题目所给条件。 若为理想,CgdT为0,CgsT约等于Cox,即CG=Cox; 非理想情况即栅源、栅漏之间有交叠,产生寄生电容:①CgdT的L为交叠部分长度②CgsT的L为L+交叠部分长度(CgsT=Cgs+Cgsp)。 3. 提高截止频率途径 1.5 CMOS 1.开关特性

2.闩锁效应过程 2.1 非理想效应 1. MOSFET亚阈特性 ①亚阈值电流:弱反型态:势垒较低→电子有一定几率越过势垒→形成亚阈值电流 ②关系式: ③注:若VDS>4(kT/e),最后括号部分≈1,IDsub近似与VDS无关 ④亚阈值摆幅S:漏电流减小一个数量级所需的栅压变化量,S是量化MOS管能否随栅压快速关断的参数。

应变SiGe沟道PMOSFET亚阈值特性模拟

第!"卷第#期 !$$%年&月电子器件’()*+,+-./0*12.342+560.*7+8)5+,9.2:!";.<#=+>2)3)+)3.)+2,‘6(+*10+,)3/216+)1*)5.3>10+)(0/,)*4162.i ))3+*,).*12,)3/216.0 ‘,+))5)+8100)*42)6(8+06)512,60/56/0+>1013+6+0,10+12,.,6/ ))+)1013+6+0,1*)2.06(510+3/220>10)*4166+*6).*6. <5N 67F M P O ’,601)*+)=)*+"+,-=.4/",/(i 6(0+,(.2)5(10156+0),6)5,"3.)+2",)3/216).* X X &Q Q ’89:;<"89:;=应变?@S N 沟道T UV ?W X K 亚阈值特性模拟 屠荆_‘!‘杨荣_‘罗晋生_‘ 张瑞智__>西安交通大学微电子研究所‘西安}_$$~&!<西北核技术研究所‘西安$ %}_$$!~摘要’通过简化的模型‘对应变=)*+沟道+,-=.4/及=)+,-=.4/的亚阈值特性作出了简单的理论分析‘然后用二维模拟器,+))5)进行了模拟和对比"研究了截止电流和亚阈值斜率随=)*++,-=.4/垂直结构参数的变化关系>模拟结果同理论分析符合一致‘表明应变=)*+沟道+,-=.4/的亚阈值特性比=)+,-=.4/更差‘ 并且对垂直结构参数敏感‘在器件设计时值得关注> 关键词’应变锗硅"+型金属@氧化物@半导体场效应晶体管" 亚阈值特性"模型"模拟中图分类号’K A B C :

现代半导体器件物理复习题

半导体器件物理复习题 1.简述Schrodinger 波动方程的物理意义及求解边界条件。 2.简述隧道效应的基本原理。 3.什么是半导体的直接带隙和间接带隙。 4.什么是Fermi-Dirac 概率函数和Fermi 能级,写出n(E) 、p(E) 与态密度和Fermi 概率函数的关系。 5.什么是本征Ferm 能级?在什么条件下,本征Ferm 能级处于中间能带上。 6.简述硅半导体中电子漂移速度与外加电场的关系。 7.简述Hall 效应基本原理。解释为什么Hall 电压极性跟半导体类型( N 型或P 型) 有关。 8.定性解释低注入下的剩余载流子寿命。 9.一个剩余电子和空穴脉冲在外加电场下会如何运动,为什么? 10.当半导体中一种类型的剩余载流子浓度突然产生时,半导体内的净电荷密度如何变化?为什么? 11.什么是内建电势?它是如何保持热平衡的? 12.解释p-n 结内空间电荷区的形成机理及空间电荷区宽度与外施电压的关系。 13.什么是突变结和线性剃度结。 14.分别写出p-n 结内剩余少子在正偏和反偏下的边界条件。 15.简述扩散电容的物理机理。 16.叙述产生电流和复合电流产生的物理机制。 17.什么理想肖特基势垒?用能带图说明肖特基势垒降低效应。 18.画出隧道结的能带图。说明为什么是欧姆接触。 19.描述npn三极管在前向有源模式偏置下的载流子输运过程。 20.描述双极晶体管在饱和与截止之间开关时的响应情况。 21.画出一个n-型衬底的MOS 电容在积聚、耗尽和反型模式下的能带图。 22.什么是平带电压和阈值电压 23.简要说明p-沟道器件的增强和耗尽型模式。 24.概述MESFET 的工作原理。 25.结合隧道二极管的I-V 特性,简述其负微分电阻区的产生机理。 26.什么是短沟道效应?阐述短沟道效应产生的原因及减少短沟道效应的方法。 短沟道效应( shortchanneleffect ):当金属- 氧化物- 半导体场效应晶体管( MOSFE)T 的沟道长度L 缩短到可与源和漏耗尽层宽度之和(WS WD)相比拟时,器件将发生偏离长沟道 (也即L 远大于WSW D)的行为,这种因沟道长度缩短而发生的对器件特性的影响,通常称为短沟道效应。由于短沟道效应使MOSFET的性能变坏且工作复杂化,所以人们希望消除或 减小这个效应,力图实现在物理上是短沟道的器件,而在电学上仍有长沟道器件的特性。 当器件尺寸缩减时,必须将短沟道效应降至最低程度,以确保正常的器件特性及电路工作在器件按比例缩小设计时需要一些准则,一个简要维持长沟道特性的方法为将所有的尺寸及电压,除上一按比例缩小因素К (> 1),如此内部电场将保持如同长沟道MOSFET 一般,此方法称为定电场按比例缩小(constant-field scaling) [ 随器件尺寸的缩减,其电路性能(速度以及导通时的功率损耗)得到加强§.然而,在实际的IC 制作中,较小器件的内部电场往往被迫增加而很难保持固定.这主要是因为一些电压因子( 如电源供 电、阈值电压等)无法任意缩减.由于亚阈值摆幅是无法按比例缩小的,所以,假若阈值电压过低,则关闭态( off state )(V G=0 )的漏电流将会显著增加, 因此,待机功率(standby power)损耗亦将随之上升[12].通过按比例缩小规范,

DIBL效应对小尺寸MOS晶体管阈值电压和亚阈值特性的影响

DIBL 效应对小尺寸MOS 晶体管阈值电压 和亚阈值特性的影响 1.MOS 晶体管阈值电压 阈值电压定义为沟道源端的半导体表面开始强反型所需要的栅压。根据定义,它由以下三部分组成:(1)抵消功函数差和有效界面电荷的影响所需的栅压,即平带电压Vfb ;(2)产生强反型所需的表面势,即2Φf ;(3)强反型时栅下表面层电荷Qs 在氧化层上产生的附加电压,通常近似为-Q b (2Φf )/Cox 。对于MOSFET ,阈值电压表示式为: V T = V fb + 2Φf - Q b (2Φf )/C ox 需要注意,对于NMOS ,Φf = (K B T/q )ln(N A /N i ),相应的,Q b = -γC ox f 2φ, γ=A s qN ε2/C ox ;对PMOS ,Φf = -(K B T/q )ln(N D /N i ),Q b =γC ox )2(f φ-, γp =D s qN ε2/C ox 。N A ,N D 是半导体衬底的掺杂浓度。 在MOS 集成电路的设计和生产中,阈值电压的控制十分重要。大多数应用中需要的是增强型器件,这时对NMOS 要求V T 〉0,对PMOS 要求V T <0。上述要求对PMOS 容易达到,对NMOS 却很困难。原因是V fb =Φms -Q 0/C ox 中的Q 0总是正的,即-Q 0/C ox 总是负的,结果使P 沟和N 沟器件的V fb 一般都是负的。对PMOS 而言,V T 表示式中的另外两项也都是负的因此产生增强型没有困难;对NMOS 而言,另外两项之和必须大于V fb ,从而要求衬底掺杂浓度较高,这会导致大的衬底电容和低的击穿电压,是十分不理想的。 我们可以通过离子浅注入的方法将杂质注入到沟道表面的薄层内,其作用相当于有效界面电荷,所以阈值电压的改变可以从下面公式估算: ΔV T = ±qN I / C ox N I 是注入剂量(离子个数/cm 2)。注入杂质为P 型时,上式取正号;注入杂质为N 型时,上式取负号。 Q b 表示式中γ=A s qN ε2/C ox 反映衬底偏压对阈值电压影响的强弱程度,故称衬偏系数。对于P 沟器件,衬底偏压引起的阈值电压改变为 ΔVT=-γp[bs f V +φ2-f φ2] γp =D s qN ε2/C ox 是P 沟器件(N 型衬底)的衬偏系数。 氧化层厚度对阈值电压也有影响。氧化层厚度增加时,栅压对半导体表面的控制作用减弱,为了使表面形成导电沟道,需要加更大的栅压,即阈值电压增加。这一点对制作场区十分重要。 2.MOS 晶体管亚阈值电流方程与亚阈值摆幅 栅偏压低于阈值以至沟道表面是弱反型时,MOSFET 仍有很小的电流,这就是亚阈值电流,器件的工作状态也被说成是亚阈值区。亚阈值区是描述MOSFET

MOSFET性能综述

MOSFET 性能定标——第一部分:历史选择 Ali Khakifirooz ,IEEE 会员;Dimitri A. Antoniadis ,IEEE 院士 摘要:描述MOSFET 在饱和状态下从亚阈到强反型的一个简单的分析模型用来推导出一个新的关 于晶体管内在转换延迟的公式。上述模型服从测量趋势:在环振荡器上数据比传统的CV/I 标准更好。MOSFET 性能衡量的历史趋势被检验,并且现在表明沟道中载流子速度的持续增加是提高晶体管测量性能的主要动力。近来应变工程器件中速度和迁移率依赖性研究是基于出版的实验数据和一个提出来以验证这种依赖性的理论。事实表 明:虚拟源速度和曾经人们相信的尽管事实是国家最先进的MOSFETs 工作在它们极限60%–65%相比依赖于低场迁移率更强烈一些。这些观察将 在本文的第二部分用来探索按参数排序的关键器件之间的交换因为尺寸测量的器件性能相称的比例来继续未来高性能CMOS 系列。 关键词:延迟,迁移率,MOSFET 定标,性能,前景,迁移速度。 Ⅰ.引言 为了继续其历史测量趋势,晶体管性能切合实际的基准是量化技术要求中必不可少的。不同于当前和过去的技术,品质因素(FOMs)的不同数字的直接测量是可能的或者它们很容易从拥有好的校准模型的电路仿真中获取,对未来技术评估电路级性能的措施并不简单。有预测模型[1], [2]的电路仿真或使用计算机辅助设计的模型校准以及器件仿真是一个选择。然而如果对于所需的FOMs 的解析表达式是易得到的,那么将更容易并且更加有洞察力。 历史上,晶体管延迟已经由sat /D D D C V I 来简 单近似,其中VDD 是电源电压、sat D I 是 G S D S D D V V V ==时的漏极电流。C 代表总的负载 电容,为获取由晶体管为主的电路中固有晶体管 延时通常被用来等同于反型中栅极电容inv C 。尽管事实上开关电荷in v D D C V 并不包含栅极和其他 晶体管固有的寄生电容,以及在CMOS 结构[3], [4]中开关期间漏极电流从未达到sat D I ,因为这个度 量同时也高估了反转电荷,对于早期的技术节点它提供了一个可供人们接受的结果。然而,随着晶体管进一步缩小,寄生电容的相对重要性也相应增加,这使得忽略它们变得不切实际。 最近,研究表明,如果在分母的电流被代表平均开关电流[3]–[5]的有效电流e ff I 取代,CV/I 度量 更好地跟随实验逆变器延迟。 通常,一个显著的观察是sa t eff D I I 比例减小 随着晶体管按比例减小,主要是由于增加的漏感应势垒降低(DIBL )。因此未来期间设计应该旨在通过在维持一个可接受的电流[5]的同时控制短沟道效应来最大化有效电流。 在本文中,我们提出一个对MOSFET 本证延 迟的解析表达式,它是基于对有效电流和总栅极开关电荷的物理模型,更加的精确。本表达式适用于已发表的器件数据,以及MOSFET 性能定标的历史趋势已被验证。用定标结果表明在沟道中载流子迁移速度对改进的晶体管性能起主要驱动作用。迁移速度和迁移率的依赖性在最近的应变工程期间中是基于实验数据和一个被提出用于检验此依赖型的理论被研究的。本文的第二部分将讨论这些观测可以被用来探索关键器件参数之间的权衡为了用尺寸定标器件性能相称的标定来继续历史的趋势。 Ⅱ.简单的MOSFET 解析模型 在饱和状态下标准宽度晶体管电流表示为 ()D inv G S T I W C V V v '=- (1) 其中T V 是在D I -G S V 曲线中用线性外推法得 到的包和阈值电压,inv C '是每单位面积的栅极电容,v 代表有效载流子迁移速度。有效速度v 和源 极附近势垒处的载流子平均迁移速度有关,这就

- MOSFET的短沟道效应

- 半导体物理6

- 第二章 MOS器件的物理基础

- 3 MOS电容、亚阈值

- 半导体器件物理-MOSFET3

- MOSFET性能综述

- 亚阈值摆幅

- 半导体器件物理II必背公式+考点摘要

- MOSFET的短沟道效应

- 第3章 第2讲 MOS晶体管的瞬态特性

- 应变SiGe沟道PMOSFET亚阈值特性模拟

- DIBL效应对小尺寸MOS晶体管阈值电压和亚阈值特性的影响

- MOSFET的短沟道效应,DOC

- MOSFET的非理想特性以及小尺寸效应

- 现代半导体器件物理复习题

- CMOS亚阈值特性的低频低压微功耗电路的设计与模拟

- 纳米级MOSFET亚阈值区电流特性模型

- MOSFET的短沟道效应

- 第六章 MOSFET

- 半导体器件物理(第六章) 施敏 第二版