A New High-Speed SAR ADC Architecture

A New High-Speed SAR ADC Architecture

Saleh Abdel-Hafeez, Member, IEEE

Jordan University of Science and Technology

College of IT, Computer Engineering Dept.

Jordan, 22110 IRBID

sabdel_99@https://www.wendangku.net/doc/8717847569.html,

Abstract—The design plan and HSPICE measurement of a high acquisition speed for a sample of 8-bit CMOS differential successive approximation register (SAR) Analog-to-digital converter (ADC) are presented. The operation of the conventional main switch-capacitor array is divided into two switch-capacitor arrays. Such that, one switched-capacitor array is used to define the four most-significant bits, while the other switched-capacitor array is used to refine the digital output by measuring the least four significant bits. Thus, the critical time constant, which is usually realized in a single conversion cycle, is divided into four conversion cycles (i.e. the time required to quantize the four most-significant bits). Thereby, our proposed ADC operates at 200MHz conversion cycle for a sample rate of 25 MS/sec. with power consumption of 3.7mW. The design is based on 0.25μm CMOS TSMC technology and comprises three comparator circuits, sign-comparator and two switched-capacitor arrays’ comparators.

I.I NTRODUCTION

Successive approximation ADC is often considered as one of the most popular A/D conversion techniques; because it offers the combination of high accuracy and low-power consumption [1]-[3]. The self calibration capabilities and density of CMOS and BiCMOS technologies have provided resolutions as high as 18 bits [1],[2]. Nevertheless, the SAR ADC is known by its moderate speed which limits its applications [4]-[5]. Several techniques combine a resistor ladder with the capacitor array, such that, the ladder provides fraction of analog input voltage which is commonly known as resistor-capacitor (Hybrid) circuit [5].

In systems where ultimate speed is the primary goal, identical A/D converters can be interleaved in time so as to achieve more parallelism than simple flash topologies [6],[7]. Other recent approaches focuses on improving the settling time constant of comparator inputs by realizing a charge pump switch circuit [8]-[10] corresponding to common mode voltage. This paper consider deals on the improvement of acquisition speed, while maintaining the accuracy and low power features of SAR ADC based on differential switched-capacitor array. Section II shows the proposed architecture of high-speed SAR ADC, while section III depicts the suggested timing behavior to reduce weighted capacitor settling time. In section IV, HSPICE simulation results for the SAR ADC is explained, and finally, section V is reserved for the conclusion and recommendation drawn from this work.

II.PROPOSED HIGH-SPEED SAR ARCHITECTURE The circuit traces analog input voltage by one bit sequentially through a network of binary weighted switch-capacitor array. The array is based on charge redistribution principles where Sample/Hold (S/H) function is carried out within the block itself, precluding an extra cycle for S/H. Hence, the maximum achievable sampling frequency is fs = fclk/(N) for a given conversion frequency (fclk) and N-bit ADC.

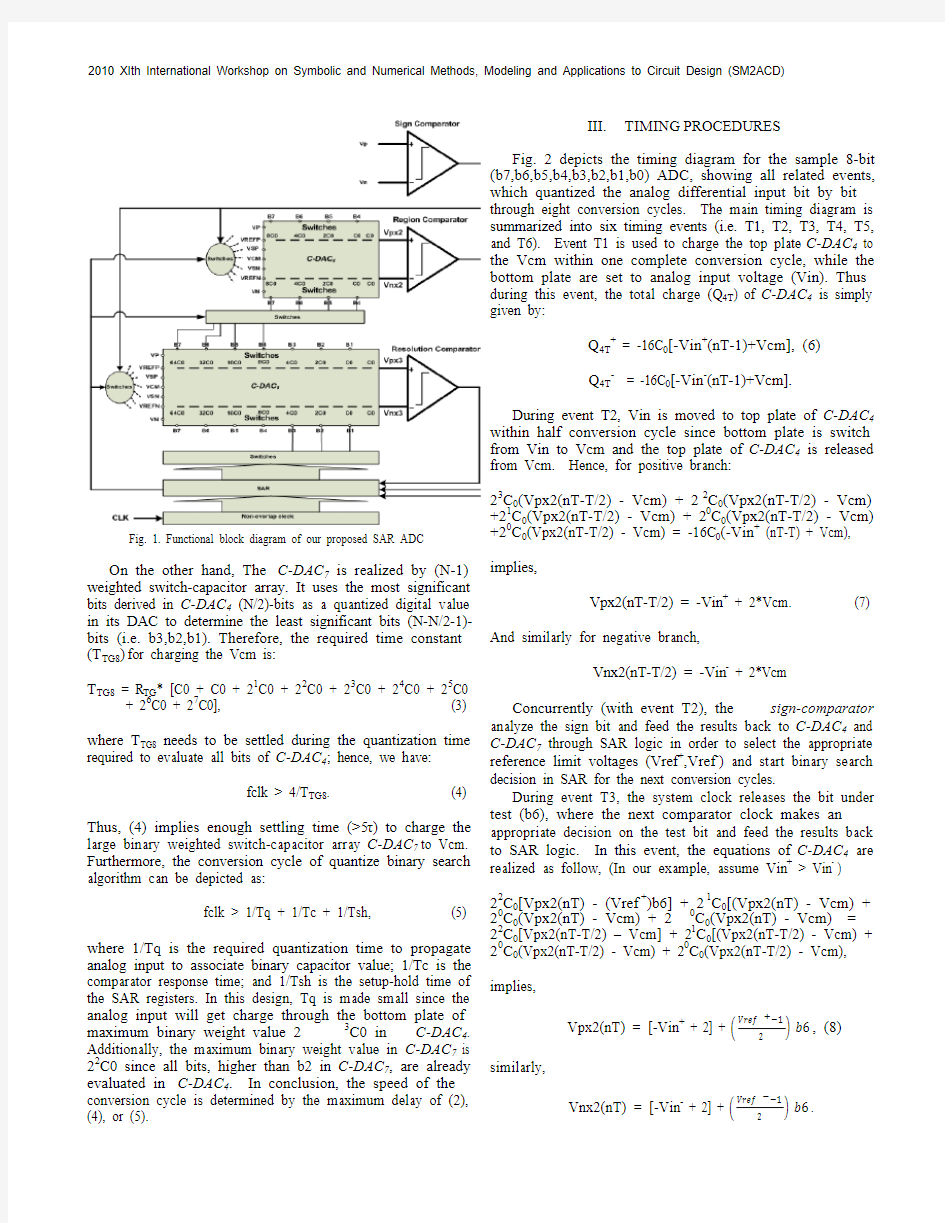

Fig. 1 displays the most important function blocks for a sample of the 8-bit (b7,b6,b5,b4,b3,b2,b1,b0) SAR ADC consisting of two capacitor arrays, three low power comparators [8] (i.e. sign-comparator, region-comparator, and resolution-comparator), SAR logic block, CMOS switches, and non-overlap clock generation circuit. There are two binary weighted switch-capacitor arrays identify as C-DAC4 and C-DAC7, where the subscript numbers present the 4-bit and 7-bit differential charge redistribution DAC, respectively.

The conversion cycle scheme starts by determining the sign bit through using the sign-comparator, and hence, eliminating the value 2N-1C0 from the C-DAC4 and the C-DAC7. Thereby, the charge time of common mode voltage to top plate capacitor of C-DAC4 and C-DAC7 is largely reduced. The quantized digital output of most significant N/2-bit (in our example: b7, b6, b5, b4) are determined bit by bit through a successive approximation algorithm using C-DAC4 with region-comparator and controlled by SAR logic block. Consequently, the required charge time for the common mode voltage (Vcm) is depicted by the time constant (T TG4); assuming a perfect capacitor ratio matching, where the nominal capacitor values are given by C i=2i-1 × C0, 1 ≤ i ≤ N for N-bit ADC. Thus we have:

T TG4 = R TG * [C0 + C0 + 21C0 + 22C0 + 23C0], (1)

where R TG is the CMOS switch resistor, and C0 is the unit charge capacitor for DACs structure. Hence, the conversion cycle is limited by:

fclk > 1/T TG4. (2)

Fig. 1. Functional block diagram of our proposed SAR ADC On the other hand, The C-DAC7 is realized by (N-1) weighted switch-capacitor array. It uses the most significant bits derived in C-DAC4 (N/2)-bits as a quantized digital value in its DAC to determine the least significant bits (N-N/2-1)-bits (i.e. b3,b2,b1). Therefore, the required time constant (T TG8)for charging the Vcm is:

T TG8 = R TG* [C0 + C0 + 21C0 + 22C0 + 23C0 + 24C0 + 25C0 + 26C0 + 27C0], (3)

where T TG8 needs to be settled during the quantization time required to evaluate all bits of C-DAC4; hence, we have:

fclk > 4/T TG8. (4)

Thus, (4) implies enough settling time (>5τ) to charge the large binary weighted switch-capacitor array C-DAC7 to Vcm. Furthermore, the conversion cycle of quantize binary search algorithm can be depicted as:

fclk > 1/Tq + 1/Tc + 1/Tsh, (5)

where 1/Tq is the required quantization time to propagate analog input to associate binary capacitor value; 1/Tc is the comparator response time; and 1/Tsh is the setup-hold time of the SAR registers. In this design, Tq is made small since the analog input will get charge through the bottom plate of maximum binary weight value 23C0 in C-DAC4. Additionally, the maximum binary weight value in C-DAC7 is 22C0 since all bits, higher than b2 in C-DAC7, are already evaluated in C-DAC4. In conclusion, the speed of the conversion cycle is determined by the maximum delay of (2), (4), or (5).

III.TIMING PROCEDURES

Fig. 2 depicts the timing diagram for the sample 8-bit

(b7,b6,b5,b4,b3,b2,b1,b0) ADC, showing all related events,

which quantized the analog differential input bit by bit through eight conversion cycles. The main timing diagram is summarized into six timing events (i.e. T1, T2, T3, T4, T5,

and T6). Event T1 is used to charge the top plate C-DAC4 to

the Vcm within one complete conversion cycle, while the bottom plate are set to analog input voltage (Vin). Thus during this event, the total charge (Q4T) of C-DAC4 is simply

given by:

Q4T+ = -16C0[-Vin+(nT-1)+Vcm], (6)

Q4T- = -16C0[-Vin-(nT-1)+Vcm].

During event T2, Vin is moved to top plate of C-DAC4

within half conversion cycle since bottom plate is switch

from Vin to Vcm and the top plate of C-DAC4 is released

from Vcm. Hence, for positive branch:

23C0(Vpx2(nT-T/2) - Vcm) + 22C0(Vpx2(nT-T/2) - Vcm)

+21C0(Vpx2(nT-T/2) - Vcm) + 20C0(Vpx2(nT-T/2) - Vcm)

+20C0(Vpx2(nT-T/2) - Vcm) = -16C0(-Vin+ (nT-T) + Vcm), implies,

Vpx2(nT-T/2) = -Vin+ + 2*Vcm. (7)

And similarly for negative branch,

Vnx2(nT-T/2) = -Vin- + 2*Vcm

Concurrently (with event T2), the sign-comparator analyze the sign bit and feed the results back to C-DAC4 and

C-DAC7 through SAR logic in order to select the appropriate reference limit voltages (Vref+,Vref-) and start binary search decision in SAR for the next conversion cycles.

During event T3, the system clock releases the bit under

test (b6), where the next comparator clock makes an appropriate decision on the test bit and feed the results back

to SAR logic. In this event, the equations of C-DAC4 are realized as follow, (In our example, assume Vin+ > Vin- )

22C0[Vpx2(nT) - (Vref+)b6] + 21C0[(Vpx2(nT) - Vcm) +

20C0(Vpx2(nT) - Vcm) + 20C0(Vpx2(nT) - Vcm) =

22C0[Vpx2(nT-T/2) – Vcm] + 21C0[(Vpx2(nT-T/2) - Vcm) +

20C0(Vpx2(nT-T/2) - Vcm) + 20C0(Vpx2(nT-T/2) - Vcm),

implies,

Vpx2(nT) = [-Vin+ + 2] +

6, (8) similarly,

Vnx2(nT) = [-Vin- + 2] +

6

.

Consequently, for general case (Vin+ > Vin-) we have:

Vpx2(nT)

=[-Vin+ + 2] +∑

, (9) similarly,

Vnx2(nT)

=[-Vin- + 2] +∑

.

Subsequently, the binary search algorithm continues its successive approximation using C-DAC4 and region-comparator to further quantize the bits b5 and b4. Mean while, the top plate of C-DAC7 is charged to Vcm while the bottom plate is set to Vin. Hence, the event T4 provides four conversion cycles to charge the C-DAC7.

Furthermore, the Vin is moved to top plate of C-DAC7 during event T5 in order to provide a similar sequential pattern depicted in (1)-(4); thereby, the structure assure no latency delay between the DACs. Event T6 starts quantization the successive approximation in C-DAC7 to evaluate b3, and furthermore, the next two conversion cycles are used to evaluate b2 and b1.

IV.S WITCH-C APACITOR A RRAY L AYOUTS Binary weighted capacitor array is usually considered a major source of error due to switches and capacitors mismatches, which usually limits the performance of ADCs’. The capacitor array is usually made of identical unit capacitors to form large capacitance as a general rule of thumb for minimizing the ratio mismatches [11]-[12]. In addition, common-centroid geometries and inter-digitization are particularly of great importance in reducing mismatches and achieving high accuracy as they help reducing the effects of gradients and random errors in fabrications [12]. Motivated by the importance of achieving high precise layout, the unit-capacitor array of differential DAC switch-capacitor array is arranged with common-centroid geometries as shown in Fig. 3. This layout arrangement provides a good cancelation of random variations across the array through an assurance of center gradient in fabrication process in all binary combinations. Besides, the proposed layout minimizes the fringing capacitances between the two lines of comparator inputs. The cell number of the layout presentations in Fig. 3 presents the unit capacitance of comprise weighted bit; for example, the cell number “6” presents the unit capacitor of weighted binary bit “b6” which has a 64 identical units capacitances for the positive line switch-capacitor array, while the cell number “-6” presents 64 identical units for the negative line switch-capacitor array.

Fig. 2. Timing diagram for the proposed SAR ADC architecture for a sample of an 8-bit size

V. E XPERIMENTAL R ESULTS

We present the HSPICE simulation results for the sample 8-bit differential SAR ADC proposed in Fig. 1. The proposed ADC has an input range between 0.5V and 1.5V, giving a quantized input resolution of 4mV. Subsequently, the common mode constant voltage (Vcm) is set to 1V, and the input voltage limits Vref + = 1.5V and Vref - = 0.5V. Fig. 4 shows the HSPICE simulation results of ramp input at a conversion cycle of 200MHz, where the noise is injected at the power supply voltage in the form of sinusoidal waveform of magnitude 0.05mV. Consequently, the INL of the converter is 0.64LSB which repeats itself within both sub-ranges (negative and positive). Furthermore, our ADC sample rate is 25 M sample/sec which accurately estimates the output spectrum for a full input range signal at a frequency of

0.300875 . (10) This allowed the input signal to land on the eleven bin of

a 914-bit output spectrum. Hence only 914 samples are taken from 11 complete sinusoidal input signal cycles were used for a 914-point FFT. Fig. 5 shows the normalized result of FFT, where the largest harmonic component (at the normalized pin=0.012) is about 52 dB below the main component, which satisfies the requirement for a sample of 8-bit SAR ADC. Further characteristics are summarized in Table 1. The HSPICE simulation results, shown in Fig. 6, present the voltage conversion towards the comparators (region-comparator and resolution-comparator ) inputs as the successive decision of bits were carried out through the 8-bit ADC.

TABLE 1: SUMMARY OF MEASUREMENTS RESULTS

VI. CONCLUSION

In focus of our interest was the problem of increasing the sampling rate that deals with SAR ADC architecture in order to consider the advantage of low consumption power. The main conventional DAC is split into two sub-DACs that lead

to a substantial reduction in the whole capacitive load at the input-lines of DACs comparators. A complete timing diagram is derived for the operation of the new structure of ADCs in order to assure right sequences for the two DACs without latency or overlapping operation based on successive approximation. HSPICE results reveal that the tested 8-bit switched-capacitor SAR ADC operates at 200MHz convergence cycle with a sample rate of 25M sample/sec. The analog input is swing from 1.5 V to 0.5 V giving a 4mV a quantized resolution with SNR= 51 dB and INL(/DNL) = 0.64(/0.64)LSB.

Fig. 3. Layout unit capacitor arrangement for the 8-bit switch-capacitor DAC

Fig. 4. Measured quantized value with respect to input voltage

Parameters

Value

Technology 0.25μm Supply Voltage 2.5V

Input Range 0.5V -to- 1.5V

Resolution 8-bit INL/DNL 0.64/0.64LSB Maximum sampling rate 25M sample/second

Convergence cycle 200MHz Power (@ 2.5v and 200MHz) 3.7mW SNR at input frequency 0.3MHz

51.2 dB

Fig. 5. Spectrum of the proposed SAR ADC output

Fig. 6. HSPICE waveforms of the 8-bit ADC using TCMC 0.25μm technology, (The horizontal scale is in nanoseconds and the vertical

scale is in volts)

R EFERENCES

[1] B. Razavi, Principles of Data Conversion System Design, John Wiley

& Sons, inc., 1995.

[2] F.Ohnhaeuser and M. Huemer,”Methods to Eliminates Dynamic Errors

in High-Performance SAR A/D Converter,” IEEE International Symposium on Circuits and Systems 2008 (ISCAS), pp. 2398-2401, May 2008. [3]K. Dabbagh-Sadeghipour, K. Hadidi, and A. Khoei, “A new succesive

approximation architecture for high-speed low-power ADCs,” Int. J.

Electron. Comm. (AEU), Vol. 60, pp. 217-223, Feb. 2006.

[4] A. Masuzawa, “Design Challenges of Analog-to-Digital Converters in

Nanoscale CMOS,”IEICE Trans Electron., Vol. E90-C, pp. 779-785, No. 4, April 2007.

[5]M. davidovic, G. Zach, and H. Zimmermann,”An 11-bit successive

approximation analog-to-digital converter based on a combined capacitor-resistor network,” Elektrotechnik & Informationstechnik, pp.

704-709, 2010.

[6] C.-W. Hsu and T.-H. Kuo,”6-bit 500 MHz flash A/D converter with

new design techniques,” IEE Proc.-Circuits Devices Syst., Vol. 150, No. 5, Oct. 2003.

[7]J. LI and F. Maloberti,”Pipeline of Successive Approximation

Converters with Optimum Power Merit Factor,” Analog Integrated Circuits and Signal Processing, Vol. 45, pp. 211-217, 2005.

[8]S. Long, J. Wu, and X. Xia, “A 1.8-V 3.1 mW successive

approximation ADC in system-on-chip,” Analog Integrated Circuit and Signal Processing, Springer Science, Vol. 56, pp. 205-211, 2008.

[9]K. Dabbagh-Sadeghipour, K. Hadidi, and A. Khoei, “A new successive

approximation architecture for high-speed low-power ADCs,”

International Journal of Communication, Vol. 60, pp. 217-223, 2006. [10]M. Casubolo, M. Grassi, Andrea Lombardi, Franco Maloberti, and

Piero Malcovati, “A Two-Bit-per-Cycle Succesive-Approximation ADC with Background Offset Calibration,” ISCAS 2008, pp. 650-653, May 2008.

[11]M. J. McNutt, S. LeMarquis, and J. L. Dunkley, “Systematic

Capacitance Matching Errors and Corrective Layout Procedures,” IEEE J. of Solid-State Circuits, vol. 29, no. 5, May 1994.

[12] D. Sayed and M. Dessouky, “Automatic Generation of Common-

Centroid Arrays with Arbitrary Capacitor Ratio,” Proceedings of the 2002 Design, Automation and Test in Europe Conference and Exhibition (DATE’02), pp. 1530-1591, March 2002.

包络函数方法

包络函数方法 低维纳米结构中电子态的计算是一个基本而重要的问题。一般来说,计算纳米结构中的电子态有两种方法,一种是利用第一性原理计算,第二种是有效质量包络函数近似。第一性原理是比较常用的一种方法,它的计算结果相对来说比用有效质量包络函数近似的结果更可靠,但是用第一性原理来计算较大的纳米结构(里面含有几百万个原子)是非常困难的,因为它需要一个超级计算系统。相比之下,用有效质量包络函数近似的方法就比较合适了,在个人计算机上就能实现,所以Burt提出的包络函数方法被认为是描述纳米结构电子态的最有前景的方法。先将包络函数方法的基本理论介绍如下: 首先,包络函数方法是在以下近似条件下得到的计算纳米结构电子态的方法: (1)有限质量近似。 (2)忽略了真实离子势场中迅速变化的震荡分量,近似认为载流子只受外场的作用。 (3)保证异质结两边的态具有同样的对称性,例如对于GaAs/AlGaAs系统,要保证电子同处于导带的Γ谷中。 此时,如果晶体中存在微扰势称V p(r),则电子运动的薛定谔方程为: ( 其中是没有微扰的晶体哈密顿量。如果微扰势是个空间缓变量,且其强度小到不足以引起带之间的耦合,则电子波函数可以表示为一个空间缓变函数与带边波函数的乘积。 称为包络函数。 如果能带是非简并的,例如导带,在导带底附近的能量可近似用有效质m*表示 其中是导带边能量,则包络函数满足

如果能带是简并的,例如价带顶,则波函数可表示为包络函数与带边波函 数)乘积的线性组合 满足一组联立的有效质量方程组 其中称为有效质量参数。 若无外界的微扰势,则在每种材料内部就电子而一言,有效质量方程简化为一平面波方程。在界面附近,势是突变的,有效质量近似不再成立,暂时先不考虑这一点。对于两种材料,它们的有效质量和带边能量是不同的。 引入(z)和有效势V(z),其中 (z)= (z)= 是两种材料导带边能量之差,也就是导带带阶。包络函数方程可写为:

包络解调法及其诊断

包络解调法及其诊断 包络解调法是故障诊断中较常用的一种方法,它可非常有效地识别某些冲击振动。从而找到该冲击振动的振源。例如,当轴承或齿轮表面因疲劳或应力集中而产生剥落和损伤时,会产生周期性的冲击振动信号,如图4—25所示。 从图4—25个可以看出,信号包括两部分:—部分是载频信号,即系统的自由振荡信号及各种随机干扰信号的频率,是图形中频率成分较高的信号;第二部分是调制信号,即包络线所包围的信号。它的频率较低,多为故障信号。 因此.若要对故障源进行分析,就必须把低频信号(或调制信号)从高频信号(或载频信号)中分离出来。这一信号分离、提取过程,被称为信号的包络解调。对分离提取出来的包络信号进行特征频率和幅度分析,就能准确可靠地诊断出如轴承和齿轮的疲劳、切齿、剥落等故障。

目前分析高频冲击的有效方法之一是共振解调(包络处理),即取振动时域波形的包络线,然后对包络线进行频谱分析。由于包络线处理可找出反复发生振动的规律,根据轴承的特征频率,就可诊断出轴承或齿轮故障的部位。研究表明,当轴承或齿轮无故障时,在共振解调频谱中没有高阶谱线;有故障时,共振解调频谱中出现高阶谱线。 当齿轮发生疲劳裂纹时,齿轮刚度的变化会引起齿轮振动噪声信号瞬时频率(相位)和幅值的变化。但裂纹由于只影响齿轮刚度,齿形无大变化,故振动噪声信号在频域中无明显征兆,因此频谱分析对裂纹诊断基本无效。可采用时域平均法分析。如果齿轮同时存在其它类型的故障,则时域平均法的可靠性不高。此时可试用希尔伯特变换或自适应滤波技术提取相位信息,也可试用共振解调分析技术即包络谱分析法。 一、包络分析法进行故障诊断的原理 当轴承或齿轮某一元件表面出现局部损伤时,在受载运行过程中

包络定理

2. 包络定理1 在上图表示的最大值函数与目标函数的关系中,我们看到,当给定参数a 之后,目标函数中的选择变量x 可以任意取值。如果x 恰好取到此时的最优值,则目标函数即与最大值函数相等。而且,我们还可以注意到,当目标函数与最大值函数恰好相等时,相应的目标函数曲线与最大值函数曲线恰好相切,即它们对参数的一阶导数相等。对这一特点的数学描述就是所谓的“包络定理”。 ⑴ 包络定理:无约束模型 设最大值函数为: ()((),)V a f x a a = 对参数a 求导有: (0)a x a a x dx V f f f f da =+== 其中,a f 在最优解处取值。 ▼ 另一种表述 设模型 max (,)x f x a 的最优解为()x x a **=;代入原目标函数(,)f x a 即得最大值函数: ()((),)V a f x a a * 上式两边对参数a 求导得: [][((),)]a a x a a dx V f x a a f f f da * *** ??==+=???? 其中,方括号右边的下标“a ”表示对参数a 求导,上标“*”表示求导后的结果在最优解处取值。由于是在最优解处取值,故由一阶必要条件可知0x f =。于是有第三个等式。第三个等式中的[]a f *表示原目标函数(,)f x a 对a 求导后在最优解处取值。 ⑵ 包络定理:等式约束模型 设最大值函数为: ()((),(),)V a L x a a a λ= 对参数a 求导有: (0)a x a a x dx d V L L L L L L da da λλλ=++=== 其中,a L 在最优解处取值。 ▼ 另一种表述

设计SAR ADC驱动电路,第一部分:ADC工作原理详解

Designing SAR ADC Drive Circuitry by Rick Downs, Applications Engineering Manager and Miro Oljaca, Systems Engineer Data Acquisition Products, Texas Instruments, Incorporated Part I: A Detailed Look at SAR ADC Operation Designing buffer circuitry for driving successive-approximation (SAR) ADCs requires knowledge of the load that the inputs present. Specifications in data sheets may mislead the user into thinking that analog inputs, for example, are static when in fact they are a very dynamic load. This three-part article will look at the architecture of modern SAR ADCs, and examine the conversion process in detail. In this first part the operation of a modern SAR ADC is discussed. A detailed, step-by-step analysis is then given, illustrating the sampling and conversion process. The final part discusses charge distribution during the sampling process. This analysis will give the user of these devices a better understanding of the inner operations of a charge-redistribution ADC. 1. The SAR ADC Structure Fig. 1: Representative SAR Input Stage Fig. 1 shows a representative three bits of a typical SAR ADC (the ADS8361). Looking at this example, we will examine a three-bit conversion sequence. For our analysis, we will assume that the most significant bit (MSB) capacitor has a value of 20 pF. The capacitor nearest to the MSB capacitor will have half its value, or 10 pF and the least significant bit (LSB) capacitor will have one-quarter of the MSB capacitor value, or 5 pF. A termination capacitor has the same value as the LS B capacitor. The effect of this is that the sum of all the capacitors below the MSB capacitor becomes 20 pF, or the same value as the MSB capacitor.

包络检波器的设计与实现

2013~2014学年第一学期 《高频电子线路》 课程设计报告 题目:包络检波器的设计与实现 专业:电子信息工程 班级:11电信1班 姓名: 指导教师:冯锁 电气工程学院 2013年12月12日

任务书

摘要 调幅波的解调即是从调幅信号中取出调制信号的过程,通常称为检波。检波广义的检波通常称为解调,是调制的逆过程,即从已调波提取调制信号的过程。对调幅波来说是从它的振幅变化提取调制信号的过程;对调频波,是从它的频率变化提取调制信号的过程;对调相波,是从它的相位变化提取调制信号的过程。 工程实际中,有一类信号叫做调幅波信号,这是一种用低频信号控制高频信号幅度的特殊信号。为了把低频信号取出来,需要专门的电路,叫做检波电路。使用二极管可以组成最简单的调幅波检波电路。调幅波解调方法有二极管包络检波器、同步检波器。目前应用最广的是二极管包络检波器,不论哪种振幅调制信号,都可采用相乘器和低通滤波器组成的同步检波电路进行解调。但是,普通调幅信号来说,它的载波分量被抑制掉,可以直接利用非线性器件实现相乘作用,得到所需的解调电压,而不必另加同步信号,通常将这种振幅检波器称为包络。 为了生动直观的分析检波电路,利用了最新电子仿真软件Multisim11.0进行二极管包络检波虚拟实验,Multisim具有组建电路快捷、波形生动直观、实验效果理想等优点。计算机虚拟仿真作为高频电子线路实验的辅助手段,是一种很好的选择,可以加深学生对一些抽象枯燥理论的理解,从而达到提高高频电子线路课程教学质量的目的。

目录 第1章设计目的及原理 (4) 1.1设计目的和要求 (4) 1.1设计原理 (4) 第2章指标参数的计算 (8) 2.1电压传输系数的计算 (8) 2.2参数的选择设置 (8) 第3章 Multisim的仿真结果及分析 (11) 总结 (16) 参考文献 (17) 答辩记录及评分表 (18)

包络检波器的设计与实现

目录 前言 (1) 1 设计目的及原理 (2) 1.1设计目的和要求 (2) 1.1设计原理 (2) 2包络检波器指标参数的计算 (6) 2.1电压传输系数的计算 (6) 2.2参数的选择设置 (6) 3 包络检波器电路的仿真 (9) 3.1 Multisim的简单介绍 (10) 3.2 包络检波电路的仿真原理图及实现 (10) 4总结 (13) 5参考文献 (14)

前言 调幅波的解调即是从调幅信号中取出调制信号的过程,通常称为检波。广义的检波通常称为解调,是调制的逆过程,即从已调波提取调制信号的过程。对调幅波来说是从它的振幅变化提取调制信号的过程;对调频波,是从它的频率变化提取调制信号的过程;对调相波,是从它的相位变化提取调制信号的过程。 工程实际中,有一类信号叫做调幅波信号,这是一种用低频信号控制高频信号幅度的特殊信号。为了把低频信号取出来,需要专门的电路,叫做检波电路。使用二极管可以组成最简单的调幅波检波电路。调幅波解调方法有二极管包络检波器、同步检波器。目前应用最广的是二极管包络检波器,不论哪种振幅调制信号,都可采用相乘器和低通滤波器组成的同步检波电路进行解调。但是,对普通调幅信号来说,它的载波分量被抑制掉,可以直接利用非线性器件实现相乘作用,得到所需的解调电压,而不必另加同步信号,通常将这种振幅检波器称为包络。 为了生动直观的分析检波电路,利用最新电子仿真软件Multisim11.0进行二极管包络检波虚拟实验。Multisim具有组建电路快捷、波形生动直观、实验效果理想等优点。计算机虚拟仿真作为高频电子线路实验的辅助手段,是一种很好的选择,可以加深学生对一些抽象枯燥理论的理解,从而达到提高高频电子线路课程教学质量的目的。

SAR ADC

SARADC逐次逼近寄存器型ADC设 计报告 课程名称:数模混合集成电路设计 专业(年级):集成电路设计与集成系统(09)组员(学号): 提交日期:2012/12/26 序号评分规则得分 1 电路结构合理正确,工作原理描述准确详细(10分) 2 理论计算清晰准确,参数设计合理(10分) 3 仿真网表完整正确,仿真结果正确,结果说明准确详实(20分) 4 版图绘制准确,标注明确(10分) 5 撰写格式规范,结构合理,层次清晰,内容详细充实(10分)

总分

一、课程设计参数要求: 设计一个10bit 逐次逼近寄存器型模数转换器SAR ADC 分 辨 率 10bit 采样频率 100KHz 功 耗 < 1mW 电源电压 2.5V 面 积 < 1mm 2 工作温度 0~80℃ 工艺技术 0.25um 二、基本结构及原理: 1. 逐次逼近寄存器型模数转换器(SAR ADC )整体结构: 2. 逐次逼近寄存器型模数转换器(SAR ADC )工作原理: SAR ADC 其基本结构如图1所示,包括采样保持电路(S/H)、比较器(COMPARE)、数/模转换器(DAC)、逐次逼近寄存器(SAR REGISTER)和逻辑控制单元(SAR LOGIC)。模拟输入电压V IN 由采样保持电路采样并保持,为实现二进制搜索算法,首先由SAR LOGIC 控制N 位寄存器设置在中间刻度,即令最高有效位MSB 为“1”电平而其余位均为“0”电平,此时数字模拟转换器DAC 输出电压V DAC 为0.5V REF ,其中V REF 为提供给ADC 的基准电压。由比较器对V IN 和V DAC 进行比较,若V IN >V DAC ,则比较器输出“1”电平,N 位寄存器的MSB 保持“1”电平;反之,若V IN 峰值包络检波器检波原理及失真分析 【摘要】峰值包络检波器是由二极管,电阻,电容组成,电路结构十分简单。检波原理是信号源通过二级管向负载电容C充电和负载电容C对负载电阻R放电 按高频周期作锯齿状波动,其平均值的过程,当C的充放电达到动态平衡后,V 是稳定的,且变化规律与输入调幅信号的包络变化规律相同,从而实现了AM信号的解调。峰值包络检波会带来失真,包括惰性失真和负峰切割失真。现在应用不多,但对调幅解调的了解有很大的帮助。 【关键词】 包络检波锯齿状原理失真惰性负峰切割 前言 随着科技的发展,无线电通信在如今应用非常广泛 ,正如现在广泛使用的对讲机一样,即时沟通、经济实用、运营成本低、使用方便 , 同时还具有组呼通播、系统呼叫、机密呼叫等功能。在处理紧急突发事件中,在进行调度指挥中其作用是其他通信工具所不能比拟的。因此,为了更好的理解在高频电子线路中所学的知识和为以后的工作实践打好基础,我们三人借课程设计之际设计了一款峰值包络检波器。 一、实验电路 实验电路图: 图1 峰值包络检波器原理图 二、工作原理 (1)实验波形如图: 图2 峰值包络检波波型图 RC 电路有两个作用:一是作为检波器的负载;在两端产生解调输出的原调制信号电压;二是滤除检波电流中的高频分量。为此,RC 网络必须满足 R C c <<ω1 且 R C >>Ω1 。式中,c ω为载波角频率,Ω为调制角频率。 1.v s 正半周的部分时间(φ<90o ) 二极管导通,对C 充电,τ充 =R D C 。因为 R D 很小,所以τ充很小,v o ≈v s 2.v s 的其余时间(φ>90o ) 二极管截止,C 经R 放电,τ放=RC 。因为 R 很大,所以τ放很大,C 上电压下 降不多,仍有:v o ≈v s 1 ,2过程循环往复,C 上获得与包络(调制信号)相一致的电压波形,有很小的起伏。故称包络检波。 检波过程实质上是信号源通过二级管向负载电容C 充电和负载电容C 对负载电阻R 放电的过程,充电时间常数为R d C ,R d 为二极管正向导通电阻。 放电时间常数为RC ,通常R>R d ,因此对C 而言充电快、放电慢。经过若干个周期后,检波器的输出电压V 0在充放电过程中逐步建立起来,该电压对二极管VD 形成一个大的负电压,从而使二极管在输入电压的峰值附近才导通,导通时间很短,电流导通角很小。当C 的充放电达到动态平衡后,V 0按高频周期作锯齿状波动,其平均值是稳定的,且变化规律与输入调幅信号的包络变化规律相同,从而实现了AM 信号的解调。 (2)指标分析 因v s 幅度较大,用折线法分析。 1. v s 为等幅波 包络检波器波形: ADC Successive Approximation ()的设计 SAR ADC 李福乐 清华大学微电子所 2012 提纲?引言 ?DAC设计 –DAC类型 –CDAC分段结构 –CDAC电容失配与校准?比较器设计 –比较器类型 –比较器失调与噪声?SAR逻辑设计 –同步逻辑 –异步逻辑 ?实验 SAR ADC Principle ?以D/A来实现A/D, 逐次逼近 ?需要N次D/A和比较实现1次N位A/D 转换 ?精度主要由DAC决定 ?无运放,低电压、低功耗 ?深亚微米CMOS工艺下很有发展潜 艺下很有发展潜 力的结构 ?超低功耗,高速转换是研究热点 –异步时序控制 可实现性能 8~16 bit Time‐interleaved xk~ x00M S/s 9‐b, 50MS/s, 65fJ/conv. 9‐b, 40MS/s, 54fJ/conv. 10‐ 10MS/s, 11fJ/conv. 0b,0MS/s,fJ/conv. No Time‐interleaved! SAR的功耗优势 实际上在中低分辨 率上异步SAR结构 主要N i t 的速度已逼近Pipeline结构 Nyquist结构ADC的比较 Ref: Shuo‐Wei Michael Chen. JSSC 2006.12 提纲?引言 ?DAC设计 –DAC类型 –CDAC分段结构 –CDAC电容失配与校准?比较器设计 –比较器类型 –比较器失调与噪声?SAR逻辑设计 –同步逻辑 –异步逻辑 ?实验 DAC topologies 二进制电流型 电压型电压改 进型 电流型 R2R 阻容混合型 电荷型 匹配好;低功耗 10b-200ksps-SAR-ADC设计说明 一、目前项目的设计需求 目前项目属于COST-DOWN项目,所以电路面积是最主要的优化点,目前该ADC 的指标要求是10b-200Ksps,精度适中,速度比较低,关键是如何减小面积降低成本且能保证10b的模数转换有效位。项目之前采用的SMIC SAR ADC IP,需要外接电阻,整体面积是0.17mm2,本次设计的主要目的是设计不需要外挂电阻的SAR ADC且整体电路的面积小于0.17mm2。本项目中的SAR ADC针对的是单端应用,所以后续所有的讨论只针对单端应用情况。 二、各种SAR ADC架构比较及选定 图1、单端SAR ADC基本架构 图2、电阻分压型DAC结构 SAR ADC的基本架构如图1所示,该类型SAR ADC中的关键点是比较器的OFFSET 和DAC的线性度。比较器的失调对于所有类型的SAR ADC具有共性,最后统一说明。 1、针对不同的DAC架构分别说明其线性度、面积等优缺点。 ?电阻分压实现DAC的传统架构: 如图2所示,该类型的由开关电阻阵列构成的电压按比例缩放D/A转换器,由于抽头电压不可能低于下面的抽头,因此保持了很好的单调性。但是当D/A转换器的位分辨率提高时,开关数和电阻数均呈指数上升,面积难以接受。而且,由于该DAC不能采样保持输入电压,因此信号输入端需要专门的采样保持电路用于维持ADC转换期间VIN 电压的相对固定,这进一步增加了面积。此外,此类型的DAC转换精度依赖于电阻的匹配精度,在芯片内部,电阻的匹配精度低于电容的匹配精度。综合以上因素,该类型的DAC只适合应用于转换位数较小的SAR ADC中。 图3、二进制电流型DAC结构 ?二进制电流型DAC架构 如图3所示,逐次逼近逻辑产生数字码控制电流源的开关,从而使得不同大小的电流与输入端产生的电流做减法运算,从而得到比较器的输出串行码。该结构的DAC受限于电阻、MOS管的匹配程度,而且随着位数的增加电流镜结构也会导致比较大的功耗。在高精度的SAR ADC架构中不宜采用此类DAC。 包络检波器的设计与实 现 Company Document number:WTUT-WT88Y-W8BBGB-BWYTT-19998 目录 前言 (1) 4总结 5参考文献 前言 调幅波的解调即是从调幅信号中取出调制信号的过程,通常称为检波。广义的检波通常称为解调,是调制的逆过程,即从已调波提取调制信号的过程。对调幅波来说是从它的振幅变化提取调制信号的过程;对调频波,是从它的频率变化提取调制信号的过程;对调相波,是从它的相位变化提取调制信号的过程。 工程实际中,有一类信号叫做调幅波信号,这是一种用低频信号控制高频信号幅度的特殊信号。为了把低频信号取出来,需要专门的电路,叫做检波电路。使用二极管可以组成最简单的调幅波检波电路。调幅波解调方法有二极管包络检波器、同步检波器。目前应用最广的是二极管包络检波器,不论哪种振幅调制信号,都可采用相乘器和低通滤波器组成的同步检波电路进行解调。但是,对普通调幅信号来说,它的载波分量被抑制掉,可以直接利用非线性器件实现相乘作用,得到所需的解调电压,而不必另加同步信号,通常将这种振幅检波器称为包络。 为了生动直观的分析检波电路,利用最新电子仿真软件进行二极管包络检波虚拟实验。Multisim具有组建电路快捷、波形生动直观、实验效果理想等优点。计算机虚拟仿真作为高频电子线路实验的辅助手段,是一种很好的选择,可以加深学生对一些抽象枯燥理论的理解,从而达到提高高频电子线路课程教学质量的目的。 1设计目的及原理 设计目的和要求 通过课程设计,使学生加强对高频电子技术电路的理解,学会查寻资料﹑方案比较,以及设计计算等环节。进一步提高分析解决实际问题的能力,创造一个动脑动手﹑独立开展电路实验的机会,锻炼分析﹑解决高频电子电路问题的实际本领,真正实现由课本知识向实际能力的转化;通过典型电路的设计与制作,加深对基本原理的了解,增强学生的实践能力。 要求:掌握串、并联谐振回路及耦合回路、高频小信号调谐放大器、高频功率放大器、混频器、幅度调制与解调、角度调制与解调的基本原理,实际电路设计及仿真。 设计要求及主要指标:用检波二极管设计一AM信号包络检波器,并且能够实现以下指标。 输入AM信号:载波频率200kHz正弦波。 集成电路设计方法三、电路设计-SAR ADC 李福乐 清华大学微电子所 提纲?引言 ?DAC设计 –DAC类型 –CDAC分段结构 –CDAC电容失配与校准?比较器设计 –比较器类型 –比较器失调与噪声?SAR逻辑设计 –同步逻辑 –异步逻辑 ?实验 SAR ADC Principle ?以D/A来实现A/D, 逐次逼近 ?需要N次D/A和比较实现1次N位A/D 转换 ?精度主要由DAC决定 ?无运放,低电压、低功耗 ?深亚微米CMOS工艺下很有发展潜 艺下很有发展潜 力的结构 ?超低功耗,高速转换是研究热点 –异步时序控制 可实现性能 8~16 bit Time‐interleaved xk~ x00M S/s 9‐b, 50MS/s, 65fJ/conv. 9‐b, 40MS/s, 54fJ/conv. 10‐ 10MS/s, 11fJ/conv. 0b,0MS/s,fJ/conv. No Time‐interleaved! SAR的功耗优势 实际上在中低分辨 率上异步SAR结构 主要N i t 的速度已逼近Pipeline结构 Nyquist结构ADC的比较 Ref: Shuo‐Wei Michael Chen. JSSC 2006.12 提纲?引言 ?DAC设计 –DAC类型 –CDAC分段结构 –CDAC电容失配与校准?比较器设计 –比较器类型 –比较器失调与噪声?SAR逻辑设计 –同步逻辑 –异步逻辑 ?实验 DAC topologies 二进制电流型 电压型电压改 进型 电流型 R2R 阻容混合型 电荷型 匹配好;低功耗 由非线性器件和低通滤波器两部分组成。(图9-17 p244) 要求: R>>R 以保证: i充>>i放,即:τ充<<τ放 D , 一、工作原理(图9-18 p244) v s为已调信号,v o为包络检波信号 1.v s正半周的部分时间(φ<90o) 二极管导通,对C充电,τ充=R D C ∵R D很小 ∴τ充很小,v o≈v s 2.v s的其余时间(φ>90o) 二极管截止,C经R放电,τ放=RC ∵R很大 ∴τ放很大,C上电压下降不多,仍有:v o≈v s 1.2.过程循环往复,C上获得与包络(调制信号)相一致的电压波形,有很小的起伏。 故称:包络检波。 二、指标分析 因v s幅度较大,用折线法分析。 1. v s为等幅波 包络检波器波形(图9-19 p245) 2. v s为AM信号 v s=V s(1+m cosΩt)cosωo t 因为Ω<<ωo,所以包络变化缓慢,在ωo的几个周期内: V s'≈V s(1+m cosΩt)=常数(恒定值) 代入: v o=V s'cosφ≈V s(1+m cosΩt)cosφ =V s cosφ+m cosφcosΩt 式中: V s cosφ为与v o幅度成正比的AGC电压vΩ=m cosφcosΩt=VΩ'cosΩt (原调制信号) 实例:收音机中的检波电路(图9-25 p252) 3.包络检波器的指标 (1)电压传输系数 理想:R >>R D ,φ→0,K d =1 实际例: R =5.1kΩ, R D =100Ω时:φ≈33o ,K d ≈0.84 R =4.7kΩ,R D =470Ω时:φ≈55o ,K d ≈0.55 通常取:K d =0.5(-6dB)来估算检波器效率 (2)等效输入电阻 经推导:R i =R /(2K d ) 理想:K d =1时,R i =R /2 实际:K d <1 ,R i 更大(对前级有利)。 (3)非线性失真 原因: ①v s 较小时,工作于非线性区; ②R 较小时,R D 的非线性作用↑。 解决:R 足够大时,R D 的非线性作用↓,R 的直流电压负反馈作用↑。但R (RC )过大时,将产生: (a) 惰性失真(τ放 跟不上v s 的变化); 1 关键名词解释 (1) 2 功能概述 (1) 3 工作原理及电路性能分析 (3) 3.1 数字部分 (3) 3.2 模拟部分 (3) 3.2.1 关于采样精度和采样时间 (3) 3.2.2 比较器 (4) 3.2.3 可变增益结构 (6) 3.2.3 模拟部分仿真结果 (9) 4 验证结果分析 (11) 4.1 TT 25℃的仿真结果 (11) 4.2 SS 85℃的仿真结果 (13) 4.3 SS 125℃的仿真结果 (14) 4.4 FF -55℃的仿真结果 (16) 4.5 FF -40℃的仿真结果 (18) 4.6总体电气特性表 (21) 4.7仿真环境说明 (22) 图目录 图2. 1 系统结构 (1) 图3. 1 采样期间的第一级比较器的结构图 (4) 图3. 2 8位ADC的比较器的结构图 (4) 图3. 3 ss情况下比较器的仿真结果分析 (5) 图3. 4 ss情况下比较器的仿真结果分析 (6) 图3. 5 待采样保持电路的第一级 (7) 图3. 6 (a)Mn和Mp未开;(b)Mn和Mp导通,DAC电压接入时的情况 (7) 图3. 7 (1)比较器Vp端的输入 (2) 比较器Vn端的输入 (7) 图3. 8 电荷转移图 (8) 图4. 1 TT 25℃,差分输入负电压情况下 (11) 图4. 2 TT 25℃,差分输入正电压情况下 (12) 图4. 3 TT 25℃,单端输入情况下 (12) 图4. 4 SS 2.7v 85℃,双端输入负电压 (13) 图4. 5 SS 2.7v 85℃,双端输入正电压 (13) 图4. 6 SS 2.7v 85℃,单端输入正电压 (14) 图4. 7 SS 2.7v 125℃,双端输入负电压 (15) 图4. 8 SS 2.7v 125℃,双端输入正电压 (15) 图4. 9 SS 2.7v 125℃,单端输入 (16) 图4. 10 FF 3.6v -55℃,双端输入负电压 (17) 图4. 11 FF 3.6v -55℃,双端输入正电压 (17) 图4. 12 FF 3.6v -55℃,单端输入正电压 (18) 图4. 13 FF 3.6v -40℃,双端输入负电压 (19) 图4. 14 FF 3.6v -40℃,双端输入正电压 (19) 图4. 15 FF 3.6v -40℃,单端输入正电压 (20) 《通信电子线路》课程设计说明书 包络检波器 学院电气与信息工程学院 学生姓名:罗春艳 指导教师:伍麟珺职称/学位 专业:通信工程 班级:通信1301 学号:1240340207 完成时间:2016年1月 湖南工学院通信电子线路课程设计课题任务书 学院:电气与信息工程学院专业:通信工程 摘要 调幅波的解调即是从调幅信号中取出调制信号的过程,通常称为检波。检波广义的检波通常称为解调,是调制的逆过程,即从已调波提取调制信号的过程。对调幅波来说是从它的振幅变化提取调制信号的过程;对调频波,是从它的频率变化提取调制信号的过程;对调相波,是从它的相位变化提取调制信号的过程。 工程实际中,有一类信号叫做调幅波信号,这是一种用低频信号控制高频信号幅度的特殊信号。为了把低频信号取出来,需要专门的电路,叫做检波电路。使用二极管可以组成最简单的调幅波检波电路。调幅波解调方法有二极管包络检波器、同步检波器。目前应用最广的是二极管包络检波器,不论哪种振幅调制信号,都可采用相乘器和低通滤波器组成的同步检波电路进行解调。但是,普通调幅信号来说,它的载波分量被抑制掉,可以直接利用非线性器件实现相乘作用,得到所需的解调电压,而不必另加同步信号,通常将这种振幅检波器称为包络。 为了生动直观的分析检波电路,利用了最新电子仿真软件Multisim11.0进行二极管包络检波虚拟实验,Multisim具有组建电路快捷、波形生动直观、实验效果理想等优点。计算机虚拟仿真作为高频电子线路实验的辅助手段,是一种很好的选择,可以加深学生对一些抽象枯燥理论的理解,从而达到提高高频电子线路课程教学质量的目的。 关键词:调幅波;包络;检波电路 逐次逼近寄存器型ADC调研报告 课程名称:数模混合集成电路设计 专业(年级):集成电路设计与集成系统(2011)组员(学号):某某某(********) 某某某(********) 某某某(********) 提交日期:2014年10月13日 一、组员分工查阅文献情况: 引言 逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。 顾名思义,SAR ADC实质上是实现一种二进制搜索算法。所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。 1. SAR ADC的架构 尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。模拟输入电压(VIN)由采样/保持电路保持。为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1)。这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。然后,比较判断VIN是小于还是大于VDAC。如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。这个过程一直持续到LSB。上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内[1-1]。 图1. 简单的N位SAR ADC架构 图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。本例中,第一次比较表明VIN < VDAC。所以,位3置为0。然后DAC被置为01002,并执行第二次比较。由于VIN > VDAC,位2保持为1。DAC置为01102,执行第三次比较。根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。最后,由于VIN > VDAC,位0确定为1[1-2]。 第三讲 奇解与包络(4课时) 目的要求:了解包络和奇解的定义,掌握包络和奇解的之间的关系,掌握奇解的求法。 重点:包络和奇解的求法。 难点:奇解及其求法。 教学方法:讲练结合法、启发式与提问式相结合教学法。 教学手段:传统板书与多媒体课件辅助教学相结合。 教学过程: 本节讨论常微分方程的奇解以及奇解的求法。 2.4.1奇解 在本章节的例2中,我们已经看到方程2 33dy y dx =的通解是3()y x C +,还有一解0y =,除解0y =外,其余解都满足唯一性,只有解0y =所对应的积分曲线上的点的 唯一性都被破坏. 这样的解在许多方程中存在. 例1 求方程 21dy y dx =- 的所有解. 解 该方程的通解是 sin()y x C =+ 此外还有两个特解1y =和1y =-。由于该方程右端函数的根号前只取+号,故积分曲线如图2-13所示, 图 2-13 显然解1y =和1y =-所对应的积分曲线上每一点,解的唯一性均被破坏。 本节主要讨论一阶隐式方程 (,,)0F x y y '= 和一阶显式方程 (,)dy f x y dx = 的解唯一性受到破坏的情形,显然这样的解只能存在于方程不满足解的存在唯一性定理条件的区域内。 对于方程,由定理,这样的区域可用f y ??无界去检验,而对于隐式方程,一般来说,若能解出几个显式方程 (,),1,2,,i dy f x y i k dx ==L 那么对每一个方程,应用定理即可。 其次对于方程,如果函数(,,)F x y y '对所有变量连续且有连续偏导数,并且在 000 (,,)x y y '的邻域内有 000 000 (,,)0(,,)0y F x y y F x y y ''=??''≠? 成立,那么应用数学分析中的隐函数定理,可解得 (,)y f x y '= 其中函数(,)f x y 是连续的且有连续偏导数,特别有 y y F f y F ' '?=- '? 这样一来,对方程初值解的存在唯一性定理的条件也就清楚了。 因此,我们可以 就方程或给出奇解的定义。 定义 如果方程存在某一解,在它所对应的积分曲线上每点处,解的唯一性都被破坏,则称此解为微分方程的奇解。奇解对应的积分曲线称为奇积分曲线。 由上述定义,可见节例2中的解0y =是方程2 33dy y dx =的奇解,而例1中的解1y =和1y =- 是方程 dy dx =的奇解。 2.4.2 不存在奇解的判别法 假设方程的右端函数(,)f x y 在区域2 D R ?上有定义,如果(,)f x y 在D 上连续且 (,)y f x y '在D 上有界(或连续),那么由本章定理,方程的任一解是唯一的,从而在D 内 一定不存在奇解。 如果存在唯一性定理条件不是在整个(,)f x y 有定义的区域D 内成立,那么奇解只 SAR ADC 驱动运算放大器的选择 作者:德州仪器 Rick Downs 与 Miroslav Oljaca 运算放大器输出级极限 运算放大器的轨至轨运行是指其输入级或输出级,或者是指其输入级和输出级。作为驱动 SAR ADC 输入端的一个缓冲器,我们更关注的是运算放大器轨至轨的输出能力。一般说来,该输出能力表明了输出级能够接近电源轨的程度。该参数可在大多数低频或 DC 输出信号产品说明书中找到,因此更好地了解输出摆幅能力,将有助于在既定条件下驱动 ADC 输入端时,确定最佳工作点。 为了确定输出级极限,应事先开展如下测量工作:对于电源电压为 5V 的轨至轨运算放大器来说,输入信号的偏移为 2.5V 或为电源电压的一半。该运算放大器应事先在电压跟随器(或增益为 +1)配置中予以设置。峰至峰输入 AC 信号振幅从0 提高到了 5V,达到了电源电压电平。当输出级达到其极限时,则可以显示出不同的峰至峰输出电压在运算放大器输出端的总谐波失真与噪声 (THD+N) 的测量情况(请参阅图 1)。 图 1:测量得出的运算放大器输出信号 通常情况下,当信号振幅增大时,低频信号 (1kHz)、总谐波失真保持不变。只有当输出电压和电源轨之间的差值低于 10mV 时,才会导致性能显著下降。而当输出信号频率增加时,输出电压和电源电压之间的差值也会随之增大。对于 10kHz 的信号而言,当上述电压差值低于 200mV时,相关性能才开始下降;对于 20kHz 的信号而言,当上述电压差值低于 300mV 时,相关性能才开始下降;以此类推。如果要保持相关性能不变,当频率增大时,则可减小输出信号的摆幅。如欲了解有关的测量结果,敬请参阅图 2。 ETPA测试系统原理 1.包络跟踪技术原理在于使放大器尽可能地在压缩区运行,因当输出功率达到峰值,即发生增益压缩时,功率放大器达到最高运行效率。功率放大器的效率峰值点和输出功率峰值点都会随着供电电压VCC的增大而增大。 2.根据包络跟踪的技术原理,我们需要找出瞬时输出功率映射与最优供电电压的对应关系,使放大器尽可能长时间处于压缩临界区。这时选择VCC供电电压对于包络跟踪非常重要。 3.包络跟踪测试系统框图 包络跟踪测试系统包括一个射频信号发生器(SMW200A)、和分析仪(FSW),用于控制功率放大器的高速数字波形发生器和一个为放大器供电的电源。 (1)DC电源:电源波形对于高带宽要求很高,经过频谱分析VCC波形的带宽至少比射频波形的大三倍;高带宽需求源于两个因素:一.VCC是射频的功率函数;二.LUT中的下限导致了削波失真。 (2)任意波形发生器不仅要较宽的带宽,还要很高的时间分辨率;任意波形发生器提供的电流不足以支持功率放大器的运行,而且电源的带宽无法满足ET的需求,解决这一问题的方法是使用功率调节器来驱动功率放大器,该功率调节器则由直流电源和任意波形发生器产生的调制VCC信号来驱动,所以VCC电压的选择对包络跟踪影响很大。 (3)仪器同步性:要保证射频信号发生器与任意波形发生器之间仪器同步,当VCC选择最优时,可以使功率放大器的PAE达到最大,但是仪器间不同步时会使VCC相对于给定的值来说太高或太低。 (4)ETPA技术的解决方式是采用非恒定的RF包络和高效的峰值功率比(PAPR) (5)包络跟踪是一种电源技术,可以改善射频功率放大器的能效,和固定功率系统不同,包络跟踪技术被广泛应用于优化射频功率放大器(PA)的功率附加效率(PAE)。 包络跟踪基础的原理与测试方案 以前手机可以待机好几天都不需要充电。现在尽管手机电池技术不断革新,然而一些新的需求,例如更多内部无线电例如更多内部射频传输、更大更高分辨率的屏幕,使得电池电量比以往任何时候都消耗的更快。因此,由于不断有新的技术应用于手机,工程师们必须持续开发出新的方法来减少电源消耗。现在,包络跟踪技术被越来越广泛地运用于优化射频功率放大器(PA)的功率附加效率(PAE),而射频功率放大器射频PA正是电池电量最主要的消耗源之一。本文介绍了怎样使用来自射频功率放大器PA的数据实现包络跟踪ET,以确定关键的包络跟踪参数。基于这些参数,工程师们提出了基于PXI的测量系统并对其进行分析,该系统可满足包络跟踪测试的严格要求。 1. 为什么选择包络跟踪技术?当输出功率达到峰值,即发生增益压缩时,功率放大器达到最高运行效率。对于典型的W-CDMA/HSPA+/LTE制式,当设备以最大输出功率运行时,效率可能高达50%。然而,由于W-CDMA和LTE等现代通信标准使用的是峰均比(PAPR)越来越高的调制信号,效率将会显著降低。而且,由于放大器的幅值响应在压缩区会变得高度非线性化,输出功率通常由于峰均比而无法达到峰值。对于LTE波形,峰均比最高可达7或8 dB,导致功率放大器以远低于最佳功率值的平均输出功率运行。 虽然有几种技术可以用来改进功率放大器的功率附加效率,以数字预失真技术(DPD)为例,但包络跟踪技术迅速引起了功率放大器厂商们的注意。事实上十年来,基站一直采用包络跟踪技术,不仅提高了效率,同时也降低了由于能量转化成热量而导致的冷却需求。 2. 包络跟踪技术的原理包络跟踪技术的原理在于使放大器尽可能地在压缩区运行。该项技术基于这一事实:功率放大器的效率峰值点和输出功率峰值点都会随着供电电压(Vcc)的变化而变化. 图1显示了不同供电电压值下,功率附加效率与输出功率的函数关系。我们可以看出峰值效率的输出功率随着供电电压的增大而增大。 包络跟踪技术的基本思路是找出瞬时输出功率映射与最优化供电电压值的对应关系,从而使放大器尽可能长时间地处于压缩临界区。理论上,运用包络跟踪技术在这种特定的放大器上得到的PAE如图1中的绿色线条所示。从图中可以看出,有效PAE远远大于采用固峰值包络检波器检波原理及失真分析

SAR ADC的设计

SAR_ADC设计架构比较及必要说明

包络检波器的设计与实现

清华大学李福乐老师集成电路设计SARADC

包络检波原理

8位 SAR ADC设计说明书

包络检波器

SAR-ADC调研报告

第二章基本定理第三讲奇解包络

SAR ADC 驱动运算放大器的选择

包络跟踪技术

包络跟踪基础的原理与测试方案