IC封装基板技术简介

IC封装基板技术

随着电子产品微小型化、多功能化和信号传输高频高速数字化,要求PCB迅速走向高密度化、高性能化和高可靠性发展。为了适应这个要求,不仅PCB迅速走向HDIBUM板、嵌入(集成)元件PCB等,而且IC封装基板已经迅速由无机基板(陶瓷基板)走向有机基板(PCB板)。有机IC封装基板是在HDI/BUM板的基础上继续‘深化(高密度化)’而发展起来的,或者说IC封装基板是具更高密度化的HDI/BUM板。

1 封装基板的提出及其类型

1.1 有机封装基板的提出

封装基板是用于把多个一级(可用二级)封装IC组件再封(组)装形成更大密度与容量的一种基板。由于这类基板的封装密度很高,因此,其尺寸都不大,大多数为≤50*70mm2。过去主要是采用陶瓷基板,现在迅速走向高密度PCB封装基板。

(1)陶瓷封装基板。

陶瓷封装基板的应用已有几十年的历史了,基优点是CTE较小,导热率较高。但是,随着高密度化、特别是信号传输高频高速数字化的发展,陶瓷封装基板遇到了严厉的挑战。

①介电常数εr大(6∽8)。

信号传输速度V是由来介电常数εr决定的,如下式可得知。

V=k·C/(εr)1/2

其中:k——为常数;C——光速。这就是说,采用较小的介电常数εr,就可以得到较高的信号传输速度。还有特性阻抗值等问题。

②密度低。L/S≥O.1mm,加上厚度厚、孔径大,不能满足IC高集成度的要求。

③电阻大。大多采用钼形成的导线,其电阻率(烧结后)比铜大三倍多或更大,发热量大和影响电气性能。

④基板尺寸不能大,影响密度和容量提高。由于陶瓷基板的脆性大,不仅尺寸不能大,

而且生产、组装和应用等都要格外小心。

⑤薄型化困难。厚度较厚,大多数为1mm以上。

⑥成本高。

(2)有机(PCB)基板。

有机(PCB)基板,刚好与陶瓷封装基板相反。

①介电常数εr小(可选择性大,大多用3∽4的材料)。

②高密度化好。L/S可达到20∽50μm,介质层薄,孔径小。

③电阻小。发热低,电气性能好。

④基板尺寸可扩大。大多数为≤70*100mm2。

⑤可薄型化,目前,双面/四层板,可达到100∽300μm。

⑥成本低。

在1991年,由日本野洲研究所开发的用于树脂密封的倒芯片安装和倒芯片键合(连接)的PCB和HDI/BUM板,这些有机封装基板和HDI/BUM板等比陶瓷基板有更优越的的有利因素和条件,使它作为IC的裸芯片封装用基板是非常合适的,特别是用于倒芯片(FC)的金属丝的封装上,既解决了封装的CTE匹配问题,又解决了高密度芯片的安装的可行性问题。

关于PCB基板的CTE较大和导热差方面,可以通过改进和选择CCL基材得到较好的解决。

1.2 IC封装基板的类型

1.2.1 IC封装基板主要的两个问题。

(1)搭载裸芯片的封装基板与所要封装元(组)件的CTE(热膨胀系数)匹配(兼容)。(2)搭载裸芯片的封装基板的高密度化,要满足裸芯片的高集成度要求。

1.2.2封装基板的三种类型。

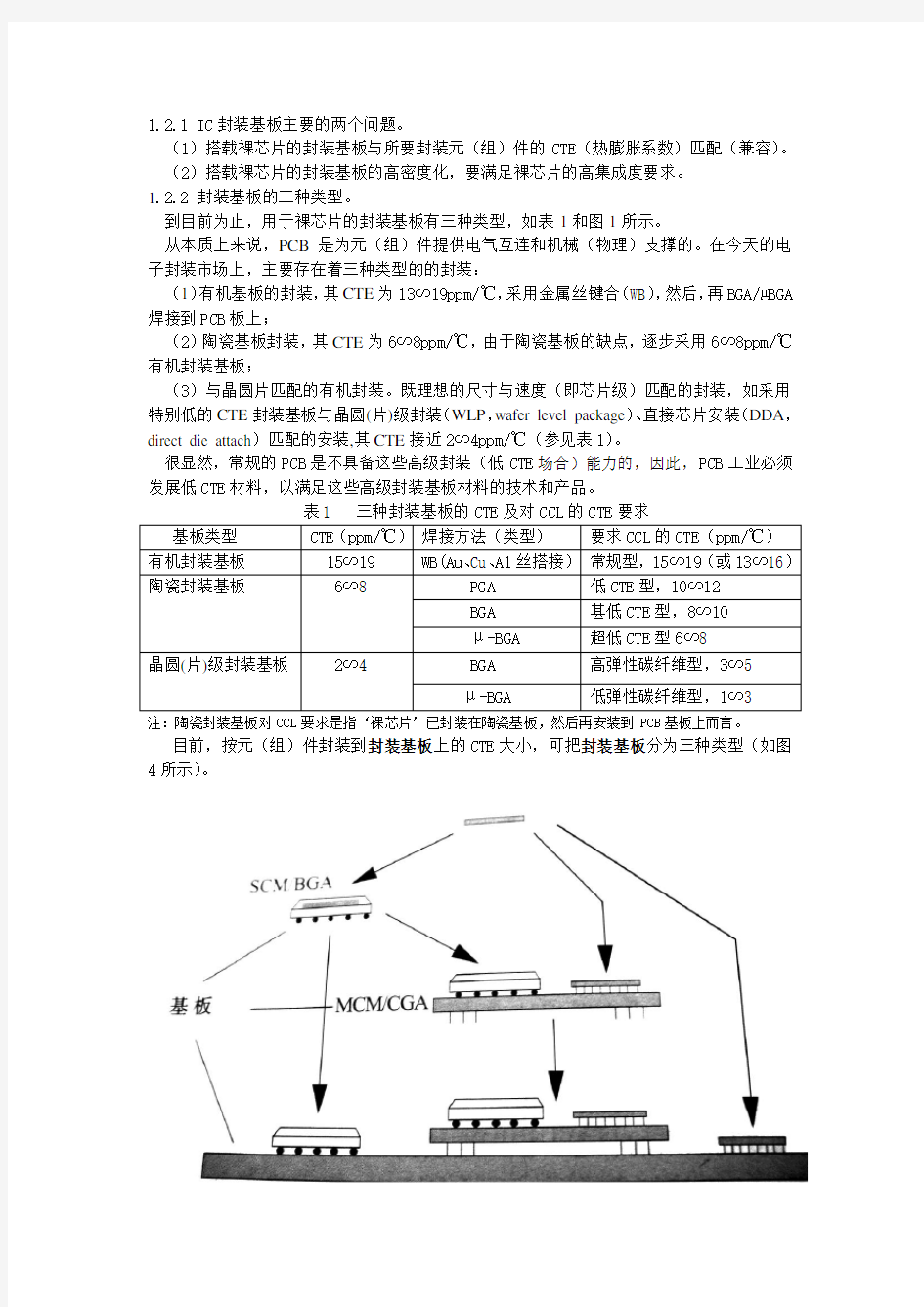

到目前为止,用于裸芯片的封装基板有三种类型,如表1和图1所示。

从本质上来说,PCB是为元(组)件提供电气互连和机械(物理)支撑的。在今天的电子封装市场上,主要存在着三种类型的的封装:

(1)有机基板的封装,其CTE为13∽19ppm/℃,采用金属丝键合(WB),然后,再BGA/μBGA 焊接到PCB板上;

(2)陶瓷基板封装,其CTE为6∽8ppm/℃,由于陶瓷基板的缺点,逐步采用6∽8ppm/℃有机封装基板;

(3)与晶圆片匹配的有机封装。既理想的尺寸与速度(即芯片级)匹配的封装,如采用特别低的CTE封装基板与晶圆(片)级封装(WLP,wafer level package)、直接芯片安装(DDA,direct die attach)匹配的安装,其CTE接近2∽4ppm/℃(参见表1)。

很显然,常规的PCB是不具备这些高级封装(低CTE场合)能力的,因此,PCB工业必须发展低CTE材料,以满足这些高级封装基板材料的技术和产品。

表1 三种封装基板的CTE及对CCL的CTE要求

基板类型CTE(ppm/℃)焊接方法(类型)要求CCL的CTE(ppm/℃)

有机封装基板15∽19 WB(Au、Cu、Al丝搭接)常规型,15∽19(或13∽16)陶瓷封装基板6∽8 PGA 低CTE型,10∽12

BGA 甚低CTE型,8∽10

μ-BGA 超低CTE型6∽8

晶圆(片)级封装基板2∽4 BGA 高弹性碳纤维型,3∽5

μ-BGA 低弹性碳纤维型,1∽3

注:陶瓷封装基板对CCL要求是指‘裸芯片’已封装在陶瓷基板,然后再安装到PCB基板上而言。

目前,按元(组)件封装到封装基板上的CTE大小,可把封装基板分为三种类型(如图4所示)。

图1 三级基板的示意图

1.2.3 基板封装与元(组)件的CTE要求。

封装基板与封装元(组)件之间的CTE匹配(兼容)问题。两者的CTE不匹配或相差甚大(如过去要求≤5ppm/℃,现在要求更高)时,焊接封装后产生的内应力便威胁着电子产品使用的可靠性和寿命。因此,封装基板与所封装元(组)件之间的CTE匹配(兼容)问题,正随着安装高密度化和焊接点面积的缩小而要求两者的CTE相差越来越小,即Δ≤5ppm/℃→Δ≤3ppm/℃→Δ≤2ppm/℃→Δ≤1ppm/℃→Δ=0。如表2所示。

表2 封装基板与所安装的元件间CTE差的要求是随着安装技术发展而不同

项目通孔插装(THT)表面安装(SMT)芯片级封装(CSP)最前端要求CTE差(ppm/℃)≤5 ≤2 ≤1∽2 0 注:CTE差(ppm/℃)是指封装基板与所封装元(组)件之间的CTE(差别)匹配度。

2 陶瓷基板封装技术。

陶瓷基板封装是把芯片(die,系指裸芯片)安装到陶瓷基板上,然后,它可以安装到PCB 基板上。首先,把硅芯片(silicon die)安装到陶瓷基板(CTE为6∽8ppm/℃)上,但是还不能安置到PCB基板上,因为PCB的CTE大小为16∽19ppm/℃,两者的CTE不匹配、差别太大。为了解决这个问题:

①大多采用圆柱形插装(column instead of balls)来解决陶瓷基板与PCB基板之间

的可靠性连接问题。因为,圆柱形引脚是高而细长的固体圆柱形针(pins),它可以随着不同膨胀而摆动,从而是有理由提供可靠的焊接点的。但是,目前常规的BGA焊接已经成为主流,要在每个连接区域除去球形(BGA)连接而改成柱形连接,那是很费时和昂贵成本为代价的,显然这不是根本的出路。

②最好而根本的办法,应该是把PCB基板的CTE=16∽19ppm/℃下降到8∽10ppm/℃或6 ∽8ppm/℃的CTE。这样,就可以不必再采用陶瓷基板了。

但是,随着IC组件的高集成度化、特别是信号传输的高频化和高速数字化的快速发展,由于陶瓷基板的(相对)介电常数大(εr=6.6),介电损耗也大,因此陶瓷封装基板的应用也受到了限制,特别是在10G以上频率的信号传输与计算,因此,其应用的领域越来越小。

3 有机基板封装技术——金属丝连(焊)接封装。

有机基板封装是把裸芯片(die,系指裸芯片)安装到很高密度的有机基板上,然后,它再安装到常规密度的大尺寸PCB基板上。即把硅芯片(silicon die)以金属丝安装(如TSOP,thin small-outline package等)有机基板(CTE为13∽19ppm/℃)上,然后再以BGA安装到常规密度的大尺寸PCB基板上,或直接应用到超小型的电子产品中,如表3所示。

表3

材料硅芯片金丝铜丝Al丝有机基板

CTE(ppm/℃)2∽414 17 21∽2316∽19,13∽15,10∽12,8∽10从表3可看出:

(1)典型的芯片的热膨胀系数CTE为2∽4ppm/℃,这就很难可以直接封装在PCB上,因为PCB的CTE大小为16∽19ppm/℃(有的文献数据为13∽15ppm/℃、13∽17ppm/℃等,这是由基材所用类型决定着),很难能够与芯片的CTE与之相匹配;

(2)采用金属丝(金的CTE为14ppm/℃、铜丝的CTE为17 ppm/℃、Al丝的CTE为21∽23ppm/℃)连(焊)接封装在不同CTE大小的有机基板(如目前大多数的IC封装基板)上,然后,再以TSOP(thin small-outline package)的金属引脚或BGA形式再在PCB基板上进行安装,因此,有机封装基板与PCB基板之间不存在着严重的CTE不匹配问题。

尽管,采用金属丝键合(连接)的有机基板封装技术,比起陶瓷基板的封装已具有很多的优点,目前正在高速发展中。但是,比起倒芯片/FCOB/DDA封装技术,仍然存在着封装面积大,连接路线长会降低信号传输速度的,对于很高速的信号传输是不理想的,一旦有机封装基板的CTE减少到2∽4ppm/℃或3∽5ppm/℃时,才会把目前的有机封装基板减少下来。

4 倒芯片/FCOB/DDA封装技术

倒芯片类型的元(组)件是具有很低的CTE,大多处在2∽4ppm/℃之间。很显然,把很低的倒芯片类型的元(组)件安装到高膨胀系数的PCB 基板上是一个巨大的挑战,特别是高密度的细小焊盘的焊接,那是关系到焊接点的可靠性问题。很小的倒芯片在传统的PCB 上的安装可行方法之一是借助于焊接部位不填充方法(underfill),但是,它限制了PCB 返工(修)的可能性。因此,要把倒芯片可靠地安装到PCB板上,必须要求PCB具有很低的CTE ,目前正在开发碳纤维的CCL基板材料。

①低--弹性模量碳纤维。用得多的是PAN碳纤维。低--弹性模量碳纤维具有接近于-0.4ppm/℃,当与树脂结合起来形成的复合材料,其CTE可达到4.5∽6.5ppm/℃。这样的CTE等级已经可与传统的IC芯片的CTE(5∽7ppm/℃)严密匹配了。

②高--弹性模量碳纤维。正如大家了解的高--弹性模量碳纤维PITCH,其CTE也接近-0.4ppm/℃,但当高--弹性模量PITCH纤维与树脂形成复合材料时,其CTE为 1.0∽3.0ppm/℃。可以应用于那些要求很低CTE(2∽4ppm/℃)的IC芯片相匹配的场合。

总之,IC封装基板主要体现在:(一)基板材料的CTE更小或匹配,即此类IC基板的CTE 要明显的减小,并接近(兼容)芯片引脚的CTE,才能保证可靠性;(二)直接用于裸芯片(KGD)的封装,因此要求IC基板更高密度化;(三)封装基板的厚度薄,尺寸很小,大多数小于70*70mm;(四)大多选用薄型的低CTE基材,如PI材料、超薄玻纤布和碳纤维的CCL 材料。

5 有机封装基板的工艺技术

有机封装基板的工艺技术路线,主要有两种:(一)传统高密度的制造方法;(二)高密度的HDI/BUM方法。

2.1 有机封装基板的主要技术指标

有机封装基板的主要技术指标如下:

(1)成品外形尺寸。大多数为70*100mm

(2)基板层数,目前为2∽4。

(3)基板厚度,0.1∽0.3mm。

(4)导线宽度L/间距S。L/S≤50μm(20∽50μm)。

半加成法L/S≥40μm。

全加成法L/S≤40μm(如5μm)。

(5)孔径Φ为50∽80μm。

2.2 CCL材料

根据封装基板的组装要求和条件来选择,因此要充分了解上、下游的技术指标性能与要求。如,采用Cu或Au丝连接(键合)的封装基板,应该采用对温度(包括高温焊接的耐热)尺寸稳定性,关键是翘曲度问题,或CTE匹配问题。

(1)CTE小、Tg高的材料。如BT材料、PI材料、改性/高Tg环氧材料等。

(2)薄型基材。即薄型玻纤布所形成的CCL。如0.1∽0.3mm。

2.3 微小孔的形成

(1)钻/蚀孔。主要有机械钻孔和激光蚀孔。

①机械钻孔。采用高速钻机,转速为20∽30万转/分,可达到Φ50∽80μ。m

②激光蚀孔。(一)红外(UV)激光蚀孔,光波长(9.6μm/10.6μm)孔的厚/径比受到限制(应≤0.5,否则,问题多),现在已经可提供LG—PP材料。RCC材料有缺点,介质厚度难保证(特别是均匀性)。(二)紫外(UV)激光,可不开‘窗口’,提高位置度,光波短(大多采用0.365μm),孔径可更小。功率较低,生产率较低。目前已经提高到6∽8瓦,这个问题已得到解决。

(2)孔化/电镀。

采用常规孔金属化工艺和电镀铜填孔技术是可以完成的

2.4 图形转移技术

(1)L/S微小化。减少侧蚀和提高精细度:

①图形电镀(含填孔镀),解决均匀性电镀,然后蚀刻。

②铜箔减薄(≤6μm),然后图形电镀(含填孔镀)/或全板镀,蚀刻形成。

③在介质是完成孔金属化和电镀(含填孔),然后蚀刻。

(2)曝光掩膜

①常规菲林。不适宜,不能满足尺寸精细堵要求。

②玻璃底片。不适宜操作。

③铬片。适宜。

(1)蚀刻抗蚀剂。

①干膜。厚度应选≤25μm(80∽120mj/cm2)。

②采用激光直接成像用干膜(8∽12mj/cm2)。

(4)激光直接刻像。注意保证介质层厚度。

2.5 表面涂(镀)覆

一般情况下,表面涂(镀)覆层大多数采用化学镀镍/浸金,现在也可是采用化学镀银。当然,采用化学(或电镀)镍/金/钯,更好。

①化学镀镍/浸金。金层要厚,并属软金,其厚度应≥0.15μm或更厚,因为金丝是键合(焊接)在金层上的。如果采用铜丝键合(焊接)是可以用薄金的。

②化学镀银。银是可以与金、铜丝键合(焊接),但银的厚度要厚些,应≥0.30μm。而化学镀银是不能与Al丝键合(焊接)的。

....

电子元件封装大全及封装常识

电子元件封装大全及封装常识 2010-04-12 19:33 一、什么叫封装 封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳。它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。 衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。封装时主要考虑的因素: 1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1; 2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能; 3、基于散热的要求,封装越薄越好。 封装主要分为DIP双列直插和SMD贴片封装两种。从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC (小外形集成电路)等。从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。 封装大致经过了如下发展进程: 结构方面:TO->DIP->PLCC->QFP->BGA ->CSP; 材料方面:金属、陶瓷->陶瓷、塑料->塑料; 引脚形状:长引线直插->短引线或无引线贴装->球状凸点; 装配方式:通孔插装->表面组装->直接安装 二、具体的封装形式 1、 SOP/SOIC封装 SOP是英文Small Outline Package 的缩写,即小外形封装。SOP封装技术由1968~1969年菲利浦公司开发成功,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。 2、 DIP封装 DIP是英文 Double In-line Package的缩写,即双列直插式封装。插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。 < 1 > 3、 PLCC封装 PLCC是英文Plastic Leaded Chip Carrier 的缩写,即塑封J引线芯片封装。PLCC封装方式,外形呈正方形,32脚封装,四周都有管脚,外形尺寸比DIP封装小得多。PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。 4、 TQFP封装 TQFP是英文thin quad flat package的缩写,即薄塑封四角扁平封装。四边扁平封装(TQFP)

电子元件封装大全及封装常识

修改者:林子木 电子元件封装大全及封装常识 一、什么叫封装 封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连 接.封装形式是指安装半导体集成电路芯片用的外壳。它不仅起着安装、固定、 密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线 连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连 接,从而实现内部芯片与外部电路的连接。因为芯片必须与外界隔离,以防止空 气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也 更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与 之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。 衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比 值越接近1 越好。封装时主要考虑的因素: 1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1; 2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性 能; 3、基于散热的要求,封装越薄越好。 封装主要分为DIP 双列直插和SMD 贴片封装两种。从结构方面,封装经历了最 早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP 公司开发出了SOP 小外型封装,以后逐渐派生出SOJ(J 型引脚小外形封装)、 TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、 TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电 路)等。从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作 条件需求的电路如军工和宇航级别仍有大量的金属封装。 封装大致经过了如下发展进程: 结构方面:TO->DIP->PLCC->QFP->BGA ->CSP; 材料方面:金属、陶瓷->陶瓷、塑料->塑料; 引脚形状:长引线直插->短引线或无引线贴装->球状凸点; 装配方式:通孔插装->表面组装->直接安装 二、具体的封装形式 1、SOP/SOIC 封装 SOP 是英文Small Outline Package 的缩写,即小外形封装。SOP 封装技术由 1968~1969 年菲利浦公司开发成功,以后逐渐派生出SOJ(J 型引脚小外形封 装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、 TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电 路)等。 SOP(Small Out-Line package) 也叫SOIC,小外形封装。表面贴装型封装之一, 引脚从封装两侧引出呈海鸥翼状(L 字形)。材料有塑料和陶瓷两种。SOP 除了用 于存储器LSI 外,也广泛用于规模不太大的ASSP 等电路。在输入输出端子不 超过10~40 的领域,SOP 是普及最广的表面贴装封装。引脚中心距 1.27mm,引脚数从8~44。另外,引脚中心距小于1.27mm 的SOP 也称为SSOP;装配 高度不到1.27mm 的SOP 也称为TSOP。还有一种带有散热片的SOP。

常用电子元件封装

常用电子元件封装 电阻:RES1, RES2, RES3, RES4;封装属性为axial系列 无极性电容:cap;封装属性为RAD-0.1到rad-0.4 电解电容:electroi;封装属性为rb.2/.4至到rb.5/1.0 电位器:pot1,pot2 ;封装属性为vr-1到vr-5 二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率) 三极管:常见的封装属性为to-18 (普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805 , 7812 , 7820等 79 系列有7905 , 7912 , 7920 等 常见的封装属性有to126h和to126v 整流桥:BRIDGE1,BRIDGE2:封装属性为 D 系列(D-44 , D-37 , D-46 )电阻:AXIAL0.3- AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4 瓷片电容:RAD0.1-RAD0.3。其中0.1-0.3指电容大小,一般用RAD0.1 电解电容:RB.1/.2- RB.4/.8 其中.1/.2-.4/.8 指电容大小。一般<100uF用 RB.1/.2,100uF-470uF 用RB.2/.4,>470uF 用RB.3/.6 二极管:DIODE0.4-DIODE0.7 其中0.4-0.7 指二极管长短,一般用DIODE0.4 发光二极管:RB.1/.2 集成块:DIP8-DIP40,其中8 —4 0指有多少脚,8脚的就是DIP8 贴片电阻 0603表示的是封装尺寸与具体阻值没有关系,但封装尺寸与功率有关通常来说如下: 0201 1/20W 0402 1/16W 0603 1/10W 0805 1/8W 1206 1/4W 电容电阻外形尺寸与封装的对应关系是: 0402=1.0mmx0.5mm 0603=1.6mmx0.8mm 0805=2.0mmx1.2mm 1206=3.2mmx1.6mm 1210=3.2mmx2.5mm 1812=4.5mmx3.2mm 2225=5.6mmx6.5mm 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。是纯粹的空间概念 因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装。像电阻,有传统的 针插式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD元件放上,即可焊接在电 路板上了。 关于零件封装我们在前面说过,除了DEVICE。LIB库中的元件外,其它库的元件都已 经有了固定的元件封装,这是因为这个库中的元件都有多种形式:以晶体管为例说明一下:晶体管是我们常用的的元件之一,在DEVICE。LIB库中,简简单单的只有NPN与PNP 之分,但实际上,如果它是NPN的2N3055那它有可能是铁壳子的TO—3,如果它是NPN 的2N3054,则有可能是铁壳的TO-66或T0-5,而学用的CS9013,有TO-92A , TO-92B ,

电子元器件封装技术详细介绍

电子元器件封装技术详细介绍 电子元器件封装技术详细介绍 1、BGA(ballgridarray):球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚LSI用的一种封装。封装本体也可做得比QFP(四侧引脚扁平封装)小。 例如,引脚中心距为1.5mm的360引脚BGA仅为31mm见方;而引脚中心距为0.5mm的304引脚QFP为40mm见方。而且BGA不用担心QFP那样的引脚变形问题。该封装是美国Motorola公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。现在也有一些LSI 厂家正在开发500引脚的BGA。BGA的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国Motorola公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC和GPAC)。 2、BQFP(quadflatpackagewithbumper):带缓冲垫的四侧引脚扁平封装。QFP封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和ASIC等电路中采用此封装。引脚中心距0.635mm,引脚数从84到196左右(见QFP)。 3、碰焊PGA(buttjointpingridarray):表面贴装型PGA的别称(见表面贴装型PGA)。 4、C-(ceramic):表示陶瓷封装的记号。例如,CDIP表示的是陶瓷DIP。是在实际中经常使用的记号。 5、Cerdip:用玻璃密封的陶瓷双列直插式封装,用于ECLRAM,DSP(数字

电子元器件封装知识

电子元器件封装知识 电子元器件封装知识一: 1、bga(ballgridarray)球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配lsi芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(pac)。引脚可超过200,是多引脚lsi 用的一种封装。封装本体也可做得比qfp(四侧引脚扁平封装)小。例如,引脚中心距为1.5mm的360引脚bga仅为31mm见方;而引脚中心距为0.5mm的304引脚qfp为40mm见方。而且bga不用担心qfp那样的引脚变形问题。该封装是美国motorola公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,bga的引脚(凸点)中心距为1.5mm,引脚数为225。现在也有一些lsi厂家正在开发500引脚的bga。bga的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国motorola公司把用模压树脂密封的封装称为ompac,而把灌封方法密封的封装称为gpac(见ompac 和gpac)。 2、bqfp(quadflatpackagewithbumper)带缓冲垫的四侧引脚扁平封装。qfp封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在

微处理器和asic等电路中采用此封装。引脚中心距0.635mm,引脚数从84到196左右(见qfp)。 3、碰焊pga(buttjointpingridarray)表面贴装型pga的别称(见表面贴装型pga)。 4、c-(ceramic)表示陶瓷封装的记号。例如,cdip表示的是陶瓷dip。是在实际中经常使用的记号。 5、cerdip用玻璃密封的陶瓷双列直插式封装,用于eclram,dsp(数字信号处理器)等电路。带有玻璃窗口的cerdip用于紫外线擦除型eprom以及内部带有eprom的微机电路等。引脚中心距2.54mm,引脚数从8到42。在日本,此封装表示为dip-g(g即玻璃密封的意思)。 6、cerquad表面贴装型封装之一,即用下密封的陶瓷qfp,用于封装dsp等的逻辑lsi电路。带有窗口的cerquad用于封装eprom电路。散热性比塑料qfp好,在自然空冷条件下可容许1.5~2w的功率。但封装成本比塑料qfp高3~5倍。引脚中心距有1.27mm、0.8mm、0.65mm、0.5mm、0.4mm等多种规格。引脚数从32到368。 7、clcc(ceramicleadedchipcarrier)带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。带有窗口的用于封装紫外线擦除型eprom以及带有eprom的微机电路等。此封装也称为qfj、qfj-g(见qfj)。 8、cob(chiponboard板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。虽然cob是最简单的裸芯片贴装技

常用电子元件封装大全

常用电子元件封装大全 电阻:RES1,RES2,RES3,RES4;封装属性为axial系列 无极性电容:cap;封装属性为RAD-0.1到rad-0.4 电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0 电位器:pot1,pot2;封装属性为vr-1到vr-5 二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率) 三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管) 电源稳压块有78和79系列;78系列如7805,7812,7820等 79系列有7905,7912,7920等 常见的封装属性有to126h和to126v 整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46) 电阻:AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4 瓷片电容:RAD0.1-RAD0.3。其中0.1-0.3指电容大小,一般用RAD0.1 电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小。一般<100uF用 RB.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6 二极管:DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4 发光二极管:RB.1/.2 集成块:DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8 贴片电阻0603表示的是封装尺寸与具体阻值没有关系,但封装尺寸与功率有关通常来说如下: 0201 1/20W 0402 1/16W 0603 1/10W 0805 1/8W 1206 1/4W 电容电阻外形尺寸与封装的对应关系是:

常用电子元器件及封装

1 常用电子元件及封装 1、电阻 使用的贴片电阻封装常见为0603和0805两种,。一般的贴片电阻阻值精度为5%,0603封装电阻功率为1/10W,0805封装电阻功率为1/8W。中发通常100只起售 如图: 直插封装的电阻用于大功率的场合,体积越大的功率越大,一般1/4W的就够用了 2、电容 电容的容值小于等于100nF时,可以使用0603或0805封装贴片陶瓷电容。智能车上最常用的容值为100nF(104),容值精度为20%,耐压50V。 如图:

电容的容值大于100nF时,要根据应用场合的需要来选择使用贴片钽电容、贴片陶瓷电容或直插式铝电解电容。 贴片钽电容特点是贵、稳定、高频特性好。常用的容值为10uF、100uF、470 uF 等,耐压应取工作电压的二倍以上。注意使用时极性不要接反,带杠的是正极。 如图: 贴片陶瓷电容是新兴的替代小型贴片钽电容的产品,小容量(如10uF)价格较贴片钽电容便宜得多,体积基本相同。具有同样良好的高频特性和更低的内阻,但容量随温度变化大,适合用在电源的整流和去耦方面。 如图:

直插式铝电解电容最大的特点就是便宜,和其他电容相比,单位容量价格最低。它也是用于电源的整流和去耦方面,常用的容值为100uF、470uF、1000uF等。缺点是自身带有感性,使用时需并联陶瓷电容以提高高频性能。容值精度较低且随温度变化,寿命相对较短。有极性不可反接,带杠的是负极。 如图: 3、电感 电感使用1315和0808两种直插封装: 1315封装电感如下图:

0808封装电感如下图:

4、二极管

整流二极管(1N4007),高速二极管(FR157、1N4148),肖特基二极管(1N5819、1N5822),瞬态电压抑制二极管(P6KE),必须使用括号内标明的型号或用与之性能相近的型号替换,建议使用贴片封装。 发光二极管(LED)有0603、0805、1206、1210等贴片封装和Φ3、Φ5等直插封装,封装体积越大亮度越高,可承受的电流也越大。颜色自选(蓝、紫、白这三种颜色的LED较贵)。二极管带杠、带点、腿短一端为负极。

IC封装制程

半導體的產品很多,應用的場合非常廣泛,圖一是常見的幾種半導體元件外型。半導體元件一般是以接腳形式或外型來劃分類別,圖一中不同類別的英文縮寫名稱原文為 PDID:Plastic Dual Inline Package SOP:Small Outline Package SOJ:Small Outline J-Lead Package PLCC:Plastic Leaded Chip Carrier QFP:Quad Flat Package PGA:Pin Grid Array BGA:Ball Grid Array 雖然半導體元件的外型種類很多,在電路板上常用的組裝方式有二種,一種是插入電路板的銲孔或腳座,如PDIP、PGA,另一種是貼附在電路板表面的銲墊上,如SOP、SOJ、PLCC、QFP、BGA。 從半導體元件的外觀,只看到從包覆的膠體或陶瓷中伸出的接腳,而半導體元件真正的的核心,是包覆在膠體或陶瓷內一片非常小的晶片,透過伸出的接腳與外部做資訊傳輸。圖二是一片EPROM元件,從上方的玻璃窗可看到內部的晶片,圖三是以顯微鏡將內部的晶片放大,可以看到晶片以多條銲線連接四周的接腳,這些接腳向外延伸並穿出膠體,成為晶片與外界通訊的道路。請注意圖三中有一條銲線從中斷裂,那是使用不當引發過電流而燒毀,致使晶片失去功能,這也是一般晶片遭到損毀而失效的原因之一。 圖四是常見的LED,也就是發光二極體,其內部也是一顆晶片,圖五是以顯微鏡正視LED的頂端,可從透明的膠體中隱約的看到一片方型的晶片及一條金色的銲線,若以LED二支接腳的極性來做分別,晶片是貼附在負極的腳上,經由銲線連接正極的腳。當LED通過正向電流時,晶片會發光而使LED發亮,如圖六所示。 半導體元件的製作分成兩段的製造程序,前一段是先製造元件的核心─晶片,稱為晶圓製造;後一段是將晶中片加以封裝成最後產品,稱為IC封裝製程,又可細分成晶圓切割、黏晶、銲線、封膠、印字、剪切成型等加工步驟,在本章節中將簡介這兩段的製造程序。

电子元件封装形式大全要点

封装形式 BGA DIP HSOP MSOP PLCC QFN QFP QSOP S DIP SIP SOD SOJ SOP Sot SSOP TO - Device TSSOP TQFP BGA(ballgridarray) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。该封装是美国Motorola公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225.现在也有一些LSI厂家正在开发500引脚的BGA.BGA的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。 序号封装编号封装说明实物图 1 BGA封装 内存

2 CCGA 3 CPGA CerAMIc Pin Grid 4 PBGA 1.5mm pitch 5 SBGA Thermally Enhanced 6 WLP-CSP Chip Scale Package DIP(du ALI n-line package)返回 双列直插式封装。插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。引脚中心距2.54mm,引脚数从6到64.封装宽度通常为15.2mm.有的把宽度为7.52mm 和10.16mm的封装分别称为skinnyDIP和slimDIP(窄体型DIP)。但多数情况下并不加区分,只简单地统称为DIP.另外,用低熔点玻璃密封的陶瓷DIP也称为cerdip。 序号封装编号封装说明实物图 1 DIP14M3 双列直插 2 DIP16M 3 双列直插 3 DIP18M3 双列直插 4 DIP20M3 双列直插 5 DIP24M3 双列直插

电子元器件封装的基本介绍

电子元件封装的基本介绍 0805封装尺寸/0402封装尺寸/0603封装尺寸/1206封装尺寸 封装尺寸与功率关系: 0201 1/20W 0402 1/16W 0603 1/10W 0805 1/8W 1206 1/4W 封装尺寸与封装的对应关系 0402=1.0mmx0.5mm 0603=1.6mmx0.8mm 0805=2.0mmx1.2mm 1206=3.2mmx1.6mm 1210=3.2mmx2.5mm 1812=4.5mmx3.2mm 2225=5.6mmx6.5mm 贴片电阻规格、封装、尺寸 贴片电阻常见封装有9种,用两种尺寸代码来表示。一种尺寸代码是由4位数字表示的EIA(美国电子工业协会)代码,前两位与后两位分别表示电阻的长与宽,以英寸为单位。我们常说的0603封装就是指英制代码。另一种是米制代码,也由4位数字表示,其单位为毫米。下表列出贴片电阻封装英制和公制的关系及详细的尺寸:

Note:我们俗称的封装是指英制。 零件封装知识 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。是纯粹的空间概念.因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装。像电阻,有传统的针插式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD元件放上,即可焊接在电路板上了。 电阻AXIAL 无极性电容RAD 电解电容RB- 电位器VR 二极管DIODE 三极管TO 电源稳压块78和79系列TO-126H和TO-126V

IC 封装制程简介-1

半导体的产品很多,应用的场合非常广泛,图一是常见的几种半导体组件外型。半导体组件一般是以接脚形式或外型来划分类别,图一中不同类别的英文缩写名称原文为 PDID:Plastic Dual Inline Package SOP:Small Outline Package SOJ:Small Outline J-Lead Package PLCC:Plastic Leaded Chip Carrier QFP:Quad Flat Package PGA:Pin Grid Array BGA:Ball Grid Array 虽然半导体组件的外型种类很多,在电路板上常用的组装方式有二种,一种是插入电路板的焊孔或脚座,如PDIP、PGA,另一种是贴附在电路板表面的焊垫上,如SOP、SOJ、PLCC、QFP、BGA。 从半导体组件的外观,只看到从包覆的胶体或陶瓷中伸出的接脚,而半导体组件真正的的核心,是包覆在胶体或陶瓷内一片非常小的芯片,透过伸出的接脚与外部做信息传输。图二是一片EPROM组件,从上方的玻璃窗可看到内部的芯片,图三是以显微镜将内部的芯片放大,可以看到芯片以多条焊线连接四周的接脚,这些接脚向外延伸并穿出胶体,成为芯片与外界通讯的道路。请注意图三中有一条焊线从中断裂,那是使用不当引发过电流而烧毁,致使芯片失去功能,这也是一般芯片遭到损毁而失效的原因之一。 图四是常见的LED,也就是发光二极管,其内部也是一颗芯片,图五是以显微镜正视LED的顶端,可从透明的胶体中隐约的看到一片方型的芯片及一条金色的焊线,若以LED二支接脚的极性来做分别,芯片是贴附在负极的脚上,经由焊线连接正极的脚。当LED通过正向电流时,芯片会发光而使LED发亮,如图六所示。 半导体组件的制作分成两段的制造程序,前一段是先制造组件的核心─芯片,称为晶圆制造;后一段是将晶中片加以封装成最后产品,称为IC封装制程,又可细分成晶圆切割、黏晶、焊线、封胶、印字、剪切成型等加工步骤,在本章节中将简介这两段的制造程序。

PCB元件封装库命名规则简介

PCB元件封装库命名规则简介 1、集成电路(直插) 用DIP- 引脚数量+尾缀来表示双列直插封装 尾缀有N和W两种,用来表示器件的体宽 N 为体窄的封装,体宽300mil, 引脚间距2.54mm W为体宽的封装,体宽600mil,弓I脚间距2.54mm 女口:DIP-16N表示的是体宽300mil,弓I脚间距2.54mm的16引脚窄体双列直插封装 2 、集成电路(贴片) 用SO-引脚数量+尾缀表示小外形贴片封装 尾缀有N、M和W三种,用来表示器件的体宽 N 为体窄的封装,体宽150mil, 弓脚间距1.27mm M为介于N和W之间的封装,体宽208mil,弓I脚间距1.27mm W为体宽的封装,体宽300mil,引脚间距1.27mm 女口:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装 若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm 3、电阻 SMD贴片电阻命名方法为:封装+R 女口:1812R表示封装大小为1812的电阻封装 碳膜电阻命名方法为:R-封装

如:表示焊盘间距为英寸的电阻封装 水泥电阻命名方法为:R-型号 女口:R-SQP5V表示功率为5W的水泥电阻封装 4、电容 无极性电容和钽电容命名方法为:封装+C 女口:6032C表示封装为6032的电容封装 SMT独石电容命名方法为:RAD引脚间距 女口:表示的是引脚间距为200mil的SMT独石电容封装 电解电容命名方法为:RB+引脚间距/外径 如:.4 表示引脚间距为200mil, 外径为400mil 的电解电容封 装 5、二极管整流器件 命名方法按照元件实际封装,其中BAT5 4和1N4148封装为1N4148 6 、晶体管 命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成 电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名 7、晶振 HC-49S,HC-49U 为表贴封装,AT26,AT38 为圆柱封装,数字表规格尺 寸 如:AT26表示外径为2mm长度为8mm的圆柱封

电子元件封装符号

电子元件封装符号 主题:Protel 99元件封装列表 元件代号封装备注电阻 R AXIAL0.3 电阻 R AXIAL0.4 电阻 R AXIAL0.5 电阻 R AXIAL0.6 电阻 R AXIAL0.7 电阻 R AXIAL0.8 电阻 R AXIAL0.9 电阻 R AXIAL1.0 电容 C RAD0.1 方型电容电容 C RAD0.2 方型电容电容 C RAD0.3 方型电容电容 C RAD0.4 方型电容电容 C RB.2/.4 电解电容电容 C RB.3/.6 电解电容电容 C RB.4/.8 电解电容电容 C RB.5/1.0 电解电容保险丝FUSE FUSE 二极管 D DIODE0.4 IN4148 二极管 D DIODE0.7 IN5408 三极管Q T0-126 三极管Q TO-3 3DD15 三极管Q T0-66 3DD6 三极管Q TO-220 TIP42 电位器VR VR1 电位器VR VR2 电位器VR VR3 电位器VR VR4 电位器VR VR5 元件代号封装备注 插座 CON2 SIP2 2脚 插座 CON3 SIP3 3 插座 CON4 SIP4 4

插座 CON5 SIP5 5 插座 CON6 SIP6 6 插座 CON16 SIP16 16 插座 CON20 SIP20 20 整流桥堆D D-37R 1A直角封装 整流桥堆D D-38 3A四脚封装 整流桥堆D D-44 3A直线封装 整流桥堆D D-46 10A四脚封装 集成电路U DIP8(S) 贴片式封装 集成电路U DIP16(S) 贴片式封装 集成电路U DIP8(S) 贴片式封装 集成电路U DIP20(D) 贴片式封装 集成电路U DIP4 双列直插式 集成电路U DIP6 双列直插式 集成电路U DIP8 双列直插式 集成电路U DIP16 双列直插式 集成电路U DIP20 双列直插式 集成电路U ZIP-15H TDA7294 集成电路U ZIP-11H Protel 封装 Protel零件库中常用器件封装 电阻 AXIAL 无极性电容 RAD 电 解电容 RB 电位器 VR 二极管 DIODE 三极管 TO 场效应管和三极管一样 电源稳压块78和79系列 TO-126H和TO-126V 整流桥 D-44 D-37 D-46 单排多针插座 CON SIP 双列直插元件 DIP 晶振 XTAL1 电阻:RES1,RES2,可变电阻:RES3,RES4;封装属性为axial系列,AXIAL0.3-AXIAL1.0 数字表示焊盘间距

IC封装制程简介

半导体的产品很多应用的场合非常广泛图一是常见的几种半导体组件外型半导体组件一般是以接脚形式或外型来划分类别图一中不同类别的英文缩写名称原文为 PDID Plastic Dual Inline Package SOP Small Outline Package SOJ Small Outline J-Lead Package PLCC Plastic Leaded Chip Carrier QFP Quad Flat Package PGA Pin Grid Array BGA Ball Grid Array 虽然半导体组件的外型种类很多在电路板上常用的组装方式有二种一种是插入电路板的焊孔或脚座如PDIP PGA另一种是贴附在电路板表面的焊垫上如SOP SOJ PLCC QFP BGA 从半导体组件的外观只看到从包覆的胶体或陶瓷中伸出的接脚而半导体组件真正的的核心是包覆在胶体或陶瓷内一片非常小的芯片透过伸出的接脚与外部做信息传输图二是一片EPROM组件从上方的玻璃窗可看到内部的芯片图三是以显微镜将内部的芯片放大可以看到芯片以多条焊线连接四周的接脚这些接脚向外延伸并穿出胶体成为芯片与外界通讯的道路请注意图三中有一条焊线从中断裂那是使用不当引发过电流而烧毁致使芯片失去功能这也是一般芯片遭到损毁而失效的原因之一 图四是常见的LED也就是发光二极管其内部也是一颗芯片图五是以显微镜正视LED的顶端可从透明的胶体中隐约的看到一片方型的芯片及一条金色的焊线若以LED二支接脚的极性来做分别芯片是贴附在负极的脚上经由焊线连接正极的脚当LED通过正向电流时芯片会发光而使LED发亮如图六所示 半导体组件的制作分成两段的制造程序前一段是先制造组件的核心─芯片称为晶圆制造后一段是将晶中片加以封装成最后产品称为IC封装制程又可细分成晶圆切割黏晶焊线封胶印字剪切成型等加工步骤在本章节中将简介这两段的制造程序

常用电子元件封装介绍

常用电子元件封装介绍 1、BGA 封装(ball grid array) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚LSI 用的一种封装。封装本体也可做得比QFP(四侧引脚扁平封装)小。例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。而且BGA 不用担心QFP 那样的引脚变形问题。该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。现在也有一些LSI 厂家正在开发500 引脚的BGA。BGA 的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。 2、BQFP 封装(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。 3、碰焊PGA 封装(butt joint pin grid array) 表面贴装型PGA的别称(见表面贴装型PGA)。 4、C-(ceramic) 封装 表示陶瓷封装的记号。例如,CDIP表示的是陶瓷DIP。是在实际中经常使用的记号。 5、Cerdip 封装 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。引脚中心距2.54mm,引脚数从8 到42。在

SMT准则元件封装资料

SMT标准元件封装资料 SMT(Surface Mount Technology)是电子业界一门新兴的工业技术,它的兴起及迅猛发展是电子组装业的一次革命,被誉为电子业的”明日之星”,它使电子组装变得越来越快速和简单,随之而来的是各种电子产品更新换代越来越快,集成度越来越高,价格越来越便宜。为IT(Information Technology)产业的飞速发展作出了巨大贡献。 SMT零件 SMT所涉及的零件种类繁多,样式各异,有许多已经形成了业界通用的标准,这主要是一些芯片电容电阻等等;有许多仍在经历着不断的变化,尤其是IC类零件,其封装形式的变化层出不穷,令人目不暇接,传统的引脚封装正在经受着新一代封装形式(BGA、FLIP CHIP等等)的冲击,在本章里将分标准零件与IC类零件详细阐述。一、标准零件标准零件是在SMT发展过程中逐步形成的,主要是针对用量比较大的零件,本节只讲述常见的标准零件。目前主要有以下几种:电阻(R)、排阻(RA或RN)、电感(L)、陶瓷电容(C)、排容(CP)、钽质电容(C)、二极管(D)、晶体管(Q)【括号内为PCB(印刷电路板)上之零件代码】,在PCB上可根据代码来判定其零件类型,一般说来,零件代码与实际装着的零件是相对应的。 1、零件规格: (1)零件规格即零件的外形尺寸,SMT发展至今,业界为方便作业,已经形成了一个标准零件系列,各家零件供货商皆是按这一标准制造。标准零件之尺寸规格有英制与公制两种表示方法,如下表英制表示法1206 0805 0603 0402公制表示法3216 2012 1608 1005电容电阻外形尺寸与封装的对应关系是:0402=0.04inch*0.02inch=40mil*20mil=1.0mm*0.5mm 0603=0.06inch*0.03inch=60mil*30mil=1.6mm*0.8mm

电子元器件封装简介及图解

电子元器件封装简介及图解 部分元件参考封装 元件封装是指在PCB编辑器中,为了将元器件固定、安装于电路板, 而绘制的与元器件管脚相对应的焊盘、元件外形等。由于它的主要作用是将元件固定、焊接在电路板上,因此它对焊盘大小、焊盘间距、焊盘孔大小、焊盘序号等参数有非常严格的要求,元器件的封装、元器件实物、原理图元件管脚序号三者之间必须保持严格的对应关系,如图6.8所示,否则直接关系到制作电路板的成败和质量。 小技巧 一般双列直插集成电路元件封装的第一脚焊盘为方形,以便于元件安装和检测,与此对应集成块表面的第一脚位置有小点标志。由图6.8可知,元件封装一般由二部分组成:焊盘和外形轮廓,其中最关键 的组成部分是和元件管脚一一对应的焊盘,它的形状和参数如图6.9所示。焊盘的作用是将元件管脚固定焊接在电路板的铜箔导线上,因此它的各参数直接关系到焊点的质量和电路板的可靠性,一般包含如下参数:焊盘长度 (X-Size)、焊盘宽度(Y-Size)、孔径(Hole Size)、序号(Designator)、形状(Shape)等。在PCB编辑器中双击焊盘,即可打开焊盘属性对话框,可 以修改或设置焊盘各属性。在元件封装中,除了焊盘本身的参数至关重要外,焊盘之间的距离也必须严格和元件实物管脚之间距离保持一致,否则在进行元件装配、焊接时将可能存在元件无法安装等严重问题,元件封装的合理选择非常重要。

图6.8 元件封装与元件实物、原理图元件的对应关系 图6.9 PCB板中的焊盘 1 元件封装的另一组成部分为外形轮廓,相对于焊盘而言,它的参数要求 没有焊盘参数那么严格,一般就是从元件顶部向底部看下去所形成的外部轮廓俯视图,它一般在顶层丝印层(Top Overlayer)绘制,默认颜色为黄色。 外形轮廓主要用于标志元件在电路板上所占面积大小和安装极性,从而便于元件的整体布局,同时还便于元件的安装。 在Protel DXP 安装目录下的“*:\Program Files\Altium\Library\”目录中,存放着大量的PCB元件封装库,在不同的元件封装库中又含有许多不同种类、不同尺寸大小的PCB元件封装,熟练了解Protel DXP 元件封装库的各种封装是正确、快速地为元件选用合适封装的前提,而合适的选择元件封装是成功制作电路板的第一步。 元件原理图符名称库中封装名称 PCB封装符号元件实物号名称 RES2 AXIAL-0.4 电阻无极

电子元件封装大全及封装常识

电子元件封装大全及封装常识 一、什么叫封装 封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳。它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。 衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。封装时主要考虑的因素: 1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1; 2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能; 3、基于散热的要求,封装越薄越好。 封装主要分为DIP双列直插和SMD贴片封装两种。从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ (J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP (薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。 封装大致经过了如下发展进程: 结构方面:TO->DIP->PLCC->QFP->BGA ->CSP; 材料方面:金属、陶瓷->陶瓷、塑料->塑料; 引脚形状:长引线直插->短引线或无引线贴装->球状凸点; 装配方式:通孔插装->表面组装->直接安装 二、具体的封装形式 1、SOP/SOIC封装 SOP是英文Small Outline Package 的缩写,即小外形封装。SOP封装技术由1968~1969年菲利浦公司开发成功,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。 2、DIP封装 DIP是英文Double In-line Package的缩写,即双列直插式封装。插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。 < 1 > 3、PLCC封装 PLCC是英文Plastic Leaded Chip Carrier 的缩写,即塑封J引线芯片封装。PLCC封装方式,外形呈正方形,32脚封装,四周都有管脚,外形尺寸比DIP封装小得多。PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。 4、TQFP封装 TQFP是英文thin quad flat package的缩写,即薄塑封四角扁平封装。四边扁平封装(TQFP)工艺能有效利用空间,从而降低对印刷电路板空间大小的要求。由于缩小了高度和体积,这种封装工艺非常适合对空间要求较高的应用,如PCMCIA 卡和网络器件。几乎所有ALTERA的CPLD/FPGA都有TQFP 封装。 5、PQFP封装 PQFP是英文Plastic Quad Flat Package的缩写,即塑封四角扁平封装。PQFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。 6、TSOP封装 TSOP是英文Thin Small Outline Package的缩写,即薄型小尺寸封装。TSOP内存封装技术的一个典型特征