《友谊地久天长》乐曲演奏电路设计

《友谊地久天长》乐曲演奏电路设计

1. 实验任务

音高与频率的对应关系见表1-1。

表1-1

音高频率对照表

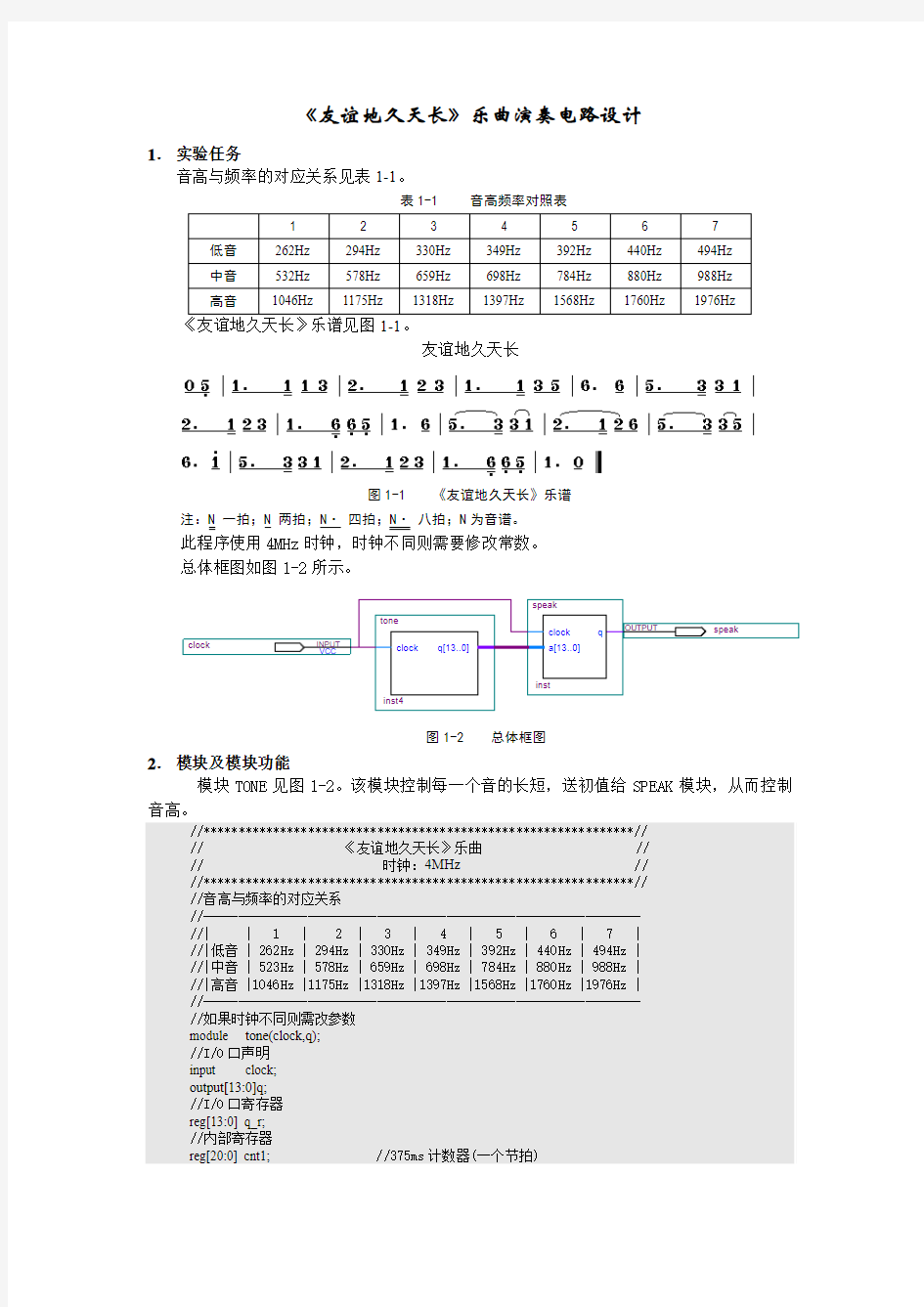

《友谊地久天长》乐谱见图1-1。

友谊地久天长

图1-1

《友谊地久天长》乐谱

注:N 一拍;N 两拍;N · 四拍;N · 八拍;N 为音谱。

此程序使用4MHz 时钟,时钟不同则需要修改常数。

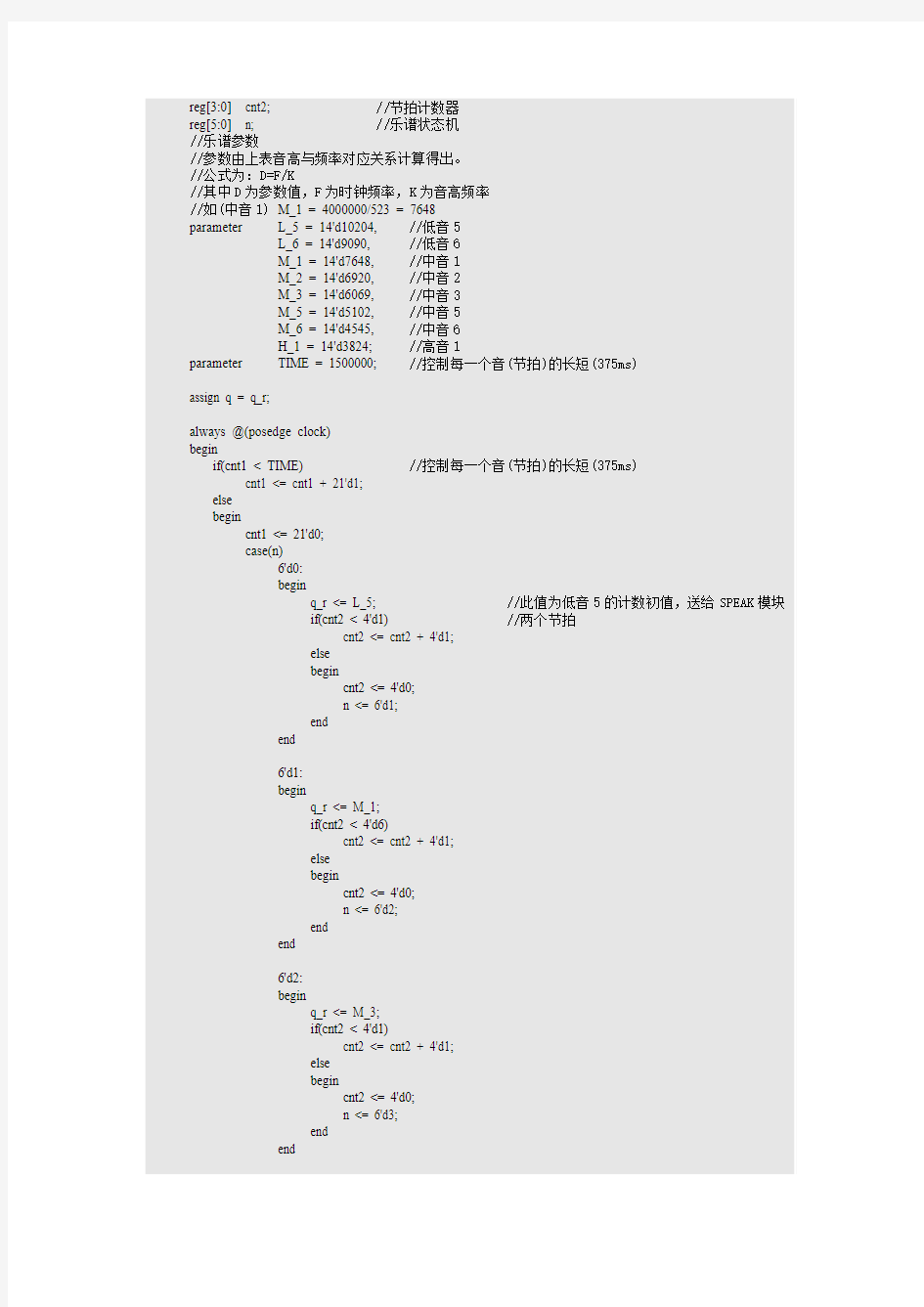

总体框图如图1-2所示。

图1-2

总体框图

2. 模块及模块功能

模块TONE 见图1-2。该模块控制每一个音的长短,送初值给SPEAK 模块,从而控制音高。

//**************************************************************// // 《友谊地久天长》乐曲 // // 时钟:4MHz // //**************************************************************// //音高与频率的对应关系

//--------------------------------------------------------------- //| | 1 | 2 | 3 | 4 | 5 | 6 | 7 | //|低音 | 262Hz | 294Hz | 330Hz | 349Hz | 392Hz | 440Hz | 494Hz | //|中音 | 523Hz | 578Hz | 659Hz | 698Hz | 784Hz | 880Hz | 988Hz | //|高音 |1046Hz |1175Hz |1318Hz |1397Hz |1568Hz |1760Hz |1976Hz | //--------------------------------------------------------------- //如果时钟不同则需改参数 module tone(clock,q); //I/O 口声明 input clock; output[13:0]q; //I/O 口寄存器 reg[13:0] q_r; //内部寄存器 reg[20:0] cnt1; //375ms 计数器(一个节拍)

reg[3:0] cnt2; //节拍计数器

reg[5:0] n; //乐谱状态机

//乐谱参数

//参数由上表音高与频率对应关系计算得出。

//公式为:D=F/K

//其中D为参数值,F为时钟频率,K为音高频率

//如(中音1)M_1 = 4000000/523 = 7648

parameter L_5 = 14'd10204,//低音5

L_6 = 14'd9090,//低音6

M_1 = 14'd7648,//中音1

M_2 = 14'd6920,//中音2

M_3 = 14'd6069,//中音3

M_5 = 14'd5102,//中音5

M_6 = 14'd4545,//中音6

H_1 = 14'd3824;//高音1

parameter TIME = 1500000; //控制每一个音(节拍)的长短(375ms)

assign q = q_r;

always @(posedge clock)

begin

if(cnt1 < TIME)//控制每一个音(节拍)的长短(375ms)

cnt1 <= cnt1 + 21'd1;

else

begin

cnt1 <= 21'd0;

case(n)

6'd0:

begin

q_r <= L_5; //此值为低音5的计数初值,送给SPEAK模块

if(cnt2 < 4'd1) //两个节拍

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd1;

end

end

6'd1:

begin

q_r <= M_1;

if(cnt2 < 4'd6)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd2;

end

end

6'd2:

begin

q_r <= M_3;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd3;

end

end

6'd3:

begin

q_r <= M_2;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd4;

end

end

6'd4:

begin

q_r <= M_1;

n <= 6'd5;

end

6'd5:

begin

q_r <= M_2;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd6;

end

end

6'd6:

begin

q_r <= M_3;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd7;

end

end

6'd7:

begin

q_r <= M_1;

if(cnt2 < 4'd4)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd8;

end

end

6'd8:

begin

q_r <= M_3;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd9;

end

end

6'd9:

begin

q_r <= M_5;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd10;

end

end

6'd10:

begin

q_r <= M_6;

if(cnt2 < 4'd9)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd11;

end

end

6'd11:

begin

q_r <= M_5;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd12;

end

end

6'd12:

begin

q_r <= M_3;

if(cnt2 < 4'd2)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd13;

end

end

6'd13:

begin

q_r <= M_1;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd14;

end

end

begin

q_r <= M_2;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd15;

end

end

6'd15:

begin

q_r <= M_1;

n <= 6'd16;

end

6'd16:

begin

q_r <= M_2;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd17;

end

end

6'd17:

begin

q_r <= M_3;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd18;

end

end

6'd18:

begin

q_r <= M_1;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd19;

end

end

6'd19:

begin

q_r <= L_6;

if(cnt2 < 4'd2)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd20;

end

6'd20:

begin

q_r <= M_5;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd21;

end

end

6'd21:

begin

q_r <= M_1;

if(cnt2 < 4'd7)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd22;

end

end

6'd22:

begin

q_r <= M_6;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd23;

end

end

6'd23:

begin

q_r <= M_5;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd24;

end

end

6'd24:

begin

q_r <= M_3;

if(cnt2 < 4'd2)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd25;

end

end

begin

q_r <= M_1;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd26;

end

end

6'd26:

begin

q_r <= M_2;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd27;

end

end

6'd27:

begin

q_r <= M_1;

n <= 6'd28;

end

6'd28:

begin

q_r <= M_2;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd29;

end

end

6'd29:

begin

q_r <= M_6;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd30;

end

end

6'd30:

begin

q_r <= M_5;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd31;

end

6'd31:

begin

q_r <= M_3;

if(cnt2 < 4'd2)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd32;

end

end

6'd32:

begin

q_r <= M_5;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd33;

end

end

6'd33:

begin

q_r <= M_6;

if(cnt2 < 4'd7)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd34;

end

end

6'd34:

begin

q_r <= H_1;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd35;

end

end

6'd35:

begin

q_r <= M_5;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd36;

end

end

begin

q_r <= M_3;

if(cnt2 < 4'd2)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd37;

end

end

6'd37:

begin

q_r <= M_1;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd38;

end

end

6'd38:

begin

q_r <= M_2;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd39;

end

end

6'd39:

begin

q_r <= M_1;

n <= 6'd40;

end

6'd40:

begin

q_r <= M_2;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd41;

end

end

6'd41:

begin

q_r <= M_3;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd42;

end

6'd42:

begin

q_r <= M_1;

if(cnt2 < 4'd3)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd43;

end

end

6'd43:

begin

q_r <= L_6;

if(cnt2 < 4'd2)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd44;

end

end

6'd44:

begin

q_r <= M_5;

if(cnt2 < 4'd1)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd45;

end

end

6'd45:

begin

q_r <= M_1;

if(cnt2 < 4'd7)

cnt2 <= cnt2 + 4'd1;

else

begin

cnt2 <= 4'd0;

n <= 6'd0;

end

end

default:n <= 6'd0;

endcase

end

end

endmodule

模块SPEAK见图1-2。该模块的功能是根据TONE送来的初值倒计时,每次计到0时就使信号Q反转,由于初值不同,从而产生不同的音高。

//**************************************************************//

// 音调产生模块 //

// 时钟:4MHz //

//**************************************************************//

//根据A的值倒计时,使信号Q反转,产生不同的音高。module speak(clock,a,q);

//I/O口声明

input clock;

input[13:0] a;

output q;

//I/O寄存器

reg q_r;

//内部寄存器

reg[13:0] count; //倒计数器

reg b; //标志位

assign q = q_r;

always @(posedge clock)

begin

if(b == 1'b0)

begin

count <= a;

b <= 1'b1;

end

else

begin

if(count == 14'd0)

begin

b <= 1'b0;

q_r <= ~q_r;

end

else

begin

count <= count - 14'd1;

end

end

end

endmodule

乐曲硬件演奏电路设计

湖南人文科技学院 课程设计报告 课程名称:VHDL语言与EDA课程设计 设计题目:乐曲硬件演奏电路设计 系别:通信与控制工程系 专业:电子信息工程 班级:08电信二班 学生姓名: 王世伟朱彩虹 学号:08409249 08409231 起止日期:2011年06月13日~20年06月26日 指导教师:姚毅成继中

教研室主任:侯海良

摘要 乐曲演奏广泛用于自动答录装置、手机铃声、集团电话、及智能仪器仪表设备。实现方法有许多种,随着FPGA集成度的提高,价格下降,EDA设计工具更新换代,功能日益普及与流行,使这种方案的应用越来越多。如今的数字逻辑设计者面临日益缩短的上市时间的压力,不得不进行上万门的设计,同时设计者不允许以牺牲硅的效率达到保持结构的独特性。使用现今的EDA软件工具来应付这些问题,并不是一件简单的事情。FPGA预装了很多已构造好的参数化库单元LPM 器件。通过引入支持LPM的EDA软件工具,设计者可以设计出结构独立而且硅片的使用效率非常高的产品。 本课设在EDA开发平台上利用VHDL语言设计数控分频器电路,利用数控分频的原理设计乐曲硬件演奏电路,并定制LPM-ROM存储音乐数据,以“两只老虎”乐曲为例,将音乐数据存储到LPM-ROM,就达到了以纯硬件的手段来实现乐曲的演奏效果。只要修改LPM-ROM所存储的音乐数据,将其换成其他乐曲的音乐数据,再重新定制LPM-ROM,连接到程序中就可以实现其它乐曲的演奏。 关键词:FPGA;EDA;VHDL;音乐

目录 设计要求 (1) 1、方案论证与对比 (1) 1.1方案一 (1) 1.2方案二 (1) 1.3综合对比 (1) 2 乐曲演奏电路原理 (2) 2.1 音乐演奏电路原理 (2) 2.2 音符频率的获得 (2) 2.3 乐曲节奏的控制 (3) 2.4 乐谱发生器 (3) 2.5 乐曲演奏电路原理框图 (3) 3音乐硬件演奏电路的设计实现 (4) 3.1 地址发生器模块 (4) 3.1.1 地址发生器的VHDL设计 (4) 3.2 分频预置数模块 (6) 3.2.1 分频预置数模块的VHDL设计 (6) 3.3 数控分频模块 (8) 3.3.1 数控分频模块的VHDL设计 (8) 3.4 music模块 (10) 3.4.1 音符数据文件 (10) 3.5.2 LPM-ROM定制 (12) 3.6 顶层文件 (14) 4 时序仿真及下载调试过程 (16) 4.1 时序仿真图 (16) 4.2 引脚锁定以及下载 (17) 4.3调试过程及结果 (17) 5扩大乐曲硬件演奏电路的通用性 (18) 5.1 完善分频预置数模块的功能 (18) 设计总结与心得体会 (21) 参考文献 (22)

乐曲自动演奏器

乐曲自动演奏器 一、功能介绍 使用FPGA设计一个乐曲自动演奏控制器,将源程序下载至FPGA 器件中,实现乐曲自动演奏。(本设计的乐曲是《友谊天长地久》的部分音乐) 乐曲演奏的原理是:由于组成乐曲的每个音符的频率值(音调)及其持续时间(音长)是乐曲演奏的2个基本数据,因此需要控制输出到扬声器的激励信号的频率高低和该频率信号持续的时间。频率的高低决定了音调的高低,而乐曲的简谱与各音名的频率之间也有固定的对应关系。所有不同频率的信号都是从同一基准频率分频而得来的,由于音阶频率多为非整数,而分频系数又不能为小数,故必须将计算的到的分频数进行四舍五入取整,基准频率和分频系数应综合考虑加以选择,从而保证音乐不会走调。如在4MHz时钟下,中音1(对应的频率值为523.3Hz)的分频系数应该为:4000000/(2*523.3)=0xd3821,这样只需对系统时钟进行3821次分频即可得到所要的中音1。至于其他音符,同样可求出对应的分频系数,这样利用程序可以很轻松地得到对应的乐声。此外,在程序中设置了一个状态机,每250ms改变一个状态(即一个节拍),组成乐曲的每

个音符的频率值(音调)相对应于状态机的每一个状态。只要让状态机的状态按顺序转换,就可以自动播放音乐了。《友谊天长地久》乐谱见下表(注:N一拍;N两拍;N﹒四拍;N﹒八拍;N为乐谱。由于芯片存储容量太小,源程序只加入乐谱的一部分音符) 《友谊天长地久》乐谱 0 5. | 1. 1 1 3 | 2. 1 2 3 | 1. 1 3 5 | 6. 6 | 5. 3 3 1 | 2. 1 2 3 | 1. 6. 6 5 .. | 1. 6 | 5. 3 3 1 | 2. 1 2 6 | 5 . 3 3 5 | 6. 1 | 5. 3 3 1 | 2. 1 2 3 | 1. 6. 6 5 ..| 1. 0 ? 简谱中的音名与频率的关系

乐器演奏电路设计-vhdl

重庆交通大学计算机与信息学院设计性实验报告 班级:通信工程专业 07 级 2 班 姓名(学号): 实验项目名称:乐器演奏电路设计 实验项目性质:设计性 实验所属课程: VHDL 实验室(中心): 指导教师:徐雯娟 实验完成时间: 2009 年 12 月 13 日

一、实验目的 1,了解普通扬声器的工作原理; 2,了解QuartusII4.1中提供了宏功能元件库mega_lpm。 3,使用LPM_ROM参数化存储模块。 二、实验内容及要求 要求能够演奏出《友谊地久天长》的曲调或可另选一段较完整的曲调。 (扩展要求:能够从数码管上显示出当前曲调的简谱和频率) 三、实验原理 1,音符的频率: 可以由上图中的U3获得,这是一个数控分频器。由其clk 端输入一具有较高频率(这里是12MHz)的信号,通过U3分频后由SPKOUT输出,U3对clk 输入信号的分频比由11位预置数Tone[10..0]决定。SPKOUT的输出频率将决定每一音符的音调,这样,分频计数器的预置值Tone[10..0]与SPKOUT 的输出频率,就有了对应关系。

2,音符的持续时间: 须根据乐曲的速度及每个音符的节拍数来确定,图中模块U2的功能首先是为U3提供决定所发音符的分频预置数,而此数在U3输入口停留的时间即为此音符的节拍值。模块U2是乐曲简谱码对应的分频预置数查表电路,其中设置了乐曲全部音符所对应的分频预置数(一共8个),每一音符的停留时间由音乐节拍和音调发生器模块U1的clk的输入频率决定(如为4Hz),这8个值的输出由对应于U2的3位输入值Index[2..0]确定。3,乐谱的存储: 在U1中设置了一个7位二进制计数器(计数最大值为65),作为音符数据ROM 的地址发生器。这个计数器的计数频率若选为4Hz,即每一计数值的停留时间为0.25秒,恰为当全音符设为1秒时,四四拍的4分音符持续时间。随着U1中的计数器按4Hz的时钟速率作加法计数时,即随地址值递增时,音符数据ROM 中的音符数据将从ROM中通过ToneIndex[2..0]端口输向U2模块,乐曲就开始连续自然地演奏起来了。 四、实验仪器、材料 1,2MHZ和4HZ的信号源 2,ACEX1K EP1K30TC144—1芯片 3,扬声器 五、方案设计(设计性实验需要,综合性实验无该项) 1,音符的产生: 音符的产生是利用数控分频器模块SPKEAR对输入的时钟信号CLK400KHZ进行分频,预置数为TONE[10..0],然后分频得出频率为CLK/2*(2048- TONE[10..0]),通过控制输入预置数TONE[10..0]来达到不同的输出频率,以达到控制扬声器发出不同的声音。 例如:当设置预置数TONE[10..0]为1538时,输出SPKEAR频率为396,为低音5。 2,频率的分频: 由于实验给定信号源为12MHZ,不满足数控分频器模块SPKEAR对输入时钟信号的要求,遂其进行30分频(PULSE30),产生0.4MHZ的时钟信号。 3,预置数的产生:

乐曲硬件演奏电路设计-verilog

EDA技术及创新实践(设计报告) 题目:乐曲硬件演奏电路设计 姓名:漩涡鸣人 学院:数理与信息工程学院 专业:电子科学与技术 班级:112 学号:1886****20 指导教师:汤大智 2014年6 月

一、设计目的及要求 实验目的: 1、理解音乐演奏的原理及分频器的原理与使用。 2、了解怎样控制音调的高低变化和音长,从而完成乐曲的自动循环演奏。 3、培养自主学习、正确分析和解决问题的能力。 要求:利用分频器设计硬件乐曲演奏电路;能通过数码管显示动态效果;通过一个开关实现两首乐曲的切换;在音乐播放的同时,会有led流水灯的闪烁。 二、设计原理 乐曲演奏的原理是这样的:组成乐曲的每个音符的频率值(音调)及其持续的时间(音长)是乐曲能连续演奏所需的两个基本数据,因此只要控制输出到扬声器的激励信号频率的高低和持续的时间,就可以使扬声器发出连续的乐曲声。 图1、顶层模块图 其中,乐谱产生电路用来控制音乐的音调和音长。控制音调通过设置计数器的预置数来实现,预置不同的数值可以使计数器产生不同频率的信号,从而产生

不同的音调。控制音长是通过控制计数器预置数的停留时间来实现的,预置数停留的时间越长,则该音符演奏的时间越长。每个音符的演奏时间都是0.25s的整数倍,对于节拍较长的音符,如2分音符,在记谱时将该音名连续记录两次即可。 1、音调的控制 频率的高低决定了音调的高低。音乐的十二平均率规定:每两个8度音(如简谱中的中音1与高音1)之间的频率相差一倍。在两个8度音之间,又可分为12个半音,每两个半音的频率比为12√2。另外,音名A(简谱中的低音6)的频率为440Hz,音名B到C之间、E到F之间为半音,其余为全音[4]。由此可以计算出简谱中从低音1至高音1之间每个音名对应的频率,如表2所示: 表2简谱中的音名与频率的关系 所有不同频率的信号都是从同一个基准频率分频得到的。由于音阶频率多为非整数,而分频系数又不能为小数,故必须将计算得到的分频数四舍五入取整。若基准频率过低,则由于分频比太小,四舍五入取整后的误差较大;若基准频率

器乐演奏理论与实践

湖南师范大学硕士研究生入学考试自命题考试大纲 考试科目代码;[ 973 ] 考试科目名称:器乐演奏理论与实践 一、考试形式与试卷结构 1)试卷成绩、技法演唱及考试时间 试卷满分为150分,考试时间为180分钟。 2)答题方式:闭卷、笔试、技法演唱或演奏考试。 3)试卷内容结构及所占分值 音乐分析约占50分 器乐演奏约占100分 4)题型结构 分析论述题:共50分 1曲式图示,25分 2 分析报告,25分 器乐演奏:共100分 二、考试内容与考试要求 1)音乐分析部分 考试目标: 考察学生对于音乐发展逻辑的把握能力。其中包括:音乐陈述结构特点、曲式结构特点、调性布局特点等。在此基础上,能够用简明的曲式图示说明音乐的逻辑运动过程,并用文字就音乐本体的发展特点进行简要说明。 考试内容: 1、陈述结构类型:乐汇、乐句、乐段、乐段的扩展、群结构、自由结构 2、曲式结构类型:单一部曲式、单二部曲式、单三部曲式、复合再现三部曲式、变奏曲 式、回旋曲式、奏鸣曲式、回旋奏鸣曲式等。 2)器乐演奏部分(接收手风琴、扬琴、古筝、二胡方向考生) 请考生们准备四首大型器乐曲目: 三、参考书目: 杨儒怀著:《音乐的分析与创作》,人民音乐出版社2003年。

吴春福编著:《音乐考研复习精要曲式与作品分析》,湖南文艺出版社2007年。 谢福源编著:《音乐分析谱例集》,湖南文艺出版社2014年。 夏雄军著:《手风琴演奏与教学》2009年上海百佳出版社 李聪、葛佳麒主编:《流行手风琴曲集合-缤纷手风琴世界》上海音乐出版社2010.4 张自强、李遇秋,主编,任士荣、杨文涛、闪源昌、杨屹、李锐。《全国手风琴演奏(业余)考级作品集》[第九级、第十级](最新修订本),全国乐器演奏(业余)委员会、手风琴专家委员会编。文化艺术出版社,1998年3月 黄河主编《全国扬琴演奏考级作品集》人民音乐出版社2011年 桂习礼主编《跟名师学扬琴:学扬琴三十课》国际文化出版公司2003年 王中山编著:《全国古筝演奏考级作品集》(第九级,第十级)安徽文艺出版社2008.5 于红梅编著:《二胡音乐会曲集》华乐出版社2005 《全国二胡演奏考级作品集》人民音乐出版社2003 以及相关书目

八位智力抢答器的设计与制作开题报告

八位智力抢答器的设计与制作开题报告 一、开题报告背景和意义 智力竞赛是一种能锻炼人的头脑开发人的IQ的一种大众化游戏,也起到娱乐的作用。现在智力竞赛越来越被多数人喜爱和娱乐,像中央卫视的三星智力快车、金苹果、幸运50等等多档智力竞赛节目都拥有大批的忠实观众。而且国内外各地电视台、工厂、学校等单位也会常常举办类似的智力竞赛活动,然而智力竞赛抢答器是必要设备。 在有些地方举行的各种智力竞赛游戏中我们经常看到有抢答的环节,举办方大多数采用让选手通过举答题板的方法或者是举手的方式判断选手的答题权,这在某种程度上会因为主持人的主观误断造成比赛的不公平性。所以,我们就需要一种具备自动锁存,置位,清零等功能智能抢答器来解决这些问题。 二、开题报告任务的主要内容 1.设计一个智力抢答器,可同时供多名选手参加比赛,对应多个抢答按钮。 2.主持人设置一个控制开关,用来控制系统得清零(显示数码灭)和抢答开始。 3.抢答器具有数据锁存功能,抢答开始后,若有选手抢答,编号立即锁存,LED 显示选手编号。同时扬声器给出音响提示,此外,要封锁输入电路。 4.(扩展功能)定时抢答,主持人设定时间,启动开始后,定时器立即减计时,并用显示器显示。 5.参赛选手在设定的时间内抢答,抢答有效,定时器停止工作,显示选手编号和抢答时刻的时间,并保持到主持人将系统清零为止。 6.如果定时抢答的时间已到,却没有选手抢答,本次抢答无效,并封锁输入电路,报警,禁止超时抢答。 三、已具备条件 熟练protell99se软件的使用,已学过模拟电子技术、数字电子技术和电路基本知识等课程。还有电子元对基本电路的简单设计,器件的选型、安装、焊接与调试。

乐曲硬件演奏电路设计

江西理工大学应用科学学院 SOPC/EDA综合课程设计报告 设计题目:硬件音乐演奏电路 设计者:徐达健 学号:08040108131 班级:测控081 指导老师:王忠锋 完成时间:2011年01月07日 设计报告综合测试总评 格式(10)内容 (40) 图表 (10) 答辩 (20) 平时 (20)

目录 一:设计原理 (3) 二:总体框图 (5) 三:选择器件 (7) 四:功能模块: (8) 1:NoteTabs模块(程序仿真图) (8) 2:ToneTaba模块(程序仿真图) (11) 3:Speakera模块(程序仿真图) (12) 五:总体设计电路图 (16) 1.顶层设计的电路原理图(Songer模块) (16) 2.Songer模块的程序 (16) 3.Songer顶层文件的仿真图形 (17) 4、锁定引脚 (17) 5、下载验证 (18) 六:结束语 (19)

七:心得体会 (20) 八:参考文献 (21) 一、设计原理 1.音乐演奏电路原理 这种频率的振荡可以用不同音符的代码所控制,从而分出不同频率的振荡,它采用编程方式将各种音符的代码预先存的计算机的内存中,利用软件和一定硬件电路配合将存放的乐曲代码有节地进行演奏,产生电子音乐。乐曲中每个音符的发生频率及其持续时间是乐曲能够连续演奏的两个关键因素。 图1.1 音乐演奏电路原理图

2.音符频率的获得 多本文中选取750KHz的基准频率。由于现有的高频时钟脉冲信号的频率为12MHz,故需先对其进行16分频,才能获得750KHz的基准频率。对基准频率分频后的输出信号是一些脉宽极窄的尖脉冲信号(占空比=1/分频系数)。为提高输出信号的驱动能力,以使扬声器有足够的功率发音,需要再通过一个分频器将原来的分频器的输出脉冲均衡为对称方波(占空比=1/2),但这时的频率将是原来的1/2。表1中各音符的分频系数就是从750KHz 的基准频率二分频得到的375KHz频率基础上计算得到的。 由于最大分频系数是1274,故分频器采用11位二进制计数器能满足要求,乐曲中的休止符,只要将分频系数设为0,即初始值=2048-1=2047,此时扬声器不会发声。3.乐曲节奏的控制 本文中的梁祝乐曲,最小的节拍为1/4拍,若将1拍的时间定为1秒,则只需要提供一个4Hz的时钟频率即可产生1/4拍的时长(0.25秒),对于其它占用时间较长的节拍(必为1/4拍的整数倍)则只需要将该音符连续输出相应的次数即可。 计数时钟信号作为输出音符快慢的控制信号,时钟快时输出节拍速度就快,演奏的速度也就快,时钟慢时输出节拍的速度就慢,演奏的速度自然降低。 4.乐谱发生器 本文将乐谱中的音符数据存储在NoteTABS中,如“梁祝”乐曲中的第一个音符为“3”,此音在逻辑中停留了4个时钟节拍,即1秒的时间,相应地,音符“3”就要在NoteTABS 中连续的四个地址上都存储。当一个4Hz的时钟来时,相应地存入NoteTABS中一个音符数据。

乐曲演奏电路

成绩 指导教师: 日期: 《EDA技术与VHDL语言设计》 课程设计 题目: EDA技术及其应用 ——乐曲演奏电路 姓名:陈 院系:电子信息工程学系 专业:电子信息工程 班级:电信092 学号: 910706220 指导教师:余尤好 2011年12 月

EDA 技术及其应用 ——乐曲演奏电路 陈 (电子信息工程学系 指导教师:余尤好) 摘要:利用EDA 技术对乐曲演奏电路进行仿真,设计者在EDA 软件平台上,用硬件描述语言HDL 完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作.EDA 是电子设计自动化(Electronic Design Automation )的缩写,在20世纪90年代初从计算机辅助设计(CAD )、计算机辅助制造(CAM )、计算机辅助测试(CAT )和计算机辅助工程(CAE )的概念发展而来的。 关键词:EDA 技术 仿真 乐曲演奏 一、概述 1.1设计目的及要求 本实验课程的目的,旨在通过上机实验,使学生加深理解EDA 技术的基本方法,帮助和培养学生建立利用原理图和硬件描述语言进行电路设计的基本方法和利用EDA 工具软件(MAX+plus Ⅱ或Quartus7.2)设计简单数字电子系统的能力,为以后从事有关数字电子系统方面的设计和研究开发工作打下基础。 为使演奏能循环进行,需另外设置一个时长计数器,当乐曲演奏完成时,保证能自动从头开始演奏。 1.2实验前预习 每次实验前,学生须仔细阅读本实验指导书的相关内容,明确实验目的和实验内容;明确实验原理与步骤;复习与实验内容有关的理论知识;预习仪器设备的使用方法、操作规程及注意事项。 1.3设计环境 计算机 MAX+plusII10.2 二、设计过程及原理 2.1乐曲演奏的原理 组成乐曲的每个音符的频率值(音调)及其持续的时间(音长)是乐曲能连续演奏所需的两个基本数据,因此只要控制输出到扬声器的激励信号的频率高低和持续时间,就可以使扬声器发出连续的乐曲声。首先来看怎样控制音调的高低变化。如下图1是乐曲演奏电路的原理框图,其中,乐谱产生的电路用来控制音乐的音调和音长。控制音调通过设置计数器的预置数来实现,预置不同的数值就可以使计数器产生不同频率的信号,从而产生不同的音调。控制音长是通过控制计数器预置数的停留时间来实现的,预置数停留的时间越长,则该音符演奏的时间越长。每个音符的演奏时间都是0.25s 的整数倍,对于节拍长的音符,如2分音符,在记谱时将该音名连续记录两次即可。 6MHz 扬声器 4Hz 数码管 图1 乐曲演奏电路原理框图 反馈预置计数器 2分频器 曲谱产生 音符显示

音乐演奏器设计

山东工商学院 电子设计大赛 作品设计报告 题目:音乐演奏器设计 队名: XXXXXX 成员: XXXXXXXXXXXXXXXXXXXX 提交时间: 2016.7.1

目录 一、引言....................................................................................................................................... 3 二、方案比较以及选择................................................................................................................. 3 2.1 控制模块选择方案......................................................................................................... 3 2.2 按键选择方案.................................................................................................................. 4 三、硬件设计及说明..................................................................................................................... 4 3.1系统组成及总体框图...................................................................................................... 4 3.2元件简介........................................................................................................................... 5 3.3 各功能模块原理图.......................................................................................................... 6 四、软件设计................................................................................................................................. 8 4.1 音乐相关知识.................................................................................................................. 8 4.2用单片机实现音乐的节拍............................................................................................... 9 4.3用单片机产生音频脉冲................................................................................................... 9 五、系统调试................................................................................................................................. 9 5.1硬件调试........................................................................................................................... 9 5.2 软件调试...................................................................................................................... 10 六、总结..................................................................................................................................... 10 七、参考文献............................................................................................................................. 10附录1:元器件清单...................................................................................... 错误!未定义书签。附录2:电路原理图.................................................................................................................. 11

电子琴实验报告乐曲硬件演奏电路设计本科论文

武夷学院实验报告 课程名称:逻辑设计与FPGA 项目名称: 乐曲硬件演奏电路设计 ______________ 姓名: 专业:微电子学 班级:14微电子 学号:04实验日期 、 实验预习部分: 1. 实验目的: 学习利用数控分频器设计硬件乐曲演奏电路。 2. 实验原理: 综合利用数控分频器、LPM ROMPLL 等单元电路设计硬件乐曲演奏电路。系统框图如图 1 所示由三个模块组成,分别为 NOTETABSTONETABASPEAKERA NOTETAB 模块(把教材图9-4中的CNT138T 和MUSIC 模块合在一起即为此模块)类似于弹 琴人的手指;TONETAB 模块类似于琴键;SPEAKER 类似于琴弦或音调发生器。 音符的频率由SPEAKER 模块(与教材图9-4中的SPKEF 模块对应)获得,这是一个数控分 频器。由其CLK 端输入一具有较高频率(12MHZ 的信号,通过SPEAKER 分频后由SPKOU 输出。 SPEAKER 对CLK 输入信号的分频比由11位预置数TONE[10..0]决定。SPKOU 的输出频率将决定 每一音符的音调,这样,分频计数器的预置值 TONE[10..0]与SPKOU 的输出频率就有了对应关 系。例如在TONETAB 模块(与教材图9-4中的F_COD 模块对应)中若取 TONE[10..0] = 1036, 图1硬件乐曲演奏电路结构框图 i.;E-Z

将发出音符“ 3”音的信号频率。

实验预习成绩(百分制)____________________ 实验指导教师签字:_________________________

简易抢答器的电路设计

简易抢答器的电路设计 学院名称公安技术学院 专业刑事科学技术、安全防范工程班级12级刑科、13级安防、刑科指导老师寇为刚 学生姓名脱海涛彭俊杰刘吉宏陈砚君 甘肃政法学院 2013年12月8日

摘要 本设计主要介绍用数电知识设计八路抢答器。优先编码电路、锁存器、译码电路将参赛队的输入信号在显示器上输出,并与主持人开关相连接,即构成了抢答器的主体电路。经过布线、接线、调试等工作后数字抢答器成形。借助较少的外围元件完成抢答的整个过程,设计制作了八路抢答器,设计编程简单,工作稳定可靠。可供8人或8个代表队抢答,并用7段数码管显示首先抢答者的组别号码,有人抢答后自动闭锁其他各路输入,禁止其他人抢答,使其他组的开关失去作用,而显示最先按下抢答键的组别号。只有当主持人按下复位按键才能再次抢答。 关键字:抢答器数码管信号电路 Abstract The design introduced by the number of electrical knowledge eight responder design. Input signal priority coding circuit, latch, decoder circuit will be the team's output on a display, and connected with the host switch, which constitute the main circuit responder. After wiring, wiring, commissioning work forming digital answering device. The whole process with fewer peripheral components to complete the answer, designed and produced eight way responder, programming is simple, stable and reliable work. For 8 people or 8 team competition, with 7 digital tube display first responder group number, some people answer automatic blocking other each input, no other answer, switch to other groups lose their effect, and shows the first press the answer key constituencies. Only when the host press the reset button again to answer. Keyword:Responder Digital tube Signal Circuit

乐器硬件演奏电路

EDA技术课程大作业 设计题目:乐器硬件演奏电路 院系:电子信息与电气工程学院 学生姓名: 学号:200902070018 专业班级: 2010 年12 月 4 日

乐曲硬件演奏电路 1. 设计背景和设计方案 1.1设计背景 目前,各领域的激烈竞争迫使人们不得不对办事效率格外重视,同时,这也是方便、高效的社会发展趋势之必要。随着科技发展及电子方面的成熟。数控分频器它成为这方面当之无愧的选择。本设计正是关于分频器在乐器硬件演奏电路系统的应用。与传统的纯硬件相比,简单有效,此设计可以适应多家可编程逻辑器件,便于组织大规模的系统设计;便于设计的复用继承和升级,具有广阔的应用前景。 1.2设计方案 该系统主要由NOTETABS,TONETABA,SPEAKERA三个模块组成,与利用微处理器CPU,MCU来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂的多,仅凭借传统的数字逻辑技术是难以实现的,因此,这里我们借助强大的EDA工具和VHDL硬件描述语言来完成。 模块SPEAKERA是数控分频器计数输出模块为一个11位的可预置数计数器。通过NOTETABS得到预置数,并对这些进行计数。由SPEAKERA的CLK端输入一具有较高的频率的信号,通过SPEAKERA分频后由SPKOUT输出,模块TONETABA的功能首先是为SPEAKERA提供决定所发音符的分频预置数,而此数在SPEAKERA输入口停留的时间即为此音符的节拍值。每一个音符的停留时间又由音乐节拍和音调发生器模块NOTETABS的CLK的输入频率决定,输出由对应于TONETABA的4位输入值INDEX[3..0]确定。输向TONETABA中INDEX[3..0]的输出值与持续的时间由模块NOTETABS决定。在NOTETABS中设置了一个8为二进制计数器作为音符数据ROM的地址发生器。这个计数器的计数频率选为4HZ,随着NOTETABS中的计数器按4HZ的时钟速率做加法计数时,即随地址值递增时,音符数据ROM中的音符数据将从ROM中通过TONEINDEX[3..0]端口输向TONETABA 模块,乐曲就开始连续自然地演奏起来了。 2. 方案实施 2.1 实现原理及算法的描述 首先,编写数控分频器计数输出模块SPEAKERA,其输入为clk, Tone ,输出为Spks,

EDA乐曲硬件演奏电路设计 课程设计

摘要 乐曲演奏广泛用于自动答录装置、手机铃声、集团电话、及智能仪器仪表设备。实现方法有许多种,随着FPGA集成度的提高,价格下降,EDA设计工具更新换代,功能日益普及与流行,使这种方案的应用越来越多。如今的数字逻辑设计者面临日益缩短的上市时间的压力,不得不进行上万门的设计,同时设计者不允许以牺牲硅的效率达到保持结构的独特性。使用现今的EDA软件工具来应付这些问题,并不是一件简单的事情。FPGA预装了很多已构造好的参数化库单元LPM 器件。通过引入支持LPM的EDA软件工具,设计者可以设计出结构独立而且硅片的使用效率非常高的产品。 本课设在EDA开发平台上利用VHDL语言设计数控分频器电路,利用数控分频的原理设计乐曲硬件演奏电路,并定制LPM-ROM存储音乐数据,以“两只老虎”乐曲为例,将音乐数据存储到LPM-ROM,就达到了以纯硬件的手段来实现乐曲的演奏效果。只要修改LPM-ROM所存储的音乐数据,将其换成其他乐曲的音乐数据,再重新定制LPM-ROM,连接到程序中就可以实现其它乐曲的演奏。 关键词:FPGA;EDA;VHDL;音乐

目录 设计要求 (1) 1、方案论证与对比 (1) 1.1方案一 (1) 1.2方案二 (1) 1.3综合对比 (1) 2 乐曲演奏电路原理 (2) 2.1 音乐演奏电路原理 (2) 2.2 音符频率的获得 (2) 2.3 乐曲节奏的控制 (3) 2.4 乐谱发生器 (3) 2.5 乐曲演奏电路原理框图 (3) 3音乐硬件演奏电路的设计实现 (4) 3.1 地址发生器模块 (4) 3.1.1 地址发生器的VHDL设计 (4) 3.2 分频预置数模块 (6) 3.2.1 分频预置数模块的VHDL设计 (6) 3.3 数控分频模块 (8) 3.3.1 数控分频模块的VHDL设计 (8) 3.4 music模块 (10) 3.4.1 音符数据文件 (10) 3.5.2 LPM-ROM定制 (12) 3.6 顶层文件 (14) 4 时序仿真及下载调试过程 (16) 4.1 时序仿真图 (16) 4.2 引脚锁定以及下载 (17) 4.3调试过程及结果 (17) 5扩大乐曲硬件演奏电路的通用性 (18) 5.1 完善分频预置数模块的功能 (18) 设计总结与心得体会 (21) 参考文献 (22)

简易抢答器制作(完成版)

电子技术综合训练 设计报告 题目:简易抢答器制作 姓名: 学号: 班级: 同组成员: 指导教师: 日期:

摘要 本文讲述的简易抢答器的主要是由抢答电路、计时电路、报警电路、主持人控制电路组成。当主持人按下主控制开关,抢答开始,计时也开始,如果有人抢答,计时停止,主持人打开主控制开关,抢搭清零,当开关再次闭合时,新一轮抢答开始;如果三十秒后无人抢答,则报警电路动作,开始报警,一秒后自动解除,主持人打开开关,当开关再次闭合时,新一轮抢答开始。 关键词:抢答器,计时电路

目录 摘要 (2) 1、设计任务和要求 (4) 1.1设计任务 (4) 1.2设计要求 (4) 2、系统设计 (5) 2.1系统要求 (5) 2.2方案设计 (5) 2.3系统工作原理 (5) 3、单元电路设计 (6) 3.1抢答电路 (6) 3.11电路结构 (6) 3.12仿真图 (6) 3.13元器件及参数 (6) 3.2计数电路 (10) 3.21电路结构 (10) 3.22仿真图 (11) 3.23元器件及其参数 (11) 3.3报警电路 (15) 3.31电路结构 (15) 3.32仿真电路 (15) 3.33元器件及其参数 (16) 3.4直流稳压电源的设计 (16) 4、系统仿真 (18) 5、电路安装、调试、与测试 (20) 5.1电路安装 (20) 5.2电路调试 (20) 5.3测试结果及分析 (20) 结论 (21) 参考文献 (22) 总结、体会和建议 (23) 附录 (23) 元器件清单 (23)

1、设计任务和要求 1.1设计任务 设计并制作一个简易数字抢答器 1.2设计要求 (1)抢答组数分为八组,序号分别为S0,S1,S2,S3,S4,S5,S6,S7,优先抢答者按动本组按钮,组号立即在LED显示器上显示,同时封锁其他组的按键信号。(2)系统设置外部清除键,按动清除,LED显示器自动清零灭灯。 (3)数字抢答器定时为30s,启动开始键后,要求30秒定时器开始工作,发光二极管点亮。 (4)抢答者在30秒内进行抢答,抢答有效,如果30秒定时到时,无抢答者,则本次抢答无效,系统短暂报警。 (5)电源:220v/50Hz的工频交流电供电;(注:直流电源部分只完成设计部分即可,不需制作,用实验室提供的稳压电源调试,但要求设计的直流电源满足电路要求) (6)按照以上技术要求设计电路,绘制电路图,对设计的电路用Multisim或CAD/PspiceAD9.2进行仿真,用万用版焊接原件,制作电路,完成调试、测试、撰写设计报告。

乐曲硬件演奏电路设计_verilog

EDA技术及创新实践(设计报告) 题目: 乐曲硬件演奏电路设计 姓名: 漩涡鸣人 学院: 数理与信息工程学院 专业: 电子科学与技术 班级: 112 学号: 1886****20 指导教师: 汤大智 2014年6 月

一、设计目的及要求 实验目的: 1、理解音乐演奏的原理及分频器的原理与使用。 2、了解怎样控制音调的高低变化和音长,从而完成乐曲的自动循环演奏。 3、培养自主学习、正确分析和解决问题的能力。 要求:利用分频器设计硬件乐曲演奏电路;能通过数码管显示动态效果;通过一个开关实现两首乐曲的切换;在音乐播放的同时,会有led流水灯的闪烁。 二、设计原理 乐曲演奏的原理是这样的:组成乐曲的每个音符的频率值(音调)及其持续的时间(音长)是乐曲能连续演奏所需的两个基本数据,因此只要控制输出到扬声器的激励信号频率的高低和持续的时间,就可以使扬声器发出连续的乐曲声。 图1、顶层模块图 其中,乐谱产生电路用来控制音乐的音调和音长。控制音调通过设置计数器的预置数来实现,预置不同的数值可以使计数器产生不同频率的信号,从而产生不同的音调。控制音长是通过控制计数器预置数的停留时间来实现的,预置数停留的时间越长,则该音符演奏的时间越长。每个音符的演奏时间都是0.25s的整数倍,对于节拍较长的音符,如2分音符,在记谱时将该音名连续记录两次即可。 1、音调的控制 频率的高低决定了音调的高低。音乐的十二平均率规定:每两个8度音(如简谱中的中音1与高音1)之间的频率相差一倍。在两个8度音之间,又可分为12个半音,每两个半音的频率比为12√2。另外,音名A(简谱中的低音6)的频率为440Hz,音名B到C之间、E到F之间为半音,其余为全音[4]。由此可以计

EDA_课程设计_乐曲演奏器

EDA课程设计题目:乐曲硬件演奏电路的VHDL设计 专业:通信工程 班级:通信082 姓名:谢振峰 学号:0810920213

一、 设计题目: 乐曲硬件演奏电路的VHDL 设计 二、 设计目标: 1)能够播放“梁祝”乐曲。 2)能够通过LED 显示音阶。 3)具有“播放/停止”功能,并在此基础上实现“按键演奏”的电子琴功能。 三、 设计原理: 1. 音乐基础知识 一段简单乐谱由音调和节拍组成,音调表示一个音符唱多高的频率,节拍表示一个音符唱多长的时间。音符的节拍我们可以举例来说明。 在一张乐谱中,我们经常会看到这样的表达式,如1=C 4 4 、1=G 43 …… 等等。以43 为例加以说明,它表示乐谱中以四分音符为节拍,每一小结有三拍。比如: 图1 其中1 、2 为一拍,3、4、5为一拍,6为一拍共三拍。1 、2的时长为四分音符的一半,即为八分音符长,3、4的时长为八分音符的一半,即为十六分音符长,5的时长为四分音符的一半,

即为八分音符长,6的时长为四分音符长。那么一拍到底该唱多长呢?一般说来,如果乐曲没有特殊说明,一拍的时长大约为400—500ms 。我们以一拍的时长为400ms为例,则当以四分音符为节拍时,四分音符的时长就为400ms,八分音符的时长就为200ms,十六分音符的时长就为100ms。 2.原理图框图: 图2.框图 3.原理图说明 音乐播放原理说明 音符的频率由数控分频器模块Speakera产生。ToneTaba模块从NoteTabs模块中输入的音符数据,将对应的分频预置数据传送给Speakera模块,并将音符数据送到LED模块显示音阶。 NoteTabs模块中包含有一个音符数据ROM,里面存有歌曲“梁祝”的全部音调,在此模块中设置了一个8位二进制计数器,作为音符数据ROM的地址发生器。这个计数器的计数频率为4Hz,即每一个数值的停留时间为0.25秒。例如:“梁祝” 乐曲的第一个音符为“3”,此音在逻辑中停留了4个时钟节拍,即1秒钟时间,所对应的“3”音符分频预置数为1036,在

基于74LS175芯片的四人抢答器设计

成绩 电子科学与技术系 学年论文 中文题目:基于74LS175芯片的四人抢答器设计 英文题目: Based on the 74LS175 chip of chip of the design of vies to answer first four people 姓名:支晓东 学号:1207010331 专业名称:电子科学与技术 指导教师:梅金硕 2015年6月12日

基于74LS175芯片四人抢答器的设计作者:支晓东哈尔滨理工大学电子科学与技术系 [内容摘要]:随着电子技术的发展,它在各个领域的应用也越来越广泛。人们对它的认识也逐步加深。人们也利用了电子技术以及相关的知识解决了一些实际问题。如:智能抢答器的设计与制作。抢答器是竞赛问题中一种常用的必备装置,从原理上讲,它是一种典型的数字电路。触发器是数字电路中的基本逻辑记忆单元,具有两个稳定状态用以表示逻辑状态“l”和“0”。在电路中它具有记忆信号的功能,是构成各种时序电路的最基本逻辑单元.本文通过对抢答器电路设计的详细分析,以加深对触发器的功能以及其应用的认识和理解。数字抢答器由主体电路与扩展电路组成。触发器电路将参赛队的输入信号在显示器上输出;主持人按开始按钮示意开始,以上两部分组成主体电路。通过两个与门电路实现屏蔽功能,构成扩展电路。经过布线、焊接、调试等工作后数字抢答器成形。 供四人用的竞赛抢答器装置线路,用以判断抢答优先权。它有三部分构成:1个D触发器74LS175,它具有置0端,置1端和CP端;1个4输入与门,1个二输入与门;四个轻触开关,它们组成抢答电路中的CP时钟脉冲源,抢答开始时,由主持人清除信号,按下复位开关S,74LS175的输出Q 1非~Q 4非全为1,所有发光二极管LED均熄灭,当主持人宣布“抢答开始”后,首先作出判断的参赛者立即按下开关,对应的发光二极管点亮,同时,通过与门送出信号锁住其余三个抢答者的电路,不再接受其它信号,直到主持人再次清除信号为止. [关键词]:数字电路设计;触发器;优先抢答

- EDA实验报告5_乐曲硬件演奏电路设计

- EDA乐曲硬件演奏电路设计

- 音乐硬件演奏器

- 乐曲硬件演奏电路设计-verilog

- 实验九 硬件乐曲自动演奏电路设计

- 基于Verilog_HDL的乐曲演奏电路设计

- 乐曲硬件演奏电路的VHDL设计报告

- EDA设计课题论文硬件演奏电路

- EDA乐曲硬件演奏电路设计课程设计报告书

- 基于单片机的音乐演奏电路的设计与制作

- 音乐演奏电路设计

- 乐曲硬件演奏电路设计

- 乐曲硬件演奏电路设计

- 乐曲硬件演奏电路设计_verilog

- 基于FPGA的音乐硬件演奏电路

- EDA乐曲播放电路课程设计报告

- VGA图片(动态)显示与乐曲硬件演奏电路设计

- EDA乐曲硬件演奏电路设计 课程设计

- 梁祝乐曲_乐曲硬件演奏电路的VHDL设计_eda课程设计

- FPGA硬件电子琴电路设计实验报告