AMS1117引脚图

AMS1117(3.3V、5V)

封装:

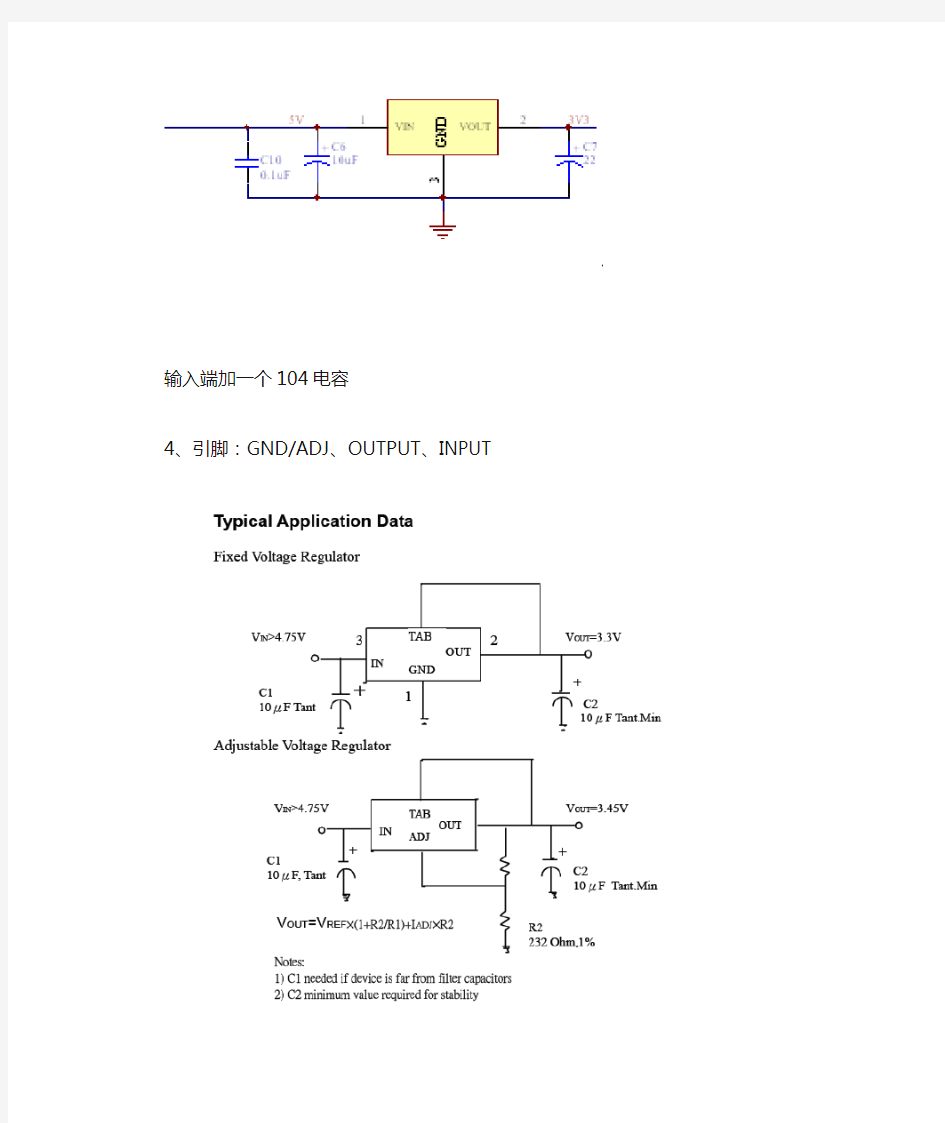

常见应用连接:

1、输入旁路电容Input Bypass Capacitor:A 10uF tantalum on the input is

a suitable input bypassing for almost all applications.建议使用输入旁路电容,10uF的钽电容适用于几乎所有的应用。

2、输出电容Output Capacitor:如果实用钽电容,LM1117要求输出电容的最小值为10uF。

3、

输入端加一个104电容

4、引脚:GND/ADJ、OUTPUT、INPUT

74LS373详细资料精心整理

74LS373 引脚图、内部结构、参数、典型应用电路 【功能简介】 74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。本文将介绍74LS373的工作原理,内容涵盖引脚图、内部结构、主要参数以及在单片机扩展系统中的典型应用电路。 【内部逻辑结构图】 74LS373地址锁存器的内部逻辑结构如图一所示。 图1

【74LS373的真值表(功能表)】 G—与8031/8051的ALE相连,控制八个D型锁存器的导通与截止:高电平时,八个D型锁存器正常运行(导通),即锁存器的输出端 与输入端D的反相信号始终同步;低电平时锁存器截止,D锁存器输出 端的状态保持不变。 OE(Output Enable = Output Control)—使能端,接地时锁存 【74LS373引脚排列图】

【74LS373电气参数】 拖动图片放大! 74ls373推荐工作条件 【74LS373在单片机扩展系统中的典型应用电路】 当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端G为高电平时,输出Q0-Q7的状态与输入端D1-D7状态相同;当G发生负的跳变时,输入端D0-D7 数据锁入Q0-Q7。51单片机的ALE信号可以直接与74LS373的G 连接。在MCS-51单片机系统中,其连接方法如下图所示。其中输入端1D-8D接

至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允 许信号ALE。输出允许端OE接地,表示三态输出门一直导通,可以送出地址信 号。 1D-8D为8个输入端。 1Q-8Q为8个输出端。 【说明】基础比较好的同学请直接忽略。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

74Ls192

实验四触发器及其功能转换 一、实验目的 1、掌握基本RS、JK、D和T触发器的逻辑功能 2、掌握集成触发器的逻辑功能及使用方法 3、熟悉触发器之间相互转换的方法 二、实验原理 触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。 1、基本RS触发器 图4-1为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直接触发的触发器。基本RS触发器具有置“0”、置“1”和“保持”三种功能。通常称S为置“1”端,因为S=0(R=1)时触发器被置“1”;R为置“0”端,因为R=0(S=1)时触发器被置“0”,当S=R=1时状态保持;S=R=0时,触发器状态不定,应避免此种情况发生,表9-1为基本RS触发器的功能表。 基本RS触发器。也可以用两个“或非门”组成,此时为高电平触发有效。

2、JK触发器 在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。引脚功能及逻辑符号如图4-2所示。 JK触发器的状态方程为 Q n+1=J Q n+K Q n J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。Q与Q为两个互补输出端。通常把 Q=0、Q=1的状态定为触发器“0”状态;而把Q=1,Q=0定为“1”状态。 图4-2 74LS112双JK触发器引脚排列及逻辑符号 下降沿触发JK触发器的功能如表4-2 表4-2

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.wendangku.net/doc/a38410114.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

74系列芯片引脚图

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

74ls373引脚图管脚功能表

74ls373引脚图管脚功能表 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片, (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。74ls373与单片机接口:

1D~8D为8个输入端。1Q~8Q为8个输出端。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开

74系列元件引脚图

反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS24 5 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│

Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 1C 1Y 3C 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│ 3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 2A 2B 2C 2Y GND

74ls系列芯片引脚

74 系列芯片的引脚图 [日期:2008-12-29 ] [来源:net 作者:佚名] [字体:大中小] (投递新闻) 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A6Y5A5Y4A4Y六非门74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A)│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1Y2A2Y3A3Y GND 驱动器: Vcc 6A6Y5A5Y4A4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A)│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1Y2A2Y3A3Y GND Vcc -4C 4A4Y -3C 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

-1C 1A1Y -2C 2A2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A4Y3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 1Y2A2B 2Y GND Vcc 4B 4A4Y3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 1Y2A2B 2Y GND Vcc 1C 1Y3C 3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 2A2B 2C 2Y GND Vcc H G Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ )│8输入与非门74LS30 │1 2 3 4 5 6 7│________

常用芯片引脚图[1]

您的数字ID 是:463099 您的密码是:1.8667 附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。 ALE/PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 XTAL1、XTAL2:内部振荡器反相器输 P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS

74LS373应用介绍

74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路. 74ls373工作原理简述: (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。 74ls373内部逻辑结构图

74LS373的真值表(功能表),表中: L——低电平; H——高电平; X——不定态; Q0——建立稳态前Q的电平;

G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。 当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同; 当G为下降沿时,将输入数据锁存。 E G 功能 0 0 直通Qi = Di 0 1 保持(Qi保持不变) 1 X 输出高阻 74ls373引脚(管脚)排列图:

74LS273与74LS373的区别

74LS273与74LS373的区别 发表于2006-12-28 23:47:08 一位网友在中华工控网上问的问题,我看没什么人回答,就整理了一下,给他回答了,并发到我的blog上 74LS273 是带公共时钟复位八D触发器 74LS373 是三态同相八D锁存器 273与373的引脚排列是相同的,唯一的差别是两者1、11脚的功能不同. 对273 (1).1脚是复位CLR,低电平有效,当1脚是低电平时,输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部输出0,即全部复位; (2).当1脚为高电平时,11(CLK)脚是锁存控制端,并且是上升沿触发锁存,当11脚有一个上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的电平状态,并且立即呈现在在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)上. 对373: (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 所以,如果分别用273和373来作为单片机的地址锁存器的话, 对273来说,1(CLR)脚必须接高电平,ALE信号经过反相后接11脚(因为单片机的ALE信号是以下降沿方式出现) 对373来说,1脚接低电平,保证使能,11脚直接接单片机的ALE信号.

74ls147引脚图管脚图和功能真值表

74ls147引脚图管脚图和功能真值表 优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入信号进行编码。常用的集成优先编码器IC有10线-4线、8线-3线两种。10线-4线优先编码器常见的型号为54/74147、54/74LS147,8线-3线优先编码器常见的型号为54/74148、54/74LS148。 下面我们以TTL中规模集成电路74LS147为例介绍8421→BCD码优先编码器的功能。 10线-4线8421 BCD码优先编码器74LS147的真值表见表3.5。74LS147的引脚图如图3.5所示,其中第9脚NC为空。74LS147优先编码器有9个输入端和4个输出端。某个输入端为0,代表输入某一个十进制数。当9个输入端全为1时,代表输入的是十进制数0。4个输出端反映输入十进制数的BCD 码编码输出。 74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421 BCD编码。当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421 BCD编码输出。 表3.5 74LS147的真值表

数字电路CD4511的原理(引脚及功能) CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。可直接驱动LED显示器。 CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,引脚排列如图 2 所示。其中a b c d 为 BCD 码输入,a为最低位。LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时, B1端应加高电平。另外 CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。LE是锁存控制端,高电平时锁存,低电平时传输数据。a~g是 7 段输出,可驱动共阴LED数码管。另外,CD4511显示数“6”时,a段消隐;显示数“9”时,d段消隐,所以显示6、9这两个数时,字形不太美观图3是 CD4511和CD4518配合而成一位计数显示电路,若要多位计数,只需将计数器级联,每级输出接一只 CD4511 和 LED 数码管即可。所谓共阴 LED 数码管是指 7 段 LED 的阴极是连在一起的,在应用中应接地。限流电阻要根据电源电压来选取,电源电压5V时可使用300Ω的限流电阻。 用CD4511实现LED与单片机的并行接口方法如下图:

常用IC引脚图

附录五、常用IC引脚图 1、STC89C51单片机 2、8255并行I/O接口 T2/P1.0 -- 1 40 -- VCC PA3-- 1 40 --PA4 T2EX/P1.1-- 2 39 -- P0.0/AD0 PA2-- 2 39 --PA5 P1.2 -- 3 38 -- P0.1/AD1 PA1-- 3 38 --PA6 P1.3 -- 4 37 -- P0.2/AD2 PA0-- 4 37 --PA7 P1.4 -- 5 36 -- P0.3/AD3 RD -- 5 36 --WR P1.5 -- 6 35 -- P0.4/AD4 CS -- 6 35 --RESET P1.6-- 7 34 -- P0.5/AD5 GND-- 7 34 --D0 P1.7 -- 8 33 -- P0.6/AD6 A1 -- 8 33 --D1 RST -- 9 32 -- P0.7/AD7 A0 -- 9 32 --D2 RXD/P3.0-- 10 31 –EA(EA)PC7 -- 10 31 --D3 TXD/P3.1-- 11 30 --ALE/PROG PC6 -- 11 30 --D4 INT0/P3.2-- 12 29 --PSEN PC5 -- 12 29 --D5 INT1/P3.3-- 13 28 -- P2.7/A15 PC4 -- 13 28 --D6 T0/P3.4 -- 14 27 -- P2.6/A14 PC0 -- 14 27 --D7 T1/P3.5 -- 15 26 -- P2.5/A13 PC1 -- 15 26 --VCC WR/P3.6 -- 16 25 -- P2.4/A12 PC2 -- 16 25 --PB7 RD/P3.7 -- 17 24 -- P2.3/A11 PC -- 17 24 --PB6 XTAL2 -- 18 23 -- P2.2/A10 PB0 -- 18 23 --PB5 XTAL1 -- 19 22 -- P2.1/A9 PB1 -- 19 22 --PB4 VSS -- 20 21 -- P2.0/A8 PB2 -- 20 21 --PB3 注:STC89C51芯片的第31脚在用外接存储器时接低(地)电位,而在使用片内存储器时接高电位。 3、74LS373 八D锁存器 4、LED七段码显示器(共阴极型、单字) CE - 1 20 –VCC g f G a b 1Q - 2 19 –8Q 1D - 3 18 –8D a 2D -- 4 17 –7D f b 2Q -- 5 16 –7Q g 3Q -- 6 15 –6Q e c

常用芯片引脚图

附录三 常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

采用74LS192设计的4、7进制计数器

《电子设计基础》课程报告 设计题目:4/7进制计数器设计 学生班级:通信0902 学生学号:20095972 学生姓名: 指导教师: 时间:2011. 6.24 西南科技大学 信息工程学院

一.设计题目及要求 1、题目:4/7进制计数器设计:采用74LS192(40192)。 2、要求:a、数码管显示状态。 b、用开关切换两种进制。 c、计数脉冲由外部提供。 二.题目分析与方案选择 由题目及其要求分析可知,首先要使用74LS192或40192设计一个4进制计数器和一个7进制计数器,然后通过数码管来显示状态。两种进制间的切换可以通过一个单刀双掷开关来实现。其重点和难点在于设计一个4进制计数器和一个7进制计数器。 通过分析74LS192和40192的特点,发现可以使用清零法来设计一个4进制计数器,而7进制则不能直接通过置数或者清零获得。因此我选择采用置数法将74LS192或40192设计的从0到7的8进制计数器改装为从1到7的计数器,然后再通过一个减法器使从1到7的计数器变为从0到6的7进制计数器。而减法器可以使用集成加法器和四个异或门来实现。 三.主要元器件介绍 在本课程设计中,主要用到了74LS192计数器、7447译码器、74LS00与非门、7408与门、74LS136异或门、74283加法器、七段数码显示器和一个单刀双掷开关等元器件。 一、十进制同步可逆计数器74LS192 功能如下: 1.异步清零。74LS192的输入端异步清零信号CR,高电平有效。仅当CR=1时,计数器输出清零,与其他控制状态无关。 2.异步置数控制。LD非为异步置数控制端,低电平有效。当CR=0,LD 非=0时,D1D2D3D4被置数,不受CP控制。 3.加法计数器,当CR和LD非均无有效输入时,即当CR=0、LD非=1,而减数计数器输入端CPd为高电平,计数脉冲从加法计数端CPu输入时,进行加法计数;当CPd和CPu条件互换时,则进行减法计数。 4.保持。当CR=0、LD非=1(无有效输入),且当CRd=CPu=1时,计数器处于保持状态。 5.进行加计数,并在Q3、Q0均为1、CPu=0时,即在计数状态为1001时,给出一进位信号。进行减计数,当Q3Q2Q1Q0=0000,且CPd=0时,BO非给出一错位信号。这就是十进制的技术规律。 在设计过程中,我主要利用74LS192的计数功能,通过置数法和清零法将其改造为一个4进制计数器和一个7进制计数器。

74ls373引脚图

74ls373引脚图,内部结构,参数,应用电路(74ls373中文资料) 74ls373功能简介: 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路. 74ls373工作原理简述: 74ls373内部逻辑结构图 74LS373的真值表(功能表),表中:

L——低电平; H——高电平; X——不定态; Q0——建立稳态前Q的电平; G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。 当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;

74ls373电气特性 74ls373推荐工作条件 74ls373在单片机系统中的应用电路图: 当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G

端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开。 1D~8D为8个输入端。 1Q~8Q为8个输出端。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出 2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

LS系列芯片引脚图 大全

74系列芯片引脚图资料大全 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8 │六非门(OC高压输出) 74LS06 Y = A ││ │ 1 2 3 4 5 6 7 │ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND

Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND

8255引脚图及引脚功能

8255引脚图及引脚功能 单片机系统中常用的地址锁存器芯片74LS373以及coms的 74hc373。是带三态缓冲输出的8D触发器,其引脚图与结构原理图、电路连接图如下: <74LS373引脚图内部结构原理图电路连接图> E G 功 能 0 0 直通Qi = Di 0 1 保持(Qi保持不变) 1 X 输出高阻 <74LS373功能表> E G D Q

L H H H L H L L L L X Q 上表是74LS373的真值表,表中: L——低电平; H——高电平; X——不定态; Q0——建立稳态前Q的电平; G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。 当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同; 当G为下降沿时,将输入数据锁存。 8255A(2) 7.2 可编程并行接口 由于我们现在常用的微机系统均以并行方式处理数据,所以,

并行接口也是最常用的接口电路。并行接口有以下几方面的特点:(1)并行接口是在多根数据线上,以数据字节(字)为单位与输入/输出设备或被控对象传送信息的,如打印机接口、A/D、D /A转换器接口、IEEE-488接口、开关量接口、控制设备接口等。在实际应用中,凡在CPU与外设之间同时需要两位以上信息传送时,就要采用并行口。 并行口适用于近距离传送的场合。由于各种I/O设备和被控对象多为并行数据线连接,CPU用并行口来组成应用系统很方便,故使用十分普遍。 (2)并行传送的信息,不要求固定的格式,这与串行传送的信息有数据格式的要求不同。例如,异步串行通信的格式是一个数据,它包括起始位、数据位、校验位和停止位。 (3)从并行接口的电路结构来看,并行口有硬线连接接口和可编程接口之分。硬线连接接口的工作方式及功能用硬线连接来设定,用软件编程序的方法不能加以改变;如果接口的工作方式及功能可以用软件编程序的方法加以改变,则就叫可编程接口。 7.2.1 可编程并行接口芯片8255A 所谓可编程,实际上就是具有可选择性。例如,选择芯片中的哪一个或哪几个数据端口与外设连接;选择端口中的哪一位或哪几位作输入,哪一位或哪几位作输出;选择端口与CPU之间采用哪种方式传送数据等,均可由用户在程序中写入方式字或控制字来进行指定。

常用芯片引脚图(1)

附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口 无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O接口,第二功能作为为单片机的控 制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) V REF:A/D转换器基准电源引脚(+5V)P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST INT0/P3.2 INT1/P3.3 WR/P3.6 RD/P3.7 XTAL2 XTAL1 V SS