Verilog中generate的用法

一:generate

Verilog-2001添加了generate循环,允许产生module和primitive的多个实例化,同时也可以产生多个variable,net,task,function,continous assignment,initial和always。在generate 语句中可以引入if-else和case语句,根据条件不同产生不同的实例化。

用法:

1. generate语法有generate for, genreate if和generate case三种

2. generate for语句必须有genvar关键字定义for的变量

3. for 的内容必须加begin和end

4. 必须给for语段起个名字

例子:

1. generate for例子:

generate

genvar i; //generate 8 samll fifo for in_data[i] 8X72

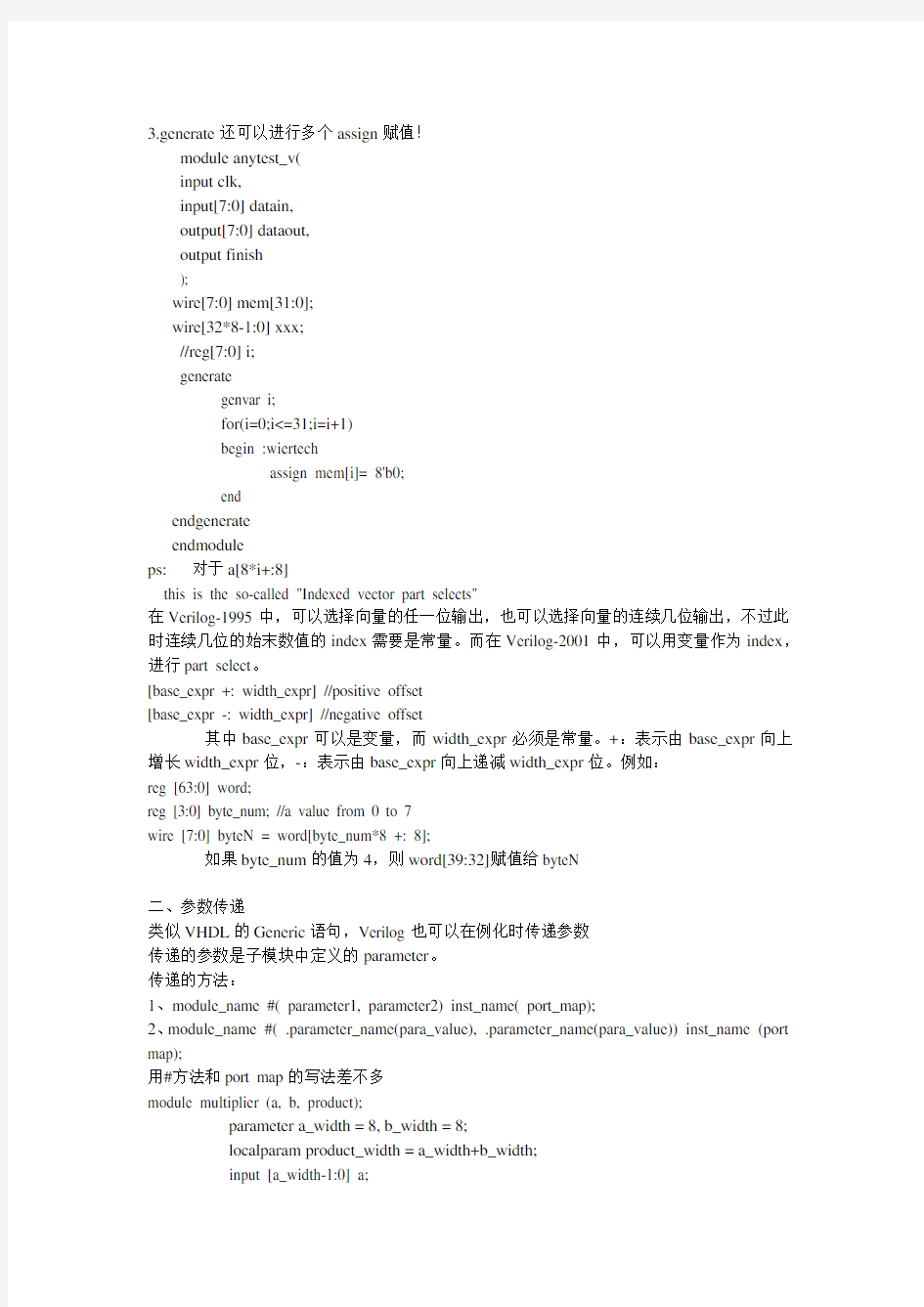

for(i=0; i #( .WIDTH(DATA_WIDTH+CTRL_WIDTH), .MAX_DEPTH_BITS(2)) in_arb_fifo (// Outputs .dout ({fifo_out_ctrl[i], fifo_out_data[i]}), .full (), .nearly_full (nearly_full[i]), .prog_full (), .empty (empty[i]), // Inputs .din ({in_ctrl[i], in_data[i]}), .wr_en (in_wr[i]), .rd_en (rd_en[i]), .reset (reset), .clk (clk)); end // block: in_arb_queues endgenerate 2.generate if例子: generate if (REG_WIDTH == WRITE_WIDTH) begin : new_data_a_generation assign new_data_a = merge_update ? merge_wr_data : held_wr_data_a; end else begin assign new_data_a = merge_update ? {{(REG_WIDTH - WRITE_WIDTH - 1){merge_wr_data_sign}}, merge_wr_data} : {{(REG_WIDTH - WRITE_WIDTH){held_wr_data_sign_a}}, held_wr_data_a}; end endgenerate 3.generate还可以进行多个assign赋值! module anytest_v( input clk, input[7:0] datain, output[7:0] dataout, output finish ); wire[7:0] mem[31:0]; wire[32*8-1:0] xxx; //reg[7:0] i; generate genvar i; for(i=0;i<=31;i=i+1) begin :wiertech assign mem[i]= 8'b0; end endgenerate endmodule ps: 对于a[8*i+:8] this is the so-called "Indexed vector part selects" 在Verilog-1995中,可以选择向量的任一位输出,也可以选择向量的连续几位输出,不过此时连续几位的始末数值的index需要是常量。而在Verilog-2001中,可以用变量作为index,进行part select。 [base_expr +: width_expr] //positive offset [base_expr -: width_expr] //negative offset 其中base_expr可以是变量,而width_expr必须是常量。+:表示由base_expr向上增长width_expr位,-:表示由base_expr向上递减width_expr位。例如: reg [63:0] word; reg [3:0] byte_num; //a value from 0 to 7 wire [7:0] byteN = word[byte_num*8 +: 8]; 如果byte_num的值为4,则word[39:32]赋值给byteN 二、参数传递 类似VHDL的Generic语句,Verilog也可以在例化时传递参数 传递的参数是子模块中定义的parameter。 传递的方法: 1、module_name #( parameter1, parameter2) inst_name( port_map); 2、module_name #( .parameter_name(para_value), .parameter_name(para_value)) inst_name (port map); 用#方法和port map的写法差不多 module multiplier (a, b, product); parameter a_width = 8, b_width = 8; localparam product_width = a_width+b_width; input [a_width-1:0] a; input [b_width-1:0] b; output[product_width-1:0]product; generate if((a_width < 8) || (b_width < 8)) CLA_multiplier #(a_width, b_width) u1 (a, b, product); else WALLACE_multiplier #(a_width, b_width) u1 (a, b, product); endgenerate endmodule 常用的RTL语法结构如下: ☆模块声明:module……endmodule ☆端口声明:input,output,inout(inout的用法比较特殊,需要注意) ☆信号类型:wire,reg,tri等,integer常用语for语句中(reg,wire时最常用的,一般tri和integer 不用) ☆参数定义:parameter ☆运算操作符:各种逻辑操作符、移位操作符、算术操作符大多时可综合的(注:===与!==是不可综合的) ☆比较判断:if……else,case(casex,casez)……default endcase ☆连续赋值:assign,问号表达式(?:) ☆always模块:(敏感表可以为电平、沿信号posedge/negedge;通常和@连用) ☆begin……end(通俗的说,它就是C语言里的“{ }”) ☆任务定义:task……endtask ☆循环语句:for(用的也比较少,但是在一些特定的设计中使用它会起到事半功倍的效果) ☆赋值符号:= 和<= (阻塞和非阻塞赋值,在具体设计中时很有讲究的) 可综合的语法时verilog可用语法里很小的一个子集,用最精简的语句描述最复杂的硬件,这也正是硬件描述语言的本质。对于做RTL级设计来说,掌握好上面这些基本语法是很重要。 相信大家在看了这么多了verilog语法书籍以后一定有点烦了,那么现在我告诉大家一个好消息,对于一个RTL级的设计来说,掌握了上面的语法就已经足够了,无论多么牛逼的工程师,在他的代码 里无非也就是上面一些语法而已。当然了,对于一个能够进行很好的仿真验证的代码,一般还需要在RTL级的设计代码中添加一些延时之类的语句,比如大家一定知道#10的作用,就是延时10个单位时间,这个语句虽然在仿真的时候是实实在在的延时,但是这个语句在综合后是会被忽略的,也就是说在我们综合并且布局布线最后烧进FPGA里,这个#10的延时是不会在硬件上实现的。所以说,上面给出的这些语法才是可以最后在硬件上实现的,其它的语法大多会在综合后被忽略。这么一来大家就要问了,为什么语法书里又要给出这么多的语法呢?呵呵,它们大都是为仿真验证是写testbench 准备的,先点到为止,下集继续! 对于模型(module)的建立,要保证可综合性应该注意: (1)不使用initial。(被忽略) (2)不使用#10。(被忽略) (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。(10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。 VerilogHDL硬件描述语言复习 一、 1.VerilogHDL是在哪一年首次被IEEE标准化的? 答:VerilogHDL是在1995年首次被IEEE标准化的。 2.VerilogHDL支持哪三种基本描述方式? 答:VerilogHDL可采用三种不同方式或混合方式对设计建模。这些方式包括:行为描述方式—使用过程 化结 构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述 建模 3.VerilogHDL是由哪个公司最先开发的? 答:VerilogHDL是由GatewayDesignAutomation公司最先开发的 4.VerilogHDL中的两类主要数据类型什么? 答:线网数据类型和寄存器数据类型。线网类型表示构件间的物理连线,而寄存器类型表示 抽象的数据存储元件。 5.UDP代表什么? 答:UDP代表用户定义原语 6.写出两个开关级基本门的名称。答: pmosnmos 7.写出两个基本逻辑门的名称。答: andor 8.在数据流描述方式中使用什么语句描述一个设计? 答:设计的数据流行为使用连续赋值语句进行描述 9.采用结构描述方式描述1位全加器。 答: modulefull_add(a,b,cin,s,co); inputa,b,cin; outputs,co; wireS1,T1,T2,T3; xor X1(S1,a,b), X2(s,S1,cin); and A1(T3,a,b), A2(T2,b,cin), A3(T1,a,cin); or O1(co,T1,T2,T3); endmodule 10.initial语句与always语句的关键区别是什么? 答:1)initial语句:此语句只执行一次。 2)always语句:此语句总是循环执行,或者说此语句重复执行。 11.采用数据流方式描述2-4译码器。 答: 'timescale1ns/ns moduleDecoder2×4(A,B,EN,Z); inputA,B,EN; output[0:3]Z; 1 基于Verilog HDL语言的可综合性设计 1 引言 逻辑综合带来了数字设计行业的革命,有效地提高了生产率,减少了设计周期时间。在手动转换设计的年代,设计过程受到诸多限制,结更容易带来人为的错误。而一个小小的错误就导致整个模块需进行重新设计,设计转换工作占去了整个设计周期的大部分时间,验证工作进行困难,设计技术无法重用等等。而自动逻辑综合工具的出现,突破了上述种种限制,使得设计者从繁琐的转换工作中解脱出来,将更多的时间用于验证和优化,不仅保证了功能的实现,而且有利于提高性能。可见,综合在逻辑设计中具有举足轻重的作用。 2 综合的概念及其过程 2.1 逻辑综合概述 综合就是在给定标准元件库和一定的设计约束条件下,把用语言描述的电路模型转换成门级网表的过程。要完成一次综合过程,必须包含三要素:RTL级描述、约束条件和工艺库。 2.2 RTL级描述 RTL级描述是以规定设计中采用各种寄存器形式为特征,然后在寄存器之间插入组合逻辑,其可以用如图1所示的“寄存器和云图”方式来表示。 图1 RTL级描述 2.3 约束条件 为了控制优化输出和映射工艺要用约束,它为优化和映射试图满足的工艺约束提供了目标,并且它们控制设计的结构实现方式。目前综合工具中可用的约束包括面积、速度、功耗和可测性约束,未来我们或许会看到对封装的约束和对布图的约束等,但是,目前的最普遍的约束是按面积和按时间的约束。 时钟限制条件规定时钟的工作频率,面积限制条件规定该设计将花的最大面积。综合工具将试图用各种可能的规则和算法尽可能地满足这些条件。 2.4 工艺库 按照所希望的逻辑行为功能和有关的约束建立设计的网表时,工艺库持有综合工具必须的全部信息。工艺库含有允许综合进程为建立设计做正确选择的全部信息,工艺库不仅含有ASIC单元的逻辑功能,而且还有该单元的面积、单元输入到输出的定时关系、有关单元扇出的某种限制和对单元所需的定时检查。 Select Case语句也是条件语句之一,而且是功能最强大的条件语句。它主要用于多条件判断,而且其条件设置灵活、方便,在工作中使用频率极高。本节介绍Select Case语句的语法及应用案例. Select Case语句的语法如下: Select Case testexpression [Case expressionlist-n [statements-n]] ... [Case Else [elsestatements]] End Select Select Case语句包括四部分,每部分详细含义如表38-1所示。 在以上语法列表中,省略号代表可以使用多个条件。只要有一个Case就需要有一个statements-n,表示条件及符合条件时的执行条件。 其中elsestatements表示不符合指定条件时的执行语句,是可选参数。可以忽略elsestatements,也可以执行一条或者一组语句,为了让程序能够处理一些不可预见的情况,尽量使用elsestatements语句处理不符合条件时该如何回应。 在Select Case的多个参数中,最复杂的是expressionlist-n部分,它有多种表达形式,包括:lExpression——直接声明一个条件值,例如5 lexpression To expression——声明一个条件的范围,例如5-10 lIs comparisonoperator——声明一种比较方式,例如is >5 下面的实例可以展示参数中expressionlist-n部分的多种表达形式。 实例1:多条件时间判断 根据当前的时间判断是上午、中午,还是下午、晚上、午夜。 要求中条件比较多,使IF…Then…需要多层嵌套,而Select Case语句会更简单。代码如下:___________________________________________________ Sub 时间() Dim Tim As Byte, msg As String C语言——switch case语句 switch语句的语法如下(switch,case和default是关键字): switch ( 表达式) { case 常量表达式1 :语句1;break; case 常量表达式2 :语句2;break; …… case 常量表达式n :语句n;break; default:语句n+1;break; } 说明: break退出{ } case后面只能跟一个值(加冒号:),而不能是一个表达式 switch(表达式) 后面没有;(分号) { }前后没有;(分号) switch语句规则 case标签必须是常量表达式(constant Expression) 只能针对基本数据类型使用switch,这些类型包括int、char等。对于其他类型,则必须使用if语句。 case 标签后不能是浮点型数据(如1.0 ) case标签必须是惟一性的表达式;也就是说,不允许两个case具有相同的值。 不要问为什么,C就这规定!我们只需要了解规则,学会应用即可! 猜想原因:浮点型数据不是准确的数据,在机器中只能表示出一个近似值,如:0.1 在机器中存的是0.09999612.... 也可能是0.09999723.... 根据精度不同,数据来源不同,其值是个不确定的数据,因此,不能用CASE来定位 简单例题1: #include 1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:(1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 综合:不可综合的运算符:= = = ,!= =,/(除法),%(取余数)。 1、不使用初始化语句。 2、不使用带有延时的描述。 3、不使用循环次数不确定的循环语句,如:forever、while等。 4、尽量采用同步方式设计电路。 5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 6、用always过程块描述组合逻辑,应在信号敏感列表中列出所有的输入信号。 7、所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 8、在verilog模块中,任务(task)通常被综合成组合逻辑的形式,每个函数(function)在调用时通常也被综合为一个独立的组合电路模块。 9、用户自定义原语(UDP)是不可综合的,它只能用来建立门级元件的仿真模型。 一般综合工具支持的V erilog HDL结构 移位运算符:V erilog HDL提供向右(>>)及向左(<<)两种运算符,运算符高位或地位一旦移出即予丢弃,其空缺的位则予以补零。 连续赋值语句(assign)、case语句、if…else语句都是可以综合的 initial 语句内若包含有多个语句时,必须以begin end 作聚合;单一的初值赋值,因此并不需以begin end做聚合。 循环(Loops)并不能单独地在程序中存在,而必须在initial和always块中才能使用。initial过程块中的语句仅执行一次,而always块中的语句是不断重复执行的。 编写顶层模块的注意事项 每个端口除了要声明是输入、输出还是双向外,还要声明其数据类型,是连线型(wire)还是寄存器型(reg),如果没有声明则综合器默认为wire型。 1、输入和双向端口不能声明为寄存器型。 2、在测试模块中不需要定义端口。 编写testbentch所归纳的心得 1)所有综合工具都支持的结构: always,assign,begin,end,case,wire,tri,supply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 2)所有综合工具都不支持的结构: time,defparam,$finish,fork,join,initial,delays,UDP,wait。 3)有些工具支持有些工具不支持的结构: casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: 1)不使用initial。 2)不使用#10。 3)不使用循环次数不确定的循环语句,如forever、while等。 4)不使用用户自定义原语(UDP元件)。 5)尽量使用同步方式设计电路。 6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对 复习: 输入三个数a,b,c,输出最大数(分别用不嵌套if 和嵌套的if语句) (提问) 4.4 Case语句 [例4-4-1] 某服装公司为了推销产品,采取这样的批发销售方案:凡订购超过100 套的,每套定价为50元,否则每套价格为80元。编程由键盘输入订购套数,输出应付款的金额数。 解:设X为订购套数,Y为付款金额,则: Var x,y: integer; Begin Write('X=') ;Readln(x) ; if x >100 then y:=50*X else y:=80*X; Writeln('y=',y) ; Readln End. 如果有多种(两种或两种以上)选择,常用情况语句编程。 将前面[例]改成用如下方法来处理。根据题意,付款计算可分为两种情况: ①Y=50*X (X>100) ②Y=80*X (X<=100) 显然,情况①与②的选择取决于X值。假设用N表示“情况值”,暂且先让N =2; 如果X>100则N=1;(此题中N的值只是1或2,且取决于X值) Var X,Y,N: integer; Begin Write('X=') ;readln(x) ;n:=2;{ 先让n=2 } if X>100 then n:=1;{如果X>100则n=1 } Case n of { 关于情况处理} 1: Y:=50*X; 2: Y:=80*X; end; Writeln('Y=',Y) ; Readln End. 程序中的Case─end 语句为情况语句,是多路分支控制,一般格式为: 格式一: case 表达式of 情况常量表1:语句1; 情况常量表2:语句2; …… 情况常量表n:语句n; end; 格式一:执行情况语句时,先计算Case后面表达式的值,然后根据该值在情况常量表中的“对应安排”,选择其对应的语句执行,执行完所选择语句后就结束Case语句;如果常量表中没有一个与表达式值对应的语句,则什么也不做就结束本Case语句。 格式二: Case 表达式of 情况常量表1: 语句1; 情况常量表2: 语句2; …… 情况常量表n: 语句n; else 语句n+1 end; 格式二:这种格式的前面部分是相同的,所不同的是:如果常量表中没有一个与表达式值对应的语句,则执行与else对应的语句,然后结束Case语句。 case语句在使用时有几点要注意: 1. end与case对应;标号与语句之间用“:”分隔;else与语句之间不用分隔符。2.表达式的类型通常是整型或字符型。所以表达式经常会用到mod、div运算和trunc、round等函数。 3.情况常量表必须是一个或几个常量,常量间用“,”间隔,其类型与表达式的类型一致。常量间的顺序可以是任意的。也就是说可以多个标号对应同一条语句。 4. 语句可以是多个语句,但必须用语句括号(begin……end)括起即复合语句。 5. case语句也可以嵌套 [例4-4-2] 对某产品征收税金,在产值1万元以上征收税5%;在1万元以下但在5000元以上的征收税3%;在5000元以下但在1000元以上征收税2%;1000元以下的免收税。编程计算该产品的收税金额。 解:设x为产值,tax为税金,用P表示情况常量各值,以题意中每1000元为情况分界: P=0: tax=0 (x<1000 ) P=1,2,3,4: tax=x*0.02 (1000<=x<5000 ) P=5,6,7,8,9: tax=x*0.03 (5000 Verilog的综合与不可综合 综合说明编的代码可以对应出具体的电路,不可综合说明没有对应的电路结构。不可综合的代码编译通过,只能看到输出,不能实现电路,就是不能用来制作具体的芯片。 一、基本 Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。 二:verilog语句结构到门级的映射 1、连续性赋值:assign 连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。因些连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。Assign语句中的延时综合时都将忽视。 2、过程性赋值: 过程性赋值只出现在always语句中。 阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。 建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。 过程性赋值的赋值对象有可能综合成wire,latch,和flip-flop,取决于具体状况。如,时钟控制下的非阻塞赋值综合成flip-flop。 过程性赋值语句中的任何延时在综合时都将忽略。 建议同一个变量单一地使用阻塞或者非阻塞赋值。 3、逻辑操作符: 逻辑操作符对应于硬件中已有的逻辑门 4、算术操作符: Verilog中将reg视为无符号数,而integer视为有符号数。因此,进行有符号操作时使用integer,使用无符号操作时使用reg。 5、进位: 通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。如: Wire [3:0] A,B; Wire [4:0] C; Assign C=A+B; C的最高位用来存放进位。 6、关系运算符: 关系运算符:<,>,<=,>= 和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net还是integer。 CASE语句 在某些方面,CASE语句是几种不同语句的一种等价物,这些语句来自你之前学过的语言。在过程化的编程语言中,下面的语句与CASE的功能相似: Switch: C、C++、C#、Delphi Select Case:Visual Basic Do Case:Xbase Evaluate:COBOL 我可以肯定还有其他语句,它们来自我多年前以这种或那种形式使用的语言。在许多方面,在T-SQL中使用CASE语句的最大缺陷是置换运算符而不是流控制语句。 书写CASE语句的方法不止一种:可以使用输入表达式或布尔表达式。第一种选择是可以使用一个输入表达式,将它与每一个WHEN子句中使用的值进行比较。SQL Server将其视为简单CASE: 1.CASE 2.WHEN verilog 不可综合语句总结汇总 2009-04-20 18:37 (1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。 (13)同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。 (14)避免在case语句的分支项中使用x值或z值。 不可综合verilog语句2009-04-14 19:33 C语言switch语句的用法详解 C语言还提供了另一种用于多分支选择的switch语句,其一般形式为: switch(表达式){ case 常量表达式1: 语句1; case 常量表达式2: 语句2; … case 常量表达式n: 语句n; default: 语句n+1; } 其语义是:计算表达式的值。并逐个与其后的常量表达式值相比较,当表达式的值与某个常量表达式的值相等时,即执行其后的语句,然后不再进行判断,继续执行后面所有case 后的语句。如表达式的值与所有case后的常量表达式均不相同时,则执行default后的语句。 【例4-9】 1.#include 12.case6:printf("Saturday\n"); 13.case7:printf("Sunday\n"); 14.default:printf("error\n"); 15.} 16.return0; 17.} 本程序是要求输入一个数字,输出一个英文单词。但是当输入3之后,却执行了case3以及以后的所有语句,输出了Wednesday 及以后的所有单词。这当然是不希望的。为什么会出现这种情况呢?这恰恰反应了switch语句的一个特点。在switch语句中,“case 常量表达式”只相当于一个语句标号,表达式的值和某标号相等则转向该标号执行,但不能在执行完该标号的语句后自动跳出整个switch 语句,所以出现了继续执行所有后面case 语句的情况。这是与前面介绍的if语句完全不同的,应特别注意。 为了避免上述情况,C语言还提供了一种break语句,专用于跳出switch语句,break 语句只有关键字break,没有参数。在后面还将详细介绍。修改例题的程序,在每一case语句之后增加break 语句,使每一次执行之后均可跳出switch语句,从而避免输出不应有的结果。 【例4-10】 1.#include module mux4_to_1case (out,i0,i1,i2,i3,s1,s0); output out; input i0,i1,i2,i3,s1,s0; reg out; always@(i0 or i1 or i2 or i3 or s1 or s0) case({s1,s0}) 2'd0:out =i0; 2'd1:out =i1; 2'd2:out =i2; 2'd3:out =i3; endcase endmodule module case4_1; reg IN0,IN1,IN2,IN3; reg S1,S0; wire OUTPUT; mux4_to_1case m1(OUTPUT,IN0,IN1,IN2,IN3,S1,S0); initial begin IN0 =1;IN1 = 0;IN2 = 1;IN3 = 0; #0 $display("IN0=%b,IN1=%b,IN2=%b,IN3=%b\n",IN0,IN1,IN2,IN3); S1=0; S0=0; #1 $display("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT); S1=0; S0=1; #1 $display("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT); S1=1; S0=0; #1 $display("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT); S1=1; S0=1; #1 $display("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT); end endmodule 6、表RSDA.DBF结构为:姓名(C,6);性别(C,2),年龄(N,2),出生日期(D,8)。判断表中是否有"李明",查询此人的性别及年龄,确定参加运动会的项目。 SET TALK OFF USE RSDA ***********SPACE********** 【?】 FOR 姓名= "李明" ***********SPACE********** IF .NOT. 【?】 DO CASE CASE 性别= "男" ?"请参加爬山比赛" CASE 年龄<=50 ? "请参加投篮比赛" CASE 年龄<=60 ? "请参加老年迪斯科比赛" ***********SPACE********** 【?】 ELSE ? "查无此人" BROWSE ENDIF USE SET TALK ON RETURN 『答案』: 1 LOCATE 或 LOCA 或 LOCATE★ALL 2 EOF() 3 ENDCASE 或 ENDC 13、对表XSDB.DBF中的计算机和英语都大于等于90分以上的学生奖学金进行调整:法律系学生奖学金增加12元、英语系学生奖学金增加15元、中文系学生奖学金增加18元,其他系学生奖学金增加20元。请在【】处添上适当的内容,使程序完整。 USE XSDB ***********SPACE********** 【?】 DO WHILE FOUN() DO CASE CASE 系别="法律" ZJ=12 CASE 系别="英语" ZJ=15 CASE 系别="中文" ZJ=18 ***********SPACE********** 【?】 ZJ=20 ENDCASE (1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。 (13)同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。 (14)避免在case语句的分支项中使用x值或z值。 不可综合verilog语句2009-04-1419:33 1、initial 只能在test bench中使用,不能综合。(我用ISE9.1综合时,有的简单的initial也可以综合,不知道为什么) 2、events event在同步test bench时更有用,不能综合。 3、real 不支持real数据类型的综合。 4、time 不支持time数据类型的综合。 if语句处理两个分支,处理多个分支时需使用if-else-if结构,但如果分支较多,则嵌套的if语句层就越多,程序不但庞大而且理解也比较困难.因此,C语言又提供了一个专门用于处理多分支结构的条件选择语句,称为switch语句,又称开关语句.使用switch语句直接处理多个分支(当然包括两个分支).其一般形式为: 引用 switch(表达式) { case 常量表达式1: 语句1; break; case 常量表达式2: 语句2; break; …… case 常量表达式n: 语句n; break; default: 语句n+1; break; } switch语句的执行流程是:首先计算switch后面圆括号中表达式的值,然后用此值依次与各个case的常量表达式比较,若圆括号中表达式的值与某个case后面的常量表达式的值相等,就执行此case后面的语句,执行后遇break语句就退出switch语句;若圆括号中表达式的值与所有case后面的常量表达式都不等,则执行default后面的语句n+1,然后退出switch语句,程序流程转向开关语句的下一个语句.如下程序,可以根据输入的考试成绩的等级,输出百分制分数段: 引用 switch(grade) { case 'A': /*注意,这里是冒号:并不是分号;*/ printf("85-100\n"); break; /*每一个case语句后都要跟一个break用来退出switch 语句*/ case 'B': /*每一个case后的常量表达式必须是不同的值以保证 分支的唯一性*/ printf("70-84\n"); break; case 'C': printf("60-69\n"); break; case 'D': printf("<60\n"); break; default: printf("error!\n"); } (2) 如果在case后面包含多条执行语句时,也不需要像if语句那样加大括号,进入某个case后,会自动顺序执行本case后面的所有执行语句.如: 引用 { case 'A': if(grade<=100) printf("85-100\n"); else printf("error\n"); break; …… (3) default总是放在最后,这时default后不需要break语句.并且,default 部分也不是必须的,如果没有这一部分,当switch后面圆括号中表达式的值与所有case后面的常量表达式的值都不相等时,则不执行任何一个分支直接退出switch语句.此时,switch语句相当于一个空语句.例如,将上面例子中switch 语句中的default部分去掉,则当输入的字符不是"A","B","C"或"D"时,此switch语句中的任何一条语句也不被执行. (4) 在switch-case语句中,多个case可以共用一条执行语句,如: 可综合Verilog语句 ?一: 综合就是从采用Verilog HDL 语言描述的寄存器传输级电路模型构造出门级网表的过程.产生门级网表之后,逻辑优化器读入网表并以用户指定的面积和定时约束为目标优化网表. ?二. 设计流程中的综合 ?Verilog HDL允许用户在不同的抽象层次上对电路进行建模,这些层次从门级、寄存器传输级、行为级直至算法级。因此,同一电路就可以有多种不同的描述方式,但不是每一中描述都是可综合的。事实上,Verilog HDL 原本被设计成一种仿真语言,而不时一种综合语言。结果导致Verilog HDL 中很多结构没有相应的硬件可以对应,例如系统调用$display.同样也不存在用于寄存器传输级综合的Verilog HDL 标准子集.?正是由于存在这些问题,不同的综合系统所支持的Verilog HDL 综合子集是不同的.由于Verilog HDL 中不存在单个的对象来表示锁存器或触发器,所以每一种综合系统都会提供不同的机制以实现锁存器或触发器的建模.因此各种综合系统都定义了自己的Verilog HDL 可综合子集以及自己的建模方式. ?使用Verilog HDL 以不同的方式描述了同一电路.某综合系统支持对方式A和方式B的综合,但可能不支持对方式C的综合,这意味着综合模型在不同的综合系统之间通常是不可移植的. ?这一局限性使设计者不仅需要理解Verilog HDL ,而且必须理解特定综合系统的建模方式, 才能编写出可综合的模型.可综合的数据类型?1.网线数据类型: ?Wire,wor,wand,tri,supply0,supply1 ?2.寄存器数据类型: ?Reg,integer ?Time,real:不能综合. ?3.常量: ?整型. ?实型和字符串型不能综合.可综合的运算符?1.逻辑运算符能直接映射成硬件中的基本逻辑门. ?2.算术运算符 ?3.关系运算符: ?能综合的有:>,<,<=,>=. ?4.相等性算符: ?能够综合的有:==和!=. ?不能综合:===和!==(有些工具按==和!=综合). ?5.移位运算符: ?<<和>>,移位腾出的位都补0. 多个时钟的可综合情况 ?1.多个时钟的情况:对变量的赋值不能受多个时钟控制 例如: ? module multclk(clk1,clk2,addclk,and,rstn,subclr,subn,dsadd,dssub);可综合的Verilog语法子集总汇

VerilogHDL复习题与答案

基于VerilogHDL语言的可综合性设计

VBA中的Select Case语句

switch case用法示例

Verilog可综合与不可综合语句汇总

verilog综合心得

verilog语句可综合vs不可综合

case语句

verilog语言的综合与不可综合

case的两种表现方式和使用

verilog不可被综合的语句

switch语句的用法

case语句 四选一

do case 语句

FPGA中不可综合语句汇总

switch语句的用法

可综合的Verilog语句

- switch case用法示例

- SELECT_CASE语句(选)

- Oracle CASE条件语句

- switch-case语句用法

- C语言:switch case语句的使用

- pascl语言编程之case语句

- case的两种表现方式和使用

- switch语句的用法

- case的用法

- MATLAB+switch+case+语句使用实例+源程序

- VBA中的Select Case语句

- VHDL主要描述语句――CASE语句

- 选择结构Select Case语句

- SQL中Case语句用法

- pascal中Case语句

- case语句

- do case 语句

- switch语句最全

- Select Case语句

- CASE语句