元件例化语句实现4位全加器VHDL源程序

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY half_adder IS --一位半加器

PORT ( A,B : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END half_adder;

ARCHITECTURE rtl OF half_adder IS

SIGNAL tmp1,tmp2 : std_logic;

BEGIN

tmp1 <= A OR B;

tmp2 <= A NAND B;

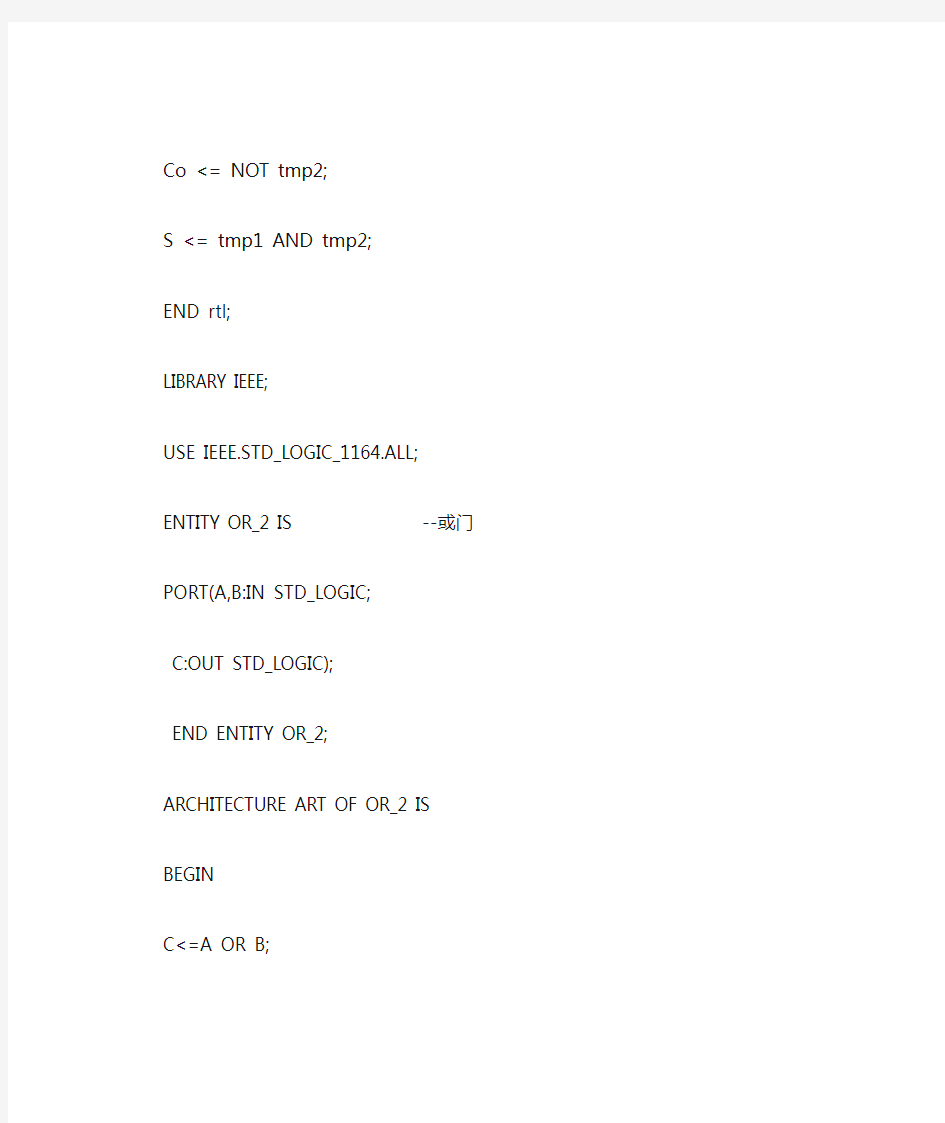

Co <= NOT tmp2;

S <= tmp1 AND tmp2;

END rtl;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY OR_2 IS --或门

PORT(A,B:IN STD_LOGIC;

C:OUT STD_LOGIC);

END ENTITY OR_2;

ARCHITECTURE ART OF OR_2 IS

BEGIN

C<=A OR B;

END ARCHITECTURE ART;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY full_adder IS --结构描述法设计一位全加器PORT(A,B,Cin:IN STD_LOGIC;

S,Co:OUT STD_LOGIC);

END full_adder;

ARCHITECTURE structure OF full_adder IS

SIGNAL tmp1,tmp2,tmp3 : std_logic;

COMPONENT half_adder

PORT(A,B : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END COMPONENT;

COMPONENT OR_2

PORT(a,b : IN std_logic;

c : OUT std_logic);

END COMPONENT;

BEGIN

U0: half_adder

PORT MAP(A,B,tmp2,tmp1);

U1: half_adder

PORT MAP(tmp1,Cin,tmp3,S);

U2: OR_2

PORT MAP(tmp3,tmp2,Co);

END structure;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY full_adder_4 IS

PORT(X,Y:IN STD_LOGIC_VECTOR(1 TO 4);

C:IN STD_LOGIC;

SUM:OUT STD_LOGIC_VECTOR(1 TO 4);

CO:OUT STD_LOGIC);

END full_adder_4;

ARCHITECTURE struct OF full_adder_4 IS--结构描述法设计四位全加器COMPONENT full_adder

PORT(A,B,Cin:IN STD_LOGIC;

S,CO:OUT STD_LOGIC);

END COMPONENT;

SIGNAL temp1,temp2,temp3,temp4:STD_LOGIC;

BEGIN

U1:full_adder PORT MAP(X(1),Y(1),C,SUM(1),temp1);

U2:full_adder PORT MAP(A=>X(2),B=>Y(2),Cin=>temp1,S=>SUM(2),Co=>temp2); U3:full_adder PORT MAP(A=>X(3),B=>Y(3),Cin=>temp2,S=>SUM(3),Co=>temp3); U4:full_adder PORT MAP(A=>X(4),B=>Y(4),Cin=>temp3,S=>SUM(4),Co=>temp4); CO<=temp4;

END struct;

可综合的Verilog语法子集总汇

常用的RTL语法结构如下: ☆模块声明:module……endmodule ☆端口声明:input,output,inout(inout的用法比较特殊,需要注意) ☆信号类型:wire,reg,tri等,integer常用语for语句中(reg,wire时最常用的,一般tri和integer 不用) ☆参数定义:parameter ☆运算操作符:各种逻辑操作符、移位操作符、算术操作符大多时可综合的(注:===与!==是不可综合的) ☆比较判断:if……else,case(casex,casez)……default endcase ☆连续赋值:assign,问号表达式(?:) ☆always模块:(敏感表可以为电平、沿信号posedge/negedge;通常和@连用) ☆begin……end(通俗的说,它就是C语言里的“{ }”) ☆任务定义:task……endtask ☆循环语句:for(用的也比较少,但是在一些特定的设计中使用它会起到事半功倍的效果) ☆赋值符号:= 和<= (阻塞和非阻塞赋值,在具体设计中时很有讲究的) 可综合的语法时verilog可用语法里很小的一个子集,用最精简的语句描述最复杂的硬件,这也正是硬件描述语言的本质。对于做RTL级设计来说,掌握好上面这些基本语法是很重要。 相信大家在看了这么多了verilog语法书籍以后一定有点烦了,那么现在我告诉大家一个好消息,对于一个RTL级的设计来说,掌握了上面的语法就已经足够了,无论多么牛逼的工程师,在他的代码

里无非也就是上面一些语法而已。当然了,对于一个能够进行很好的仿真验证的代码,一般还需要在RTL级的设计代码中添加一些延时之类的语句,比如大家一定知道#10的作用,就是延时10个单位时间,这个语句虽然在仿真的时候是实实在在的延时,但是这个语句在综合后是会被忽略的,也就是说在我们综合并且布局布线最后烧进FPGA里,这个#10的延时是不会在硬件上实现的。所以说,上面给出的这些语法才是可以最后在硬件上实现的,其它的语法大多会在综合后被忽略。这么一来大家就要问了,为什么语法书里又要给出这么多的语法呢?呵呵,它们大都是为仿真验证是写testbench 准备的,先点到为止,下集继续! 对于模型(module)的建立,要保证可综合性应该注意: (1)不使用initial。(被忽略) (2)不使用#10。(被忽略) (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。(10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。

基于VerilogHDL语言的可综合性设计

基于Verilog HDL语言的可综合性设计 1 引言 逻辑综合带来了数字设计行业的革命,有效地提高了生产率,减少了设计周期时间。在手动转换设计的年代,设计过程受到诸多限制,结更容易带来人为的错误。而一个小小的错误就导致整个模块需进行重新设计,设计转换工作占去了整个设计周期的大部分时间,验证工作进行困难,设计技术无法重用等等。而自动逻辑综合工具的出现,突破了上述种种限制,使得设计者从繁琐的转换工作中解脱出来,将更多的时间用于验证和优化,不仅保证了功能的实现,而且有利于提高性能。可见,综合在逻辑设计中具有举足轻重的作用。 2 综合的概念及其过程 2.1 逻辑综合概述 综合就是在给定标准元件库和一定的设计约束条件下,把用语言描述的电路模型转换成门级网表的过程。要完成一次综合过程,必须包含三要素:RTL级描述、约束条件和工艺库。 2.2 RTL级描述 RTL级描述是以规定设计中采用各种寄存器形式为特征,然后在寄存器之间插入组合逻辑,其可以用如图1所示的“寄存器和云图”方式来表示。 图1 RTL级描述 2.3 约束条件 为了控制优化输出和映射工艺要用约束,它为优化和映射试图满足的工艺约束提供了目标,并且它们控制设计的结构实现方式。目前综合工具中可用的约束包括面积、速度、功耗和可测性约束,未来我们或许会看到对封装的约束和对布图的约束等,但是,目前的最普遍的约束是按面积和按时间的约束。 时钟限制条件规定时钟的工作频率,面积限制条件规定该设计将花的最大面积。综合工具将试图用各种可能的规则和算法尽可能地满足这些条件。 2.4 工艺库 按照所希望的逻辑行为功能和有关的约束建立设计的网表时,工艺库持有综合工具必须的全部信息。工艺库含有允许综合进程为建立设计做正确选择的全部信息,工艺库不仅含有ASIC单元的逻辑功能,而且还有该单元的面积、单元输入到输出的定时关系、有关单元扇出的某种限制和对单元所需的定时检查。

VHDL编写一位全加器参考程序

这是茄子求别人写的参考程序,不一定能实际运行。但是可靠性在百分之九十左右。大家做不出来的可以参考下。做出来的看出错误请指正。我作为学习委员既然把答案给大家,一方面是不想影响大家平时成绩,另一方面也是希望大家可以自己看看,学习一下,不要到最后结课了着急。所以我晚上不收打印的作业,每个人都必须亲自抄写出来。 行为描述方式 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADD11 IS PORT(A:IN STD_LOGIC; B:IN STD_LOGIC; CIN:IN STD_LOGIC; CO:OUT STD_LOGIC; S:OUT STD_LOGIC); END ADD11; ARCHITECTURE BEHAVE OF ADD11 IS BEGIN PROCESS(A,B,CIN) VARIABLE N: INTEGER RANGE 0 TO 3; CONSTANT S_VECTOR: STD_LOGIC_VECTOR(0 TO 3):="1010"; CONSTANT CO_VECTOR: STD_LOGIC_VECTOR(0 TO 3):="1100"; BEGIN N:=0; IF(A='1') THEN N:=N+1; END IF; IF(B='1') THEN N:=N+1; END IF; IF(CIN='1') THEN N:=N+1; END IF; S<=S_VECTOR(N); CO<=CO_VECTOR(N); END PROCESS; END BEHAVE; 数据流描述方式 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY ADD2 IS PORT(A:IN STD_LOGIC; B:IN STD_LOGIC; CIN:IN STD_LOGIC; CO:OUT STD_LOGIC; S:OUT STD_LOGIC);

VHDL实现16位全加器

[键入公司名称] [键入文档标题] [键入文档副标题] 姓名:托列吾别克·马杰尼 班级:电路与系统01班 学号:201221020141 2013/11/24

基于VHDL的16位全加器的设计 1.1设计题目的内容及要求 1.1.1目的: CMOS数字集成电路设计流程及数字集成电路自动化设计,包括功能验证、VHDL/Verlog建模、同步电路设计、异步数据获取、能耗与散热、信号完整性、物理设计、设计验证等技术 1.1.2内容: 主要实验内容是用0.18μm数字CMOS工艺,VHDL或Verlog设计一个16位全加器,用Synthesis 仿真工具验证功能,电路合成,及性能检测。 1.1.3主要测试参数及指标范围: 16位的全加器主要的设计指标是高于1GHz的频率,功耗,物理面积大小等参数。 1.2全加器的组成和原理分析 全加器是常用的组合逻辑模块中的一种,对全加器的分析和对组合逻辑电 路的分析一样。组合逻辑电路的分析,就是找出给定电路输入和输出之间的逻 辑关系,从而了解给定逻辑电路的逻辑功能。组合逻辑电路的分析方法通常采 用代数法,一般按下列步骤进行: (1)根据所需要的功能,列出真值表。 (2)根据真值表,写出相应的逻辑函数表达式。 (3)根据真值表或逻辑函数表达式,画出相应的组合逻辑电路的逻辑图[1]。 (4)用VHDL编写程序在QUARTUSⅡ上进行模拟,并分析结果的正确性。 1.3 全加器简介

全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运算就是全加运算,实现全加运算的电路称为全加器。它主要实现加法的运算,其中分为并行全加器和串行全加器,所谓并行就是指向高位进位时是并行执行的,而串行就是从低位到高位按顺序执行,为了提高运算,必须设法减小或消除由于进位信号逐级传递所消耗的时间,为了提高运算速度,制成了超前进位加法器,这是对全加器的一种创新[2]。 1.3.1半加器的基本原理 如果不考虑有来自低位的进位将两个1位二进制数相加,称为半加。实现半加运算的电路称为半加器。 按照二进制加法运算规则可以列出如表2所示的半加器真值表,其中A、B 是两个加数,S是相加的和,CO是向高位的进位。将S、CO和A、B的关系写成逻辑表达式则得到 S=A B+A B=A+B CO=AB 表1 半加器的真值表 因此,半加器是由一个异或门和一个与门组成的,如图1所示。

verilog综合心得

综合:不可综合的运算符:= = = ,!= =,/(除法),%(取余数)。 1、不使用初始化语句。 2、不使用带有延时的描述。 3、不使用循环次数不确定的循环语句,如:forever、while等。 4、尽量采用同步方式设计电路。 5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 6、用always过程块描述组合逻辑,应在信号敏感列表中列出所有的输入信号。 7、所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 8、在verilog模块中,任务(task)通常被综合成组合逻辑的形式,每个函数(function)在调用时通常也被综合为一个独立的组合电路模块。 9、用户自定义原语(UDP)是不可综合的,它只能用来建立门级元件的仿真模型。 一般综合工具支持的V erilog HDL结构

移位运算符:V erilog HDL提供向右(>>)及向左(<<)两种运算符,运算符高位或地位一旦移出即予丢弃,其空缺的位则予以补零。 连续赋值语句(assign)、case语句、if…else语句都是可以综合的 initial 语句内若包含有多个语句时,必须以begin end 作聚合;单一的初值赋值,因此并不需以begin end做聚合。 循环(Loops)并不能单独地在程序中存在,而必须在initial和always块中才能使用。initial过程块中的语句仅执行一次,而always块中的语句是不断重复执行的。 编写顶层模块的注意事项 每个端口除了要声明是输入、输出还是双向外,还要声明其数据类型,是连线型(wire)还是寄存器型(reg),如果没有声明则综合器默认为wire型。 1、输入和双向端口不能声明为寄存器型。 2、在测试模块中不需要定义端口。 编写testbentch所归纳的心得

EDA与VHDL实现8位加法器

EDA技术与VHDL实训 姓名:李* 班级:电信**-* 学号:12******** 电子与信息工程学院

8位加法器设计 一实训目的 1.学习使用VHDL语言设计电路,加深对VHDL语言的理解与应用。 2.学习8位加法器的VHDL程序设计方法。 3.学习例化语句的应用,并能够利用例化语句完成从半加器到全加器的设计。 二加法器 加法器是为了实现加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。 对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。前三个量为输入量,后两个量为输出量,五个量均为1位。 对于32位的二进制加法,相关的也有五个量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。 要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT 提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。而最后的第32位必须在前31位全部计算出结果后,才能开始计算。这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。 三实训内容 首先设计半加器,然后用例化语句将它们连接起来。利用半加器和或门构成1位全加器,以1位全加器为基本硬件,构成串行进位的8位加法器。 3.1 设计1位半减器 利用真值表设计1位半减器。图3-1中的h_add是半加器,sum是输出和,a_out是进位输出,add_in是进位输入。 表3-1 加法真值表 加数x 加数y 和sum 进位a_out 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1

verilog语句可综合vs不可综合

1)所有综合工具都支持的结构: always,assign,begin,end,case,wire,tri,supply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 2)所有综合工具都不支持的结构: time,defparam,$finish,fork,join,initial,delays,UDP,wait。 3)有些工具支持有些工具不支持的结构: casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: 1)不使用initial。 2)不使用#10。 3)不使用循环次数不确定的循环语句,如forever、while等。 4)不使用用户自定义原语(UDP元件)。 5)尽量使用同步方式设计电路。 6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对

FPGA设计实例 四位加法器(含VHDL源程序)

EDA FPGA 四位加法器设计说明:程序使用原件例化语句编写。 半加器程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY bjq IS PORT(A,B:IN STD_LOGIC; Y,Co:OUT STD_LOGIC); END bjq; ARCHITECTURE bjqbehv OF bjq IS SIGNAL c,d:STD_LOGIC; BEGIN c<=A OR B; d<=A NAND B; Co<=NOT d; Y<=c AND d; END bjqbehv; 全加器程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY qjq IS PORT(Ci,A,B:IN STD_LOGIC;

S,Co:OUT STD_LOGIC); END qjq; ARCHITECTURE qjqbehv OF qjq IS BEGIN S<=A XOR B XOR Ci; Co<=(A AND B) OR (A AND Ci) OR (B AND Ci); END qjqbehv; 加法器例化程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY jfq4 IS PORT(A,B:IN STD_LOGIC_VECTOR(3 DOWNTO 0); y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); Co:OUT STD_LOGIC); END jfq4; ARCHITECTURE jfq4behv OF jfq4 IS COMPONENT qjq PORT(Ci,A,B:IN STD_LOGIC; S,Co:OUT STD_LOGIC); END COMPONENT; COMPONENT bjq PORT(A,B:IN STD_LOGIC; Y,Co:OUT STD_LOGIC); END COMPONENT; SIGNAL C0,C1,C2:STD_LOGIC; BEGIN u1:bjq PORT MAP(A(0),B(0),Y(0),C0); u2:qjq PORT MAP(C0,A(1),B(1),Y(1),C1); u3:qjq PORT MAP(C1,A(2),B(2),Y(2),C2); u4:qjq PORT MAP(C2,A(3),B(3),Y(3),Co); END ARCHITECTURE jfq4behv; 兄弟加qq 352995783,技术交流。 暮落 2011年12月2日

verilog语言的综合与不可综合

Verilog的综合与不可综合 综合说明编的代码可以对应出具体的电路,不可综合说明没有对应的电路结构。不可综合的代码编译通过,只能看到输出,不能实现电路,就是不能用来制作具体的芯片。 一、基本 Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。 二:verilog语句结构到门级的映射 1、连续性赋值:assign 连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。因些连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。Assign语句中的延时综合时都将忽视。 2、过程性赋值: 过程性赋值只出现在always语句中。 阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。 建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。 过程性赋值的赋值对象有可能综合成wire,latch,和flip-flop,取决于具体状况。如,时钟控制下的非阻塞赋值综合成flip-flop。 过程性赋值语句中的任何延时在综合时都将忽略。 建议同一个变量单一地使用阻塞或者非阻塞赋值。 3、逻辑操作符: 逻辑操作符对应于硬件中已有的逻辑门 4、算术操作符: Verilog中将reg视为无符号数,而integer视为有符号数。因此,进行有符号操作时使用integer,使用无符号操作时使用reg。 5、进位: 通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。如: Wire [3:0] A,B; Wire [4:0] C; Assign C=A+B; C的最高位用来存放进位。 6、关系运算符: 关系运算符:<,>,<=,>= 和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net还是integer。

VHDL实现16位全加器

[键入公司名称] [键入文档标题] [键入文档副标题] 姓名:托列吾别克?马杰尼 班级:电路与系统01班 学号:201221020141

[键入公司名称] 2013/11/24

基于VHDL的16位全加器的设计 1.1设计题目的内容及要求 i.i.i 目的: CMOS数字集成电路设计流程及数字集成电路自动化设计,包括功能验证、VHDL/Verlog建模、同步电路设计、异步数据获取、能耗与散热、信号完整性、物理设计、设计验证等技术 1.1.2内容: 主要实验内容是用0.18阿数字CMOS工艺,VHDL或Verlog设计- 个16位全加器,用Synthesis仿真工具验证功能,电路合成,及性能检测。 1.1.3主要测试参数及指标范围: 16位的全加器主要的设计指标是高于1GHz的频率,功耗,物理面积大小等参数。 1.2全加器的组成和原理分析 全加器是常用的组合逻辑模块中的一种,对全加器的分析和对组合逻辑电路的分析一样。组合逻辑电路的分析,就是找出给定电路输入和输出之间的逻辑关系,从而了解给定逻辑电路的逻辑功能。组合逻辑电路的分析方法通常采用代数法,一般按下列步骤进行: (1)根据所需要的功能,列出真值表。 (2)根据真值表,写出相应的逻辑函数表达式。 (3)根据真值表或逻辑函数表达式,画出相应的组合逻辑电路的逻辑图 (4)用VHDL编写程序在QUARTUS U上进行模拟,并分析结果的正确性。 1.3全加器简介

全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运 算就是全加运算,实现全加运算的电路称为全加器。它主要实现加法的运算, 其中分为并行全加器和串行全加器,所谓并行就是指向高位进位时是并行执行 的,而串行就是从低位到高位按顺序执行,为了提高运算,必须设法减小或消除由于进位信号逐级传递所消耗的时间,为了提高运算速度,制成了超前进位加法器,这是对全加器的一种创新[2]。 1.3.1半加器的基本原理 如果不考虑有来自低位的进位将两个1位二进制数相加,称为半加。实现 半加运算的电路称为半加器。 按照二进制加法运算规则可以列出如表2所示的半加器真值表,其中A、B 是两个加数,S是相加的和,CO是向咼位的进位。将S、CO和A、B的关系写成逻辑表达式则得到 S=A B+A B=A+B CO=AB 因此,半加器是由一个异或门和一个与门组成的,如图1所示。

Verilog可综合与不可综合语句汇总

1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:(1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。

8位加法器设计程序过程

实验8位加法器设计 一、实验目的 熟悉利用QuartusⅡ的图形编辑输入法设计简单组合电路,掌握层次化设计方法,并通过8位全加器的设计,进一步熟悉利用EDA软件进行数字系统设计的流程。 二、实验仪器与器材 计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。 三、实验内容 1. 基本命题 利用图形输入法设计一个一位半加器和全加器,再利用级联方法构成8位加法器。 2. 扩展命题 利用文本输入法设计4位并行进位加法器,再利用层次设计方法构成8位加法器。通过时序仿真,比较两种加法器的性能。 四、实验设计思路 按照如图2-1,2-2,2-3设计半加器、全加器、串行级联加法器 ①设计半加器 图2-1半加器设计图 ②设计全加器

图2-2全加加器设计图 ③设计串行级联8位加法器 图2-3串行级联8位加法器设计图 ④仿真波形图 对以上的串行级联加法器进行仿真。设置时钟频率为/1/10ns。每20ns对a,b输入口进行+2操作。所得结果见图2-8。由图可知延时大约为14ns。

图2-4串行级联加法器仿真波形图 对以上的串行级联加法器进行仿真。设置时钟频率为/2.0us。每10us对a,b输入口进行 +2操作。所得结果见图2-4。由图可知延时大约为10us。 五、实验要求 将实验原理、设计过程、编译仿真波形和分析结果、硬件测试实验结果写进实验报告。 六、实验思考题 (1)与单一设计文件比较,实现层次化设计应注意哪些问题? 答:实现层次化设计需要注意的是:假设B设计中引用A设计,那么需要将A 设计的工程文件放在B设计的工程文件中,另外,B设计的工程必须要以B的实体名称对应,不然仿真的时候会出错。 (2)比较图形编辑和文本编辑两种8位二进制加法器的性能,分析它们的主要异同点。以下是文本编辑的参考程序。 1) 4位二进制数加法器ADDER4B的VHDL描述 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER4B IS PORT ( CIN4 : IN STD_LOGIC; A4 : IN STD_LOGIC_VECTOR(3DOWNTO0);

FPGA VHDL4位全加器

《FPGA原理及应用》 实验报告书 (4) 用例化语句设计4位全加器题目 学院专业 姓名学号 指导教师 2015年 10-12月

1.实验目的 (1)进一步熟悉和掌握Qartus II的使用方法; (2)进一步掌握FPGA实验箱使用方法; (3)学习和掌握电路原理图的设计流程; (4)深化理解顶层设计的概念和构建电路的方法 2.实验内容 使用Qartus II的元件库,通过元件图的方式设计具有4位全加器功能的程序,并使用FPGA实验箱对程序进行硬件下载,验证。 3.实验条件 开发软件:Qartus II 8.0 实验设备:FPGA实验箱 拟用芯片:Altera EP3C55F484C8 4.实验设计 1)系统原理 多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。 四位全加器可对两个多位二进制数进行加法运算,同时产生进位。当两个二进制数相加时,较高位相加时必须加入较低位的进位项(Ci),以得到输出为和(S)和进位(C0)。 其中CIN表示输入进位位,COUT表示输出进位位,输入A和B分别表示加数和被加数。输出SUM=A+B+CIN,当SUM大于255时,COUT置‘1’。 图4-1 4位全加器原理图 2)程序代码

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY adder1 IS --1位全加器设计 PORT(a,b,cin:IN STD_LOGIC; s,cout:OUT STD_LOGIC); END adder1; ARCHITECTURE dataflow OF adder1 IS --用数据流方式设计1位全加器SIGNAL tmp:STD_LOGIC; --用tmp表示a⊕b BEGIN tmp<=a XOR b AFTER 10 ns; s<=tmp XOR cin AFTER 10 ns; cout<=(a AND b)OR(tmp AND cin) AFTER 20 ns; END dataflow; LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY adder4 IS --4位全加器设计 PORT(a,b:IN STD_LOGIC_VECTOR(3 DOWNTO 0); cin:IN STD_LOGIC; s:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); cout:OUT STD_LOGIC); END adder4;

基于VHDL 4位加法器的设计

实验三基于VHDL 4位加法器的设计 一、实验目的 1、进一步熟悉QUARTUS II软件的使用方法和VHDL输入的全过程。 2、进一步掌握实验系统的使用。 二、实验原理 图 2-1 半加器原理图 图 2-2 1位全加器原理图 图 2-3 4 位加法器原理图 4 位加法器(如图 2-3)是以 1 位全加器作为基本硬件,由 4 个 1 位全加器串行构成,1位全加器又可以由两个1位的半加器和一个或门连接而成(如图 2-2),而1位半加器可以由若干门电路组成(如图 2-1)。

三、实验内容 本次实验使用 Altera FPGA 的开发工具 Quartus Ⅱ,利用原理图输入设计方法设计一个 4位加法器,取实验板上的 8 位按键的高 4 位与低 4 位分别作为 4 位加数与被加数,其中 8 个 LED 取 5 位作为结果输出,LED2~LED5 作为 4 位相加之和的输出结果,LED1作为两数高 4 位相加的进位 (LED 亮,表示低电平“0”, LED 灭,表示高电平“1”) 四、实验步骤 1、打开QUARTUS II软件,新建一个工程。 2、建完工程之后,再新建一个VHDL File。新建一个VHDL文件的过程如下: 1)选择QUARTUS II软件中的File->New命令,出现New对话框。如图2-1所示。 图2-1 新建设计文件选择窗口 2)在New对话框(图2-1)中选择Design Files页下的VHDL File,点击OK按钮,打开VHDL编辑器对话框,如图2-2所示。

图2-2 VHDL编辑窗口 3、按照实验原理和自己的想法,在VHDL编辑窗口编写1位半加器的VHDL程序。如图 2-3所示。 图2-3 1位半加器VHDL程序 4、编写完半加器VHDL程序后,保存,文件名为h_adder.vhd(注意文件名要与实体名 保持一致),再将半加器文件设置为顶层文件,然后进行编译并仿真,对程序 的错误进行修改。 5、再用同样的方法进行或门的VHDL程序(or2a.vhd)输入、编译和仿真。 图2-4 或门VHDL程序 6、利用半加器与或门进行1位全加器的VHDL程序(f_adder.vhd)设计、编译与仿真。

EDA VHDL 4位全加器实验报告解析

姓名:车琳班级:通信1101班 学号:0121109320130 实验一用原理图输入法设计4位全加器 一、实验目的 1)熟悉利用Quartus II 的原理图输入方法设计简单组合电路; 2)掌握层次化设计的方法; 3)通过一个4位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。 二、实验内容 1)完成半加器、全加器和4位全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设计成一个硬件符号入库。键1、键2、键3(PIO0/1/2)分别接ain、bin、cin;发光管D2、D1(PIO9/8)分别接sum和cout。 2)建立一个更高的层次的原理图设计,利用以上获得的1位全加器构成的4位全加器,并完成编译、综合、适配、仿真和硬件测试。建议选择电路模式1:键2、键1输入4位加数:键4、键3输入4位被加数:数码6和数码5显示加和:D8显示进位cout。 三、实验仪器 1)计算机及操作系统; 2)QuartusII软件; 3)编程电缆。

四、实验原理 一个4位全加器可以由4个一位全加器 构成,加法器间的进位可以串行方式实现, 即将低位加法器的进位输出 cout 与相邻的 高位加法器的最低进位输入信号 cin 相接。 一个1位全加器可以参考教材介绍的方 法来完成。1位全加器示意图如图1所示。 其中,其中CI 为输入进位位,CO 为输出进位位,输入A 和B 分别为加数和被加数。S 为输出和,其功能可用布尔代数式表示为: i i i i o i i i ABC ABC ABC ABC C ABC C B A C B A C B A S +++=+++= 五、实验步骤 1、完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设计成一个硬件符号入库。键1、键 2、键3(PIO0/1/2)分别接ain 、bin 、cin ;发光管D2、D1(PIO9/8)分别接sum 和cout 。 2、建立一个更高层次的原理图设计,利用以上获得的1位全加器构成4位全加器,并完成编译、综合、适配、仿真、和硬件测试。建议选择电路模式1(附图F-2):键2、键1输入4位加数:键4、键3输入4位被加数:数码6和数码5显示加和:D8显示进位cout 。 1、一位全加器设计输入 1)创建文件。采用File\new 菜单,创建图形文件。 2)添加元件。采用菜单symbol\enter symbol ,在弹出的对话框中选中相应的库与元件,添加元件,构成一位全加器并保存。 2、一位全加器元件的创建 1)对上述文件编译综合仿真。 2)生成元件。 3)采用菜单FILE\CREATE SYMBOL 生成一位全加器元件。

verilog不可被综合的语句

verilog 不可综合语句总结汇总 2009-04-20 18:37 (1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。 (13)同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。 (14)避免在case语句的分支项中使用x值或z值。 不可综合verilog语句2009-04-14 19:33

VHDL四位全加器三种语言编程

四位全加器的三种VHDL语言描述方式: 一:数据流描述方式 libraryieee; use ieee.std_logic_1164.all; entity add1 is port(a,b,cin:instd_logic; s,cout:outstd_logic); end add1; architecture dataflow of add1 is begin s<=(a xor b) xorcin; cout<=((a xor b)and cin)or(a and b); end dataflow; 二:行为描述方式 libraryieee; use ieee.std_logic_1164.all; useieee.std_logic_unsigned.all; entity add22 is port(a,b,cin:instd_logic; s,co:outstd_logic); end add22; architecture dataflow of add22 is signaltmp:std_logic; begin process(a,b,cin) variable n:integer range 0 to 3; constants_vector: std_logic_vector(3 downto 0):="1010"; constantco_vector: std_logic_vector(3 downto 0):="1100"; begin n:=0; if a='1' then n:=n+1; end if; if b='1' then n:=n+1; end if; ifcin='1' then n:=n+1; end if; s<=s_vector(n) after 10 ;

FPGA中不可综合语句汇总

(1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。 (13)同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。 (14)避免在case语句的分支项中使用x值或z值。 不可综合verilog语句2009-04-1419:33 1、initial 只能在test bench中使用,不能综合。(我用ISE9.1综合时,有的简单的initial也可以综合,不知道为什么) 2、events event在同步test bench时更有用,不能综合。 3、real 不支持real数据类型的综合。 4、time 不支持time数据类型的综合。

- 分别使用原理图和VHDL语言输入方法设计8位全加器分解

- VHDL实现16位全加器

- 一位加法器VHDL程序

- 基于VHDL 4位加法器的设计

- 数字逻辑电路课程设计_4bit模9加法器_VHDL实现(含完整

- VHDL实现16位全加器

- VHDL实现16位全加器.doc

- VHDL实现16位全加器

- 四位全加器的VHDL与VerilogHDL完成

- EDA实验报告(四位全加器的实现)

- 元件例化语句实现4位全加器VHDL源程序

- VHDL编写一位全加器参考程序

- VHDL8位加法器设计

- 二位全加器(VHDL)

- EDA VHDL 4位全加器实验报告

- 分别使用原理图和VHDL语言输入方法设计8位全加器

- EDA—VHDL的四位全加器

- FPGA设计实例 四位加法器(含VHDL源程序)

- VHDL四位全加器三种语言编程

- 四位全加器的VHDLVerilogHDL实现