DSP学习

DSP之时钟学习

先说软件设置:

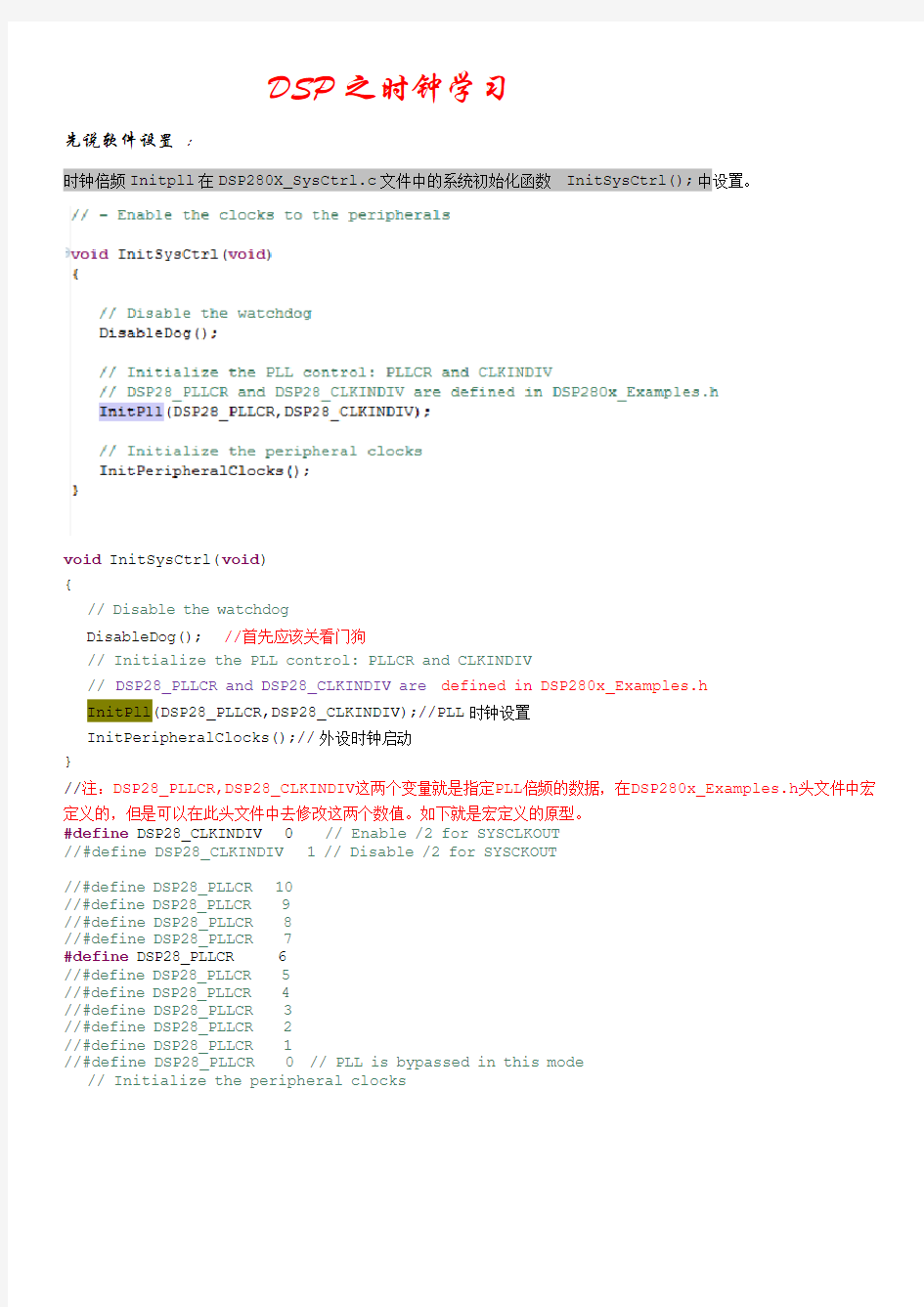

时钟倍频Initpll在DSP280X_SysCtrl.c文件中的系统初始化函数 InitSysCtrl();中设置。

void InitSysCtrl(void)

{

// Disable the watchdog

DisableDog(); //首先应该关看门狗

// Initialize the PLL control: PLLCR and CLKINDIV

// DSP28_PLLCR and DSP28_CLKINDIV are defined in DSP280x_Examples.h

InitPll(DSP28_PLLCR,DSP28_CLKINDIV);//PLL时钟设置

InitPeripheralClocks();//外设时钟启动

}

//注:DSP28_PLLCR,DSP28_CLKINDIV这两个变量就是指定PLL倍频的数据,在DSP280x_Examples.h头文件中宏定义的,但是可以在此头文件中去修改这两个数值。如下就是宏定义的原型。

#define DSP28_CLKINDIV 0 // Enable /2 for SYSCLKOUT

//#define DSP28_CLKINDIV 1 // Disable /2 for SYSCKOUT

//#define DSP28_PLLCR 10

//#define DSP28_PLLCR 9

//#define DSP28_PLLCR 8

//#define DSP28_PLLCR 7

#define DSP28_PLLCR 6

//#define DSP28_PLLCR 5

//#define DSP28_PLLCR 4

//#define DSP28_PLLCR 3

//#define DSP28_PLLCR 2

//#define DSP28_PLLCR 1

//#define DSP28_PLLCR 0 // PLL is bypassed in this mode

// Initialize the peripheral clocks

进出CPU时钟CLKIN可以是PLL关闭可以是PLL旁路,还可以是PLL使能

注:

·晶振操作:

此模式允许使用外部为器件提供时基。晶体连接到X1/X2 引脚,XCLKIN 连接到低电平。

·外部时钟源操作:

此模式允许绕过内部振荡器。器件时钟根据引脚上的外部时钟源输入生成。必须将X1 连接到低电平并让X2 悬空。在这种情况下,外部振荡器时钟连接到XCLKIN 引脚,允许使用3.3V 时钟源。

允许使用X1 和X2 引脚将晶体连接到280x 器件。如果未使用晶体,则可以将外部振荡器直接连接到XCLKIN 引脚,X2 引脚保留悬空,X1 连接到低电平。请参阅

TMS320F2808、TMS320F2806、TMS320F2801、UCD9501 数字信号处理器数据手册(文献编号SPRS230) 1:来自X1,X2或者XCLKIN的时钟可以通过控制寄存器PLL 状态寄存器(PLLSTS)来控制是否需要经过PLL倍频,

当OSCOFF=0时来自X1,X2或者XCLKIN的时钟送至PLL,当OSCOFF=1时X1,X2或者XCLKIN的时钟不送PLL 2:a、简单的说就是若OSCOFF=1是关闭PLL,SYSCLKOUT直接就等于外部晶振或者晶体来的时钟OSCCLK 或者是OSCCLK/2,具体是OSCCLK/2还是OSCCLK还要通过设置寄存器PLLSTS[CLKINDIV]位,如下图:

b、OSCOFF=0且PLLOFF=0时就是打开PLL,通过设置PLLCR寄存器来控制倍频的倍数,控制SYSCLKOUT 的大小,见图PLLCR的值和CLKIN(SYSCLKOUT)对应关系:(还要设置PLLSTS[CLKINDIV]位)

c、当OSCOFF=0且PLLOFF=1时就是PLL作为旁路使用,PLL 关闭设置了PLLOFF 位时,PLL 模块应保持断电。器件必须处于PLL 旁路模式(PLLCR = 0x0000),然后才能将1 写入PLLOFF。当PLL 关闭(PLLOFF = 1) 时,不要为PLLCR 写入非零值。当PLLOFF = 1时,STANDBY 和HALT 低功率模式将如预期正常工作。在从HALT 或STANDBY 唤醒之后,PLL 模块将继续断电。

例:DSP280x_Examples.h头文件中

/*-----------------------------------------------------------------------------

Specify the PLL control register (PLLCR) and clock in divide (CLKINDIV) value.

if CLKINDIV = 0: SYSCLKOUT = (OSCCLK * PLLCR)/2

if CLKINDIV = 1: SYSCLKOUT = (OSCCLK * PLLCR)

-----------------------------------------------------------------------------*/

#define DSP28_CLKINDIV 0 // Enable /2 for SYSCLKOUT

//#define DSP28_CLKINDIV 1 // Disable /2 for SYSCKOUT 设置输出的时钟二分频与否 0表示二分频 1表示不二分频。

//#define DSP28_PLLCR 10

//#define DSP28_PLLCR 9

#define DSP28_PLLCR 6

//#define DSP28_PLLCR 5

//#define DSP28_PLLCR 4

//#define DSP28_PLLCR 3

//#define DSP28_PLLCR 2

//#define DSP28_PLLCR 1

//#define DSP28_PLLCR 0 // PLL is bypassed in this mode//旁路模式中使用

void InitPll(Uint16 val, Uint16 clkindiv) 函数也在DSP280X_SysCtrl.c中,

寄存器设置

Figure 3-3. Peripheral Clock Control 0 Register (PCLKCR0) 图3-2./3-3. 外设时钟控制寄存器0 (PCLKCR0/1)

图3-5. 高速外设时钟预分频器(HISPCP) 寄存器

// HISPCP/LOSPCP prescale register settings, normally it will be set to default values SysCtrlRegs.HISPCP.all = 0x001 ;//高速时钟HISPCP = SYSCLKOUT/2

SysCtrlRegs.LOSPCP.all = 0x002;//低速时钟HISPCP = SYSCLKOUT/4

// XCLKOUT to SYSCLKOUT ratio. By default XCLKOUT = 1/2 SYSCLKOUT

SysCtrlRegs.XCLK.bit.XCLKOUTDIV=10 ;

DSP之GPIO

1GPIO Port A MUX 1 (GPAMUX1) Register 引脚功能控制寄存器:GPAMUX1 控制0-15号引脚

GPAMUX2 控制16-31号引脚

注:GPIO复用功能寄存器MUX可以根据设置相应的位来达到改变GPIO功能的作用其中两位控制一个GPIO

GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 0; // GPIO6 = GPIO6

2Figure 4-13. GPIO Port A Direction (GPADIR) Register

方向控制器GPADIR 控制31-0

GPBDIR控制34-32

注:方向寄存器是控制GPIO的方向的

寄存器的每一位控制一个GPIO

对其写0代表GPIO输入,写1代表GPIO输出

GpioCtrlRegs.GPADIR.bit.GPIO17 = 1; // GPIO17 = output

内部上拉控制寄存器GPAPUD 控制31-0引脚

GPBPUD 控制32-34引脚

注:内部上拉控制寄存器是用来开启/关闭内部上拉

GpioCtrlRegs.GPAPUD.bit.GPIO8 = 0; // Enable pullup on GPIO8

状态寄存器GPADAT控制GPIO31-0

状态寄存器GPBDAT 控制32-34

注:DAT状态寄存器可以用来读取GPIO的值也可用来对GPIO进行赋值

输入,则不能驱动端口输出0。

Reading a 0 indicates that the state of the pin is currently low, irrespective of the mode the pin is configured for.(读取0状态操作)

Reading a 1 indicates that the state of the pin is currently high irrespective of the mode the pin is configured for. (读取1状态操作)

GpioDataRegs.GPADDAT.all = 0xFFFDFFFF //GPIO16输出低电平

GPIO端口置位,清零,反转控制寄存器GPASET, GPACLEAR, GPATOGGLE 控制31-0引脚

注:对置位,清零,反转操作时对寄存器写0被忽略不计,只有当对其写1是才起作用,比如对某一位GPIO的GPACLEAR写1,则表示对此端口进行清零操作。

同理GPBSET, GPBCLEAR, GPBTOGGLE则是对32-34GPIO操作,

例:GpioDataRegs.GPASET.bit.GPIO12 = 1; //GPIO置1

XINT1, XINT2, XNMI中断源控制寄存器

注:此处只拿XINT1作为参考

想把哪个GPIO作为XINT1的中断源只需要设置对应位寄存器就OK

Register Field Descriptions 低功耗唤醒设置寄存器

很多工程师在对按键去抖动都会采用软件延时的方法,今天介绍下关于Piccolo DSP GPIO所具有的硬件去抖功能.

信号首先同步于系统时钟,在输入到内核改变之前要经过一定周期个数的量化,这种方式可以滤除噪声。量化窗口输入的结构示意图如图所示。

由图可知,外部的管脚输入信号经过一个量化窗口到达DSP内核。量化窗口的时间宽度取决于采样间隔和采样个数。采样间隔由GPxCTRL寄存器决定,采样个数由寄存器GPxQSELn决定。

如果QUxLPRDn = 0,采样间隔为一个系统周期整数倍。如果QUxLPRDn = N (N≠0),采样周期为系统周期的2N倍。如表所示

采样个数可以配置位三个或六个。通过寄存器GPAQSEL1、GPAQSEL2、GPBQSEL1来配置,当外部管脚电平状态发生变化时,量化窗口检测到三个或六个周期内相同的状态时,才把此次状态改变传送到内核,否则会当成杂波滤除。

量化窗口的宽度与采样周期和采样个数有关,当采样周期和采样个数确定之后,量化窗口的宽度就确定了。量化窗口与采样周期及采样个数的关系如表所示。

现举例说明量化窗口的用法及效果。假如某个GPIO引脚为数字输入,量化模式为6个采样周期量化,采样周期寄存器中QUxLPRDn值为一,则采样周期为两个系统时钟周期宽度,量化输入的结果如图所示。

注:值得注意的是在DEBUG 的时候必须,当触发中断的时候不能用单步执行程序,因为由于DSP有端口硬件消抖的功能,输入的状态必须和系统时钟一致才能触发外中断的发生,应该用RUN直接执行程序。

DSP之外部中断

PIE

CPU有1各部可屏蔽中断NMI。

14个可屏蔽中断INT1---INT14。

2812内有很多外设每一个外设可以产生一个或多个中断、CPU没有能力同时处理所有中断请求专门设计一个PIE外设中断控制器。

PIE支持96个中断12组每组8个中断。

而且每组都被反馈到CPU内核12条中短线的某一条上面。

其实我们作用了96中断的45个。

CPU是3级中断机制外设级PIE 级CPU级。对于一个具体的外设中断请求,一个不许可CPU 不会执行该中断。

当某个外设中断事件发生了,这个外设某个寄存器和该中断标志置 1

如果该中断的中断使能位被置1 外设就会向PIE发送中断请求,否则不会往PIE发送中断请求。不管什么情况下外设中断标志寄存器中断中断标志必须手动清除

例如

每一组PIE 都有个标志寄存器PIEIFRx 使能寄存器PIEIERx 还有个相应寄存器ACK

一组同时一个中断被响应因为PIEACK 寄存器12位对应INT1 --12

有中断PIEACK对应位置 1 等待手动清除(标志寄存器自动清除)才能响应同组下一个中断(如果中断请求还在)。

DINT; //禁止中断在设置某些寄存器的时候

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

EALLOW; // This is needed to write to EALLOW protected registers 写自由

EDIS; // This is needed to disable write to EALLOW protected registers 禁止写某些特殊寄存器

所以简单点说,就是有些寄存器受到写保护的,你要写它,就首先要用EALLOW禁止写保护.写完了之后别忘

了用EDIS再是能写保护.

CPU级也有IFR IER CPU接到中断请求暂停现在执行的程序清除IER IFR EALLOW 、INTM置位就不响应其他中断

1、PieVectTable.T1PINT = &eva_timer1_isr;

2、// Enable PIE group 2 interrupt 4 for T1PINT

PieCtrl.PIEIER2.all = M_INT4;

3、IER |= (M_INT2 | M_INT3 | M_INT4 | M_INT5);

4、interrupt void eva_timer1_isr(void)

8音度手把手教你调音玩转dsp

8 音度手把手教你调音 玩转DSP 当前浏览器不支持播放音乐或语音,请在微信或其他浏览器中播放湘妃怨纯音乐- 中国古典音乐历朝黄金年鉴8 音度教你如何使用均衡器来获得更好的声音表现、如何利用好均衡器调音、图形均衡器怎么用,对汽车音响调音还不够熟悉的小伙伴可以看下哦!包你学会之后对自己调音技术自信满满,提升客户对你的满意度!如何使用均衡器来获得更好的声音表现下面来看看均衡器分段后的每个部分的作用:1.20Hz--60Hz 部分这一段提升能给音乐强有力的感觉,给人很响的感觉,如雷声。是音乐中强劲有力的感觉,如果这个频段的量感太少,丰润澎湃的感觉一定没有;而且会导致中高频、高频的突出,使得声音失去平衡感,不耐久听。如果提升过高,则又会混浊不清,造成清晰度不佳,特别是低频响应差和低频过重的音响设备。 2. 60Hz--250Hz 部分这段是音乐的低频结构,它们包含了节奏部分的基础音,包括基音、节奏音的主音。它和高中音的比例构成了音色结构的平衡特性。提升这一段可使声音丰满,过度提升会发出隆

隆声。衰减这两段会使声音单薄。 3. 250Hz--2KHz 部分这段包含了大多数乐器的低频谐波,如果提升过多会使声音像电话里的声音。如把600Hz 和1kHz 过度提升会使声音像喇叭的声音。如把3kHz 提升过多会掩蔽说话的识别音,即口齿不清,并使唇音“ mbv”难以分辨。如把1kHz 和3kHz 过分提升会使声音具有金属感。由于人耳对这一频段比较敏感,通常不调节这一段,过分提升这一段会使听觉疲劳。 4. 2KHz--4kHz 部分这段频率属中频,如果提升得过高会掩盖说话的识别音,尤其是3kHz 提升过高,会引起听觉疲劳。5. 4kHz--5KHz 部分这是具有临场感的频段,它影响语言和乐器等声音的清晰度。提升这一频段,使人感觉声源与听者的距离显得稍近了一些;衰减5kHz ,就会使声音的距离感变远;如果在5kHz 左右提出升6dB ,则会使整个混合声音的声功率提升3dB。 6. 6kHz--16kHz 部分这一频段控制着音色的明亮度,宏亮度和清晰度。一般来说提升这几段使声音宏亮,但不清晰,不可能会引起齿音过重,衰减时声音变得清晰,但声音不宏

03 第三讲 数字电路基础知识--力天手把手教你学单片机之入门篇

手把手教你学51单片机 ——之MCS-51入门篇 主讲: 尹延辉 策划:张勇 开发板:LT-Super51 QQ群:31646346 网址:https://www.wendangku.net/doc/741154794.html, E-Mail:litianmcu@https://www.wendangku.net/doc/741154794.html, litianmcu@https://www.wendangku.net/doc/741154794.html,

入门篇第三讲——数字电路基础知识?本讲内容提要 数字量和模拟量 数制和码制 算术运算和逻辑运算 数字芯片 常用数字芯片简介 可编程逻辑器件 存储器 学习板上扩展IO口 的实现

——数字量和模拟量 ?数字量和模拟量定义 模拟量:随时间连续变化的电压或电流信号称之为模拟量 数字量:随时间离散变化的量称之为数字量 ?数字量的实质为加入判决门限的模拟量

——数字电路’0’与’1’的定义?数字电路’0’与’1’的定义 TTL电平:电压+5V代表’1’,电压0代表’0’ LVTTL:+3.3V~’1’,0~’0’ RS232:-15V~’1’,+15V~’0’ LVDS:2根线上电压差的正负表示’1’或’0’

——数制和码制 ?数制的定义 计数过程中一位数字通常是不够用的,多位数码中每一位的构成方法及从低位向高位进位规则称为数制。 N进制数的通俗定义:逢N进1 ?十进制:逢十进一 ?十六进制:逢十六进一 ?二进制:逢二进一 ?常用数制 十进制、二进制、十六进制 ?人类有十个指头,所以习惯采用十进制 ?计算机只能识别0和1,采用二进制 ?为了计算机学中的数据书写方便,采用十六进制

——数制转换详解 ?数制间的转换 二-十转换 十-二转换 二-十六转换 十六-二转换 ?位与字节的概念: 位(bit):简写为b,表示二进制数的一位。 字节(Byte):简写为B,8位为一字节。 ?数制转换工具: Windows自带的计算器

音度手把手教你调音玩转dsp

音度手把手教你调音玩转 d s p Newly compiled on November 23, 2020

8音度手把手教你调音 玩转DSP 当前浏览器不支持播放音乐或语音,请在微信或其他浏览器中播放湘妃怨纯音乐 - 中国古典音乐历朝黄金年鉴 8音度教你如何使用均衡器来获得更好的声音表现、如何利用好均衡器调音、图形均衡器怎么用,对汽车音响调音还不够熟悉的小伙伴可以看下哦!包你学会之后对自己调音技术自信满满,提升客户对你的满意度! 如何使用均衡器来获得更好的声音表现 下面来看看均衡器分段后的每个部分的作用: 部分 这一段提升能给音乐强有力的感觉,给人很响的感觉,如雷声。是音乐中强劲有力的感觉,如果这个频段的量感太少,丰润澎湃的感觉一定没有;而且会导致中高频、高频的突出,使得声音失去平衡感,不耐久听。如果提升过高,则又会混浊不清,造成清晰度不佳,特别是低频响应差和低频过重的音响设备。 2. 60Hz--250Hz部分 这段是音乐的低频结构,它们包含了节奏部分的基础音,包括基音、节奏音的主音。它和高中音的比例构成了音色结构的平衡特性。提升这一段可使声音丰满,过度提升会发出隆隆声。衰减这两段会使声音单薄。 3.

250Hz--2KHz部分 这段包含了大多数乐器的低频谐波,如果提升过多会使声音像电话里的声音。如把600Hz和1kHz过度提升会使声音像喇叭的声音。如把3kHz提升过多会掩蔽说话的识别音,即口齿不清,并使唇音“mbv”难以分辨。如把1kHz和3kHz过分提升会使声音具有金属感。由于人耳对这一频段比较敏感,通常不调节这一段,过分提升这一段会使听觉疲劳。 4. 2KHz--4kHz部分这段频率属中频,如果提升得过高会掩盖说话的识别音,尤其是3kHz提升过高,会引起听觉疲劳。 5. 4kHz--5KHz部分 这是具有临场感的频段,它影响语言和乐器等声音的清晰度。提升这一频段,使人感觉声源与听者的距离显得稍近了一些;衰减5kHz,就会使声音的距离感变远;如果在5kHz左右提出升6dB,则会使整个混合声音的声功率提升3dB。 6. 6kHz--16kHz部分 这一频段控制着音色的明亮度,宏亮度和清晰度。一般来说提升这几段使声音宏亮,但不清晰,不可能会引起齿音过重,衰减时声音变得清晰,但声音不宏亮。均衡器上也可以按照听门极限的曲线图来设置,这样让耳朵能最容易的感觉到声音,这样最自然

音度手把手教你调音玩转dsp

8音度手把手教你调音 玩转DSP 当前浏览器不支持播放音乐或语音,请在微信或其他浏览器中播放湘妃怨纯音乐 - 中国古典音乐历 朝黄金年鉴 8音度教你如何使用均衡器来获得更好的 声音表现、如何利用好均衡器调音、图形均衡器怎么用,对汽车音响调音还不够熟悉的小伙伴可以看下哦!包你学会之后对自己调音技术自信满满,提升客户对你的满意度! 如何使用均衡器来获得更好的声音表现 下面来看看均衡器分段后的每个部分的作用: 1.20Hz--60Hz部分 这一段提升能给音乐强有力的感觉,给人很响的感觉,如雷声。是音乐中强劲有力的感觉,如果这个频段的量感太少,丰润澎湃的感觉一定没有;而且会导致中高频、高频的突出,使得声音失去平衡感,不耐久听。如果提升过高,则又会混浊不清,造成清晰度不佳,特别是低频响应差和低频过重的音响设备。 2. 60Hz--250Hz部分 这段是音乐的低频结构,它们包含了节奏部分的基础音,包括基音、节奏音的主音。它和高中音的比例构成了音色结构的平衡特性。提升这一段可使声音丰满,过度提升会发出隆隆声。衰减这两段会使声音单薄。

3. 250Hz--2KHz部分 这段包含了大多数乐器的低频谐波,如果提升过多会使声音像电话里的声音。如把600Hz和1kHz过度提升会使声音像喇叭的声音。如把3kHz提升过多会掩蔽说话的识别音,即口齿不清,并使唇音“mbv”难以分辨。如把1kHz和3kHz 过分提升会使声音具有金属感。由于人耳对这一频段比较敏感,通常不调节这一段,过分提升这一段会使听觉疲劳。4. 2KHz--4kHz部分这段频率属中频,如果提升得过高会掩盖说话的识别音,尤其是3kHz提升过高,会引起听觉疲劳。 5. 4kHz--5KHz部分 这是具有临场感的频段,它影响语言和乐器等声音的清晰度。提升这一频段,使人感觉声源与听者的距离显得稍近了一些;衰减5kHz,就会使声音的距离感变远;如果在5kHz 左右提出升6dB,则会使整个混合声音的声功率提升3dB。 6. 6kHz--16kHz部分 这一频段控制着音色的明亮度,宏亮度和清晰度。一般来说提升这几段使声音宏亮,但不清晰,不可能会引起齿音过重,衰减时声音变得清晰,但声音不宏亮。均衡器上也可以按照

手把手教你学DSP-2812

第一章如何开始DSP的学习和开发 DSP是Digital Signal Processing的缩写,同时也是Digital Signal Processor的缩写。它采用哈佛结构即数据空间和存储空间是分开的,通过独立的数据总线在程序空间和数据空间同时访问。DSP的优势是其强大的数据处理能力和较高的运行速度,所以多用于数据处理,例如加密/解密、调制/解调等。值得一提的是,TI公司的C2000系列的DSP除了具有强大的运算能力外,也是控制领域的佼佼者。 MCU:采用冯诺依曼结构,数据空间和存储空间共用一个存储空间,通过一组总线(地址总线和数据总线)连接到CPU。MCU的价格便宜。 ARM是Adnanced RISC(精简指令集)Machines的缩写,是面向低预算市场的RISC微处理器。它具有较强的事务管理功能,适合用来跑跑界面、操作系统等,其优势主体体现在控制方面,像手持设备90%左右的市场份额均被其占有。 FPGA是Field Programmable Gate Array(现场可编程逻辑门阵列),它是在PAL、GAL、PLD等可编程器件的基础上进一步发展的产物,是专用集成电路中集成度最高的一种。FPGA适合用来开发数字电路,但是FPGA的价格通常比较昂贵,这是限制其应用的原因。 TMS320C2000系列,面向数字控制、运动控制领域,主要包括:TMS320C24xx/TSM320F24xx,TMS320C28xx/TMS320F28xx等。使用较多的定点芯片是TMS320F2407、TMS320F2812、TMS320F2808和浮点芯片TMS320F2812(应用最广泛)。 TMS320C5000系列,面向低功耗、手持设备、无线终端应用领域。 TMS320C6000系列,面向高性能、多功能、复杂应用领域。 DSP开发的软件环境:CCS(Code Composer Studio)。硬件环境是仿真器和开发板或目标板。 通常的上电和下电顺序: 上电顺序:先连电源插座,后连仿真器的接口连接到计算机上。 下电顺序:先将仿真器USB口从计算机的USB口拔下,再将电源拔出。

DSP简单例程

不知道你学过单片机没有。 37个寄存器是R1-R16.(当然,里面有很多是分几个模式的,所以总共有37个) 类似于单片机的R0-R7. GPXCON,GPXDAT等等是另外的寄存器,应该叫,特殊功能寄存器,类似于单片机的P0,P1,TCON,等等。 GPXCON:是X管脚的控制寄存器,控制它们的模式,比如输出模式,输入模式……GPXDAT:是X管脚的数据寄存器,存储它们的数据, 比如: 在输出模式中,想在X管脚输出什么数据,就在这个寄存器里写入什么数据, 在输入模式中,这个寄存器中存储的就是外部输入的数据。 手把手教你找GPIO寄存器IODIR 定义 手把手教你找寄存器定义 一直就很纳闷,没有一个向c8051f410.h的头文件定义特殊功能寄存器,找不见定义,使用起来就无从下手,心里总是不舒坦; 从网上看了一些帖子,都说就是在头文件里(我也是这么认为的,肯定要有定义的,不然无法调用) StartUp{ ……….. ………. GEL_MapAdd(0x3400u,2,0x0400u,1,1); /* GPIO 1KW */ ……….. } 这段映射0x3400u 为GPIO空间,其实只是表示这段i/o空间可读可写; 下面是我一步一步地追踪,这些都是要用到的宏定义; #define PREG16(addr) (*(volatile ioport Uint16*)(addr)) 从一个ioport Uint16*类型的地址中取出地址内容,就是IODIR寄存器的值了 #define _GPIO_IODIR_ADDR (0x3400u) //定义了IO地址常量 #define _GPIO_IODIR PREG16(_GPIO_IODIR_ADDR) //得到寄存器的地址 #define _IODIR _GPIO_IODIR 定义了 _IODIR 常量 #define GPIO_ADDR(Reg) _GPIO_##Reg##_ADDR 两个变量合并 #define _PREG_SET(PregAddr, Val) PREG16(PregAddr) = (Uint16)Val #define GPIO_RSET(Reg,Val) _PREG_SET(GPIO_ADDR(##Reg),Val)

如何学习DSP

如何学习DSP 在上完一学期的DSP应用与技术之后,我对于DSP这个名词依旧似懂非懂,为了彻底了解其含义,我只好从网上搜了些资料,原来,DSP就是数字信号处理或者数字信号处理器的英文简称,也就是用数值计算的方式对信号进行加工的理论和技术。 那么,这样一来,我就清楚多了,毕竟上学期有上数字信号处理这门课,我想在它的基础上,DSP学起来就容易些了。 通俗来讲,数字信号处理是研究用数字方法对信号进行分析、变换、滤波、检测、调制、解调以及快速算法的一门技术学科。但很多人认为:数字信号处理主要是研究有关数字滤波技术、离散变换快速算法和谱分析方法。当然,这些技术在各个领域都有所发展,而且应用也会越来越广。 在学DSP的过程中,我遇到了一个难题,就是自己学会编程,离散傅里叶变换的编程方法和数字滤波器的实现问题着实让人头疼,不仅仅这样,有时候就连听老师讲例题都会有点丈二和尚摸不着头脑的感觉,其实在课堂上,老师把讲课的速度放得很慢,为的就是让我们能听懂,有时候一个语句要反复解释好几遍,可能是大家对于编程基础还是不太扎实,所以现在自己编写很费力,完全不知道从哪里入手。 我还记得第一次上DSP课时,把书本打开,前一章都是些概括性的话语,还有一些简短的汇编语言,看起来不算难,可是当第二堂课老师通过例子来教学时,我都懵了,书本上的程序可能一个就十几

行,可是在放映的ppt 上一个例子不下四五十行,别说是理解了,就连看完都很费力,不仅仅是大骨架的构建,一个程序里往往包括好几个子程序,稍一不留神,就不知道老师从哪跳到哪了。 为了跟上老师的节奏,我每次都会事先看书预习,以免上课犯迷糊,本来到做实验的时候是一个很好的学习机会,毕竟动手实践往往比理论来的更真切,可是不幸运的是,实验室的实验器材大部分都坏了,就这样,很多理论都证明不了了。 从学习DSP中,我领悟到了一些东西,DSP说难不难,说简单也不简单,关键是要看你用什么样的心态去对待它,其实,不管是学习哪方面的知识,你都要抱着一份认真的态度,努力去学习它,这样才会有收获。 在这门课学习完后,让我欣慰的是我的翻译水平提高了很多,我会试着从程序里找到切入点,仔细钻研不懂的语句,联系前后可以得到理解,当然设计能力确实还是有待提高,自己水平有限,如果要我用程序来设计一个处理器或者电子产品,我觉得我需要很多时间和帮助。 所以,我觉得如果想真正掌握好这门技术,不如去报个培训班,从课堂上听到的知识毕竟还是有限的,既然有心要学好,就应该投入精力,首先是将书本啃烂,然后去跟辅导班老师的进度,珍惜和老师同学相处的时间,有什么不懂的可以向老师提出来,也可以同学之间相互交流,下完课后将自己学到的知识梳理一遍,做到课前预习,课后复习,辅导的意义只是在于解决你所觉得棘手的问题,不会像小学

【音响知识】特伦诗手把手教你调音 玩转DSP

【音响知识】特伦诗手把手教你调音玩转DSP 特伦诗教你如何使用均衡器来获得更好的声音表现、如何利用好均衡器调音、图形均衡器怎么用,对汽车音响调音还不够熟悉的小伙伴可以看下哦!包你学会之后对自己调音技术自信满满,提升客户对你的满意度! 如何使用均衡器来获得更好的声音表现 下面来看看均衡器分段后的每个部分的作用: 1.20Hz--60Hz部分 这一段提升能给音乐强有力的感觉,给人很响的感觉,如雷声。是音乐中强劲有力的感觉,如果这个频段的量感太少,丰润澎湃的感觉一定没有;而且会导致中高频、高频的突出,使得声音失去平衡感,不耐久听。如果提升过高,则又会混浊不清,造成清晰度不佳,特别是低频响应差和低频过重的音响设备。 2. 60Hz--250Hz部分 这段是音乐的低频结构,它们包含了节奏部分的基础音,包括基音、节奏音的主音。它和高中音的比例构成了音色结构的平衡特性。提升这一段可使声音丰满,过度提升会发出隆隆声。衰减这两段会使声音单薄。 3. 250Hz--2KHz部分 这段包含了大多数乐器的低频谐波,如果提升过多会使声音

像电话里的声音。如把600Hz和1kHz过度提升会使声音像喇叭的声音。如把3kHz提升过多会掩蔽说话的识别音,即口齿不清,并使唇音“mbv”难以分辨。如把1kHz和3kHz过分提升会使声音具有金属感。由于人耳对这一频段比较敏感,通常不调节这一段,过分提升这一段会使听觉疲劳。4. 2KHz--4kHz部分 这段频率属中频,如果提升得过高会掩盖说话的识别音,尤其是3kHz提升过高,会引起听觉疲劳。 5. 4kHz--5KHz部分 这是具有临场感的频段,它影响语言和乐器等声音的清晰度。提升这一频段,使人感觉声源与听者的距离显得稍近了一些;衰减5kHz,就会使声音的距离感变远;如果在5kHz 左右提出升6dB,则会使整个混合声音的声功率提升3dB。 6. 6kHz--16kHz部分 这一频段控制着音色的明亮度,宏亮度和清晰度。一般来说提升这几段使声音宏亮,但不清晰,不可能会引起齿音过重,衰减时声音变得清晰,但声音不宏亮。均衡器上也可以按照听门极限的曲线图来设置,这样让耳朵能最容易的感觉到声音,这样最自然最好!这样让低频和高频能够很自然的被耳朵感受到,也就是说最佳的EQ设置应该和该曲线图吻合。在对均衡器进行调节的时候最好能结合等响曲线和耳机的 频响曲线。例如,如果耳机的频响曲线是理想的,也就是一

音度手把手教你调音玩转ds

8音度手把手教你调音 玩转DSP 当前浏览器不支持播放音乐或语音,请在微信或其他浏览器中播放 湘妃怨纯音乐 - 中国古典音乐历朝黄金年鉴 8音度教你如何使用均衡器来获得更好的声音表现、如何利用好均衡器调音、图形均衡器怎么用,对汽车音响调音还不够熟悉的小伙伴可以看下哦!包你学会之后对自己调音技术自信满满,提升客户对你的满意度! 如何使用均衡器来获得更好的声音表现 下面来看看均衡器分段后的每个部分的作用: 部分 这一段提升能给音乐强有力的感觉,给人很响的感觉,如雷声。是音乐中强劲有力的感觉,如果这个频段的量感太少,丰润澎湃的感觉一定没有;而且会导致中高频、高频的突出,使得声音失去平衡感,不耐久听。如果提升过高,则又会混浊不清,造成清晰度不佳,特别是低频响应差和低频过重的音响设备。 2. 60Hz--250Hz部分 这段是音乐的低频结构,它们包含了节奏部分的基础音,包括基音、节奏音的主音。它和高中音的比例构成了音色结构的平衡特性。提升这一段可使声音丰满,过度提升会发出隆隆声。衰减这两段会使声音单薄。

3. 250Hz--2KHz部分 这段包含了大多数乐器的低频谐波,如果提升过多会使声音像电话里的声音。如把600Hz和1kHz过度提升会使声音像喇叭的声音。如把3kHz提升过多会掩蔽说话的识别音,即口齿不清,并使唇音“mbv”难以分辨。如把1kHz和3kHz过分提升会使声音具有金属感。由于人耳对这一频段比较敏感,通常不调节这一段,过分提升这一段会使听觉疲劳。 4. 2KHz--4kHz部分这段频率属中频,如果提升得过高会掩盖说话的识别音,尤其是3kHz提升过高,会引起听觉疲劳。 5. 4kHz--5KHz部分 这是具有临场感的频段,它影响语言和乐器等声音的清晰度。提升这一频段,使人感觉声源与听者的距离显得稍近了一些;衰减5kHz,就会使声音的距离感变远;如果在5kHz左右提出升6dB,则会使整个混合声音的声功率提升3dB。 6. 6kHz--16kHz部分 这一频段控制着音色的明亮度,宏亮度和清晰度。一般来说提升这几段使声音宏

手把手教你建立C2000 F28027工程

28027建立工程详细方法 Writened by xuan2014-03-22之前因为要做一个小项目--用DSP控制步进电机,看起来感觉很简单,但以前没用过C2000的DSP,只用过5509A,正好手上有块F28027的板子,所以琢磨着用这块板来试试。 和很多新手一样,刚开始我也是无从下手,于是花了一个多礼拜在网上查找资料,把TI 的在线支持社区也差不多翻了个底朝天。 功夫不负有心人!C2000LaunchPad终于能够闪起来了!所以也想把自己的经验分享出来,让更多的新手少走一些弯路。 下面是建立工程的详细步骤: 一.准备工作 https://www.wendangku.net/doc/741154794.html,S sofeware。我用的是5.5,比较新 2.ControlSuite。这个软件可以在TI wiki里面搜索下载到,里面包含了C2000系列所有的 例 程

二.建立工程,设置相应参数: 1.新建工程目录 配置好后点击Finish。 工程配置需和以上完全一致,若有一处不同,后面编译和down进板子里面时就可能出现各种错误,切记。

建立好后的空白工程: 2.工程右键--properties,我们要建立的是Debug版工程,所以需要delete Release版的配置

3.General配置:因为是Debug工程,所以CMD文件选择28027_RAM_lnk.cmd 4.配置Include Option项,将control suite中F28027的include和src文件夹拷贝到当前工程目录下并添加进来:

5.配置Debug--F28027Flash Settings项,选择Load RAM Only。如果要down入Flash中, 则选择Erase,Program。Verify项,这样重新上电后可以继续运行而不会丢失之前的工程:

手把手教你理解(FFT)

手把手教你理解(FFT) 实验原理 傅里叶变换是一种将信号从时域变换到频域的变换形式,是信号处理的重要 分析工具。离散傅里叶变换(DFT )是傅里叶变换在离散系统中的表示形式。但是DFT 的计算量非常大, FFT 就是DFT 的一种快速算法, FFT 将DFT 的N 2 步运算减少至 ( N/2 )log 2N 步。 离散信号x(n)的傅里叶变换可以表示为: ∑-==1 ][)(N N nk N W n x k X N j N e W /2π-= 式中的W N 称为蝶形因子,利用它的对称性和周期性可以减少运算量。一般而言, FFT 算法分为时间抽取(DIT )和频率抽取(DIF )两大类。两者的区别是蝶形因子出现的位置不同,前者中蝶形因子出现在输入端,后者中出现在输出端。本实验以时间抽取方法为例。前者和后者如图所示:

时间抽取FFT 是将N 点输入序列x(n) 按照偶数项和奇数项分解为偶序列和奇序列。偶序列为:x(0), x(2), x(4),…, x(N -2);奇序列为:x(1), x(3), x(5),…, x(N -1)。这样x(n) 的N 点DFT 可写成: ()()∑∑-=+-=++ = 1 2/0 )12(1 2/0 2122)(N n k n N N n nk N W n x W n x k X 考虑到W N 的性质,即 2/)2//(22/)2(2 ][N N j N j N W e e W ===--ππ 因此有: ()()∑∑-=-=++= 12/0 2 /1 2/0 2 /122)(N n nk N k N N n nk N W n x W W n x k X 或者写成: ()()k Z W k Y k X k N +=)( 由于Y(k) 与Z(k) 的周期为N/2,并且利用W N 的对称性和周期性,即: k N N k N W W -=+2/ 可得: ()()k Z W k Y N k X k N -=+)2/( 对Y(k) 与Z(k) 继续以同样的方式分解下去,就可以使一个N 点的DFT 最终用一组2点的DFT 来计算。在基数为2的FFT 中,总共有log 2(N) 级运算,每级中有N/2 个2点FFT 蝶形运算。 单个蝶形运算示意图如下:

音度手把手教你调音玩转ds

音度手把手教你调音玩 转d s SANY标准化小组 #QS8QHH-HHGX8Q8-GNHHJ8-HHMHGN#

8音度手把手教你调音 玩转DSP 当前浏览器不支持播放音乐或语音,请在微信或其他浏览器中播放 湘妃怨纯音乐 - 中国古典音乐历朝黄金年鉴 8音度教你如何使用均衡器来获得更好的声音表现、如何利用好均衡器调音、图形均衡器怎么用,对汽车音响调音还不够熟悉的小伙伴可以看下哦!包你学会之后对自己调音技术自信满满,提升客户对你的满意度! 如何使用均衡器来获得更好的声音表现 下面来看看均衡器分段后的每个部分的作用: 部分 这一段提升能给音乐强有力的感觉,给人很响的感觉,如雷声。是音乐中强劲有力的感觉,如果这个频段的量感太少,丰润澎湃的感觉一定没有;而且会导致中高频、高频的突出,使得声音失去平衡感,不耐久听。如果提升过高,则又会混浊不清,造成清晰度不佳,特别是低频响应差和低频过重的音响设备。 2. 60Hz--250Hz部分 这段是音乐的低频结构,它们包含了节奏部分的基础音,包括基音、节奏音的主音。它和高中音的比例构成了音色结构的平衡特性。提升这一段可使声音丰满,过度提升会发出隆隆声。衰减这两段会使声音单薄。

3. 250Hz--2KHz部分 这段包含了大多数乐器的低频谐波,如果提升过多会使声音像电话里的声音。如把600Hz和1kHz过度提升会使声音像喇叭的声音。如把3kHz提升过多会掩蔽说话的识别音,即口齿不清,并使唇音“mbv”难以分辨。如把1kHz和3kHz过分提升会使声音具有金属感。由于人耳对这一频段比较敏感,通常不调节这一段,过分提升这一段会使听觉疲劳。 4. 2KHz--4kHz部分这段频率属中频,如果提升得过高会掩盖说话的识别音,尤其是3kHz提升过高,会引起听觉疲劳。 5. 4kHz--5KHz部分 这是具有临场感的频段,它影响语言和乐器等声音的清晰度。提升这一频段,使人感觉声源与听者的距离显得稍近了一些;衰减5kHz,就会使声音的距离感变远;如果在5kHz左右提出升6dB,则会使整个混合声音的声功率提升3dB。 6. 6kHz--16kHz部分

详细手把手教你学dsp教程学习笔记

1、cj 431电压基准芯片,2.5v 2、电平标准 3、驱动器74HC245(为增强PWM的驱动负载能力) 4、增加输入端的抗干扰能力:在芯片的输入端加上拉电阻加电源或者下拉电阻 接地,没有用到的采样端口尽量不要悬空。 5、D/A电路方案

通用扩展语言GEL和c相似,但是有所不同。GEL语言是C语言的一个子集。与c语言不同的是gel不需要指定函数返回值的类型。Gel中的while语句和c中的while语句相同,gel不支持标准c的break和continue语句 6、一个完整的dsp工程包括头文件(.h),库文件(.lib),源文件(.c),以 及配置文件.Cmd 使用关键字MENUITEM可以在gel菜单下选择用户自定义的菜单项,然后用hotmenu、dialog或slider等关键字,在这个新的下拉菜单中添加新的菜单项。 7、关于添加文件遇到的问题

8、变量查找:edit→find:Ctrl+f 9、调试时,添加断点的快捷方法如下 点击图上的小手即可 10、单步调试 第一个的意思是单击一步走一步,第二个的意思是指在单步运行时遇到子函数不进入子函数内部进行而是把它当成一步来执行,第三个的意思是当执行到子函数内部时使用这个按钮就可以执行完剩下的部分返回上一层函数。 如果想在一个窗口内同时看到c和汇编,则有操作View→mixed source/asm 11、观察变量 右击变量→add to watch window 可以得到变量的值、类型、地址等。 12、位域定义、结构体以及共同体的知识

结构体先定义再声明 Union SCIFFCT_REG { Uint16 all; Struct SCIFFCT_BITS bit; }; //--------------------------------------------------------------------------- // SCI Register File: // Struct SCI_REGS { Union SCICCR_REG SCICCR; // Communications control register Union SCICTL1_REG SCICTL1; // Control register 1 Uint16 SCIHBAUD; // Baud rate (high) register Uint16 SCILBAUD; // Baud rate (low) register Union SCICTL2_REG SCICTL2; // Control register 2 Union SCIRXST_REG SCIRXST; // Receive status register

Removed_手把手教你学DSP 2812-寄存器14

DSP2812寄存器汇总 表1中的“书页”指《手把手教你学DSP 》 表1分类 寄存器名称书页说明HISPCP P165高速外设时钟预定标寄存器LOSPCP P165低速外设时钟预定标寄存器PCLKCR P165外设时钟控制寄存器LPMCR0 P165低功耗模式控制寄存器0LPMCR1 P165低功耗模式控制寄存器1PLLCR P165PLL 控制寄存器SCSR P165系统控制和状态寄存器WDCNTY P165看门狗计数器寄存器WDKEY P165看门狗复位密钥寄存器时钟和系统控制模 块寄存器WDCR P165看门狗控制寄存器GPAMUX P173GPIOA 功能选择控制寄存器GPADIR P173GPIOA 方向控制寄存器GPAQUAL P173GPIOA 输入限定控制寄存器GPBMUX P173 GPIOB 功能选择控制寄存器GPBDIR P173GPIOB 方向控制寄存器GPBQUAL P173GPIOB 输入限定控制寄存器GPDMUX P173GPIOD 功能选择控制寄存器GPDDIR P173GPIOD 方向控制寄存器GPDQUAL P173GPIOD 输入限定控制寄存器GPEMUX P173GPIOE 功能选择控制寄存器GPEDIR P173GPIOE 方向控制寄存器GPEQUAL P173GPIOE 输入限定控制寄存器GPFMUX P173GPIOF 功能选择控制寄存器GPFDIR P173GPIOF 方向控制寄存器GPGMUX P173GPIOG 功能选择控制寄存器GPIO 控制寄存器GPGDIR P173GPIOG 方向控制寄存器GPADAT P176GPIOA 数据寄存器GPASET P176GPIOA 置位寄存器GPACLEAR P176GPIOA 清除寄存器GPATOGGLE P176GPIOA 取反寄存器GPBDAT P176GPIOB 数据寄存器GPBSET P176GPIOB 置位寄存器GPBCLEAR P176GPIOB 清除寄存器GPBTOGGLE P176GPIOB 取反寄存器GPIO 数据寄存器GPDDAT P176GPIOD 数据寄存器

- 详细手把手教你学dsp教程学习笔记

- 手把手教你学51单片机(C语言)

- 如何学习DSP

- 07 第七讲 TMS320F28x的C语言编程基础--力天手把手教你学DSP之入门篇

- F28335的ADC转换模块

- 《手把手教你DSP-2812》课件

- 音度手把手教你调音玩转dsp

- 【音响知识】特伦诗手把手教你调音 玩转DSP

- 教你构建一个完整的DSP工程(ccs3.3)

- 音度手把手教你调音玩转ds

- F28335增强型正交编码模块EQEP

- Removed_手把手教你学DSP 2812-寄存器14

- DSP简单例程

- 《手把手教你学DSP-基于TMS320F28335》配套 第二讲 DSP开发环境介绍

- 手把手教你理解(FFT)

- 《手把手教你学DSP-基于TMS320F28335》配套PPT 第二讲 DSP开发环境介绍

- 音度手把手教你调音玩转dsp

- 音度手把手教你调音玩转dsp

- 手把手教你启动空客A320..

- 51单片机最小系统--力天手把手教你学单片机之基础篇