肖特基与欧姆接触

94學年度第二學期無機與有機光電半導體材料與元件-期末報告

The formation of Schottky and Ohmic contact in semiconductor

組員:蕭傑予、李鴻昌

一.Schottky contact:

1.Definition:

Metal-semiconductor contact having a large barrier height and a low doping concentration.

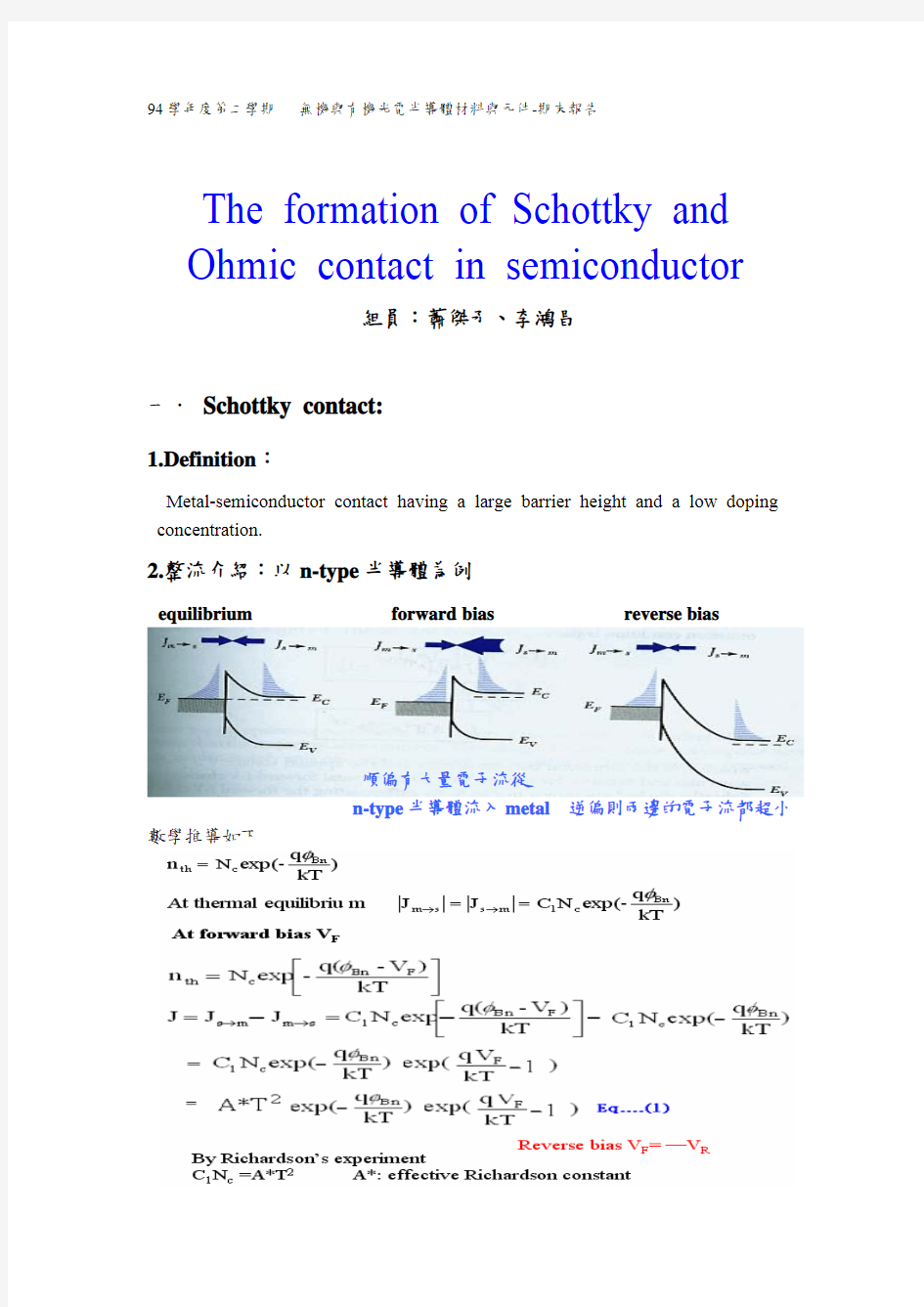

2.整流介紹:以n-type半導體為例

equilibrium forward bias reverse bias

順偏有大量電子流從

n-type半導體流入metal 逆偏則兩邊的電子流都超小數學推導如下

二. Ohmic contact:

1.Definition :

Metal-Semiconductor contact that has a negligible contact resistance relative to the bulk or series resistance of the semiconductor.

2.Specific contact resistance :

(1)With low doping concentrations, thermionic

emission dominates the current.

[]1-e kT

q -exp(T *A J qV/kT

Bn 2

n φ=?

由公式知ΦBn 越大Rc越大 ,但是在low doping concentrations可以看出和N D 無關

(2) With high concentrations, tunneling dominates

the current.

由公式知ΦBn 越大Rc越大,N D 越大則Rc越小, 表示N D 越大tunneling current越大,導致Rc 變小

三. Manufacture:

1. Schottky contact

因元件的表面會有表面能態(surface state)密度累積電荷的緣故而產生空乏區,這種空乏區稱為表面空乏區。由於表面空乏區的存在,使得電子所能流通的電阻增加或電流減少等不佳的效果。為了避免這種情況的發生,採用閘極掘入的方式,使電晶體能在已掘入之閘極下面的真正主動區工作,以求將表面空乏區的影響減少至最低。掘入製程主要是用濕蝕刻的方式來進行;最後再鍍上金屬閘極即完成Schottky contact 的製作。

Surface states :Because of the abrupt discontinuity of the lattice structure at the surface, a large number of localized energy states or

generation-recombination center may be introduced at the surface region.

2. Ohmic contact

Ohmic contact 是指沒有整流效應的低電阻金屬/半導體接觸。理論上來講,只要選擇金屬功函數小於N 型半導體功函數(Φm <Φs)或大於P 型半導體的做毆姆接觸電下能障高度低的情況,在室溫下就會有足夠的載子可以從半導金屬到半導體,這樣的接觸整流效應極小。一般而言金屬與Band bend

,並且能障寬度也會減薄到使z 功函數(Φm >Φs) ,就可以製作出歐姆接觸。但實際上金屬/半導體的能障高度受半導體表面複雜的影響(dangling bonds 、surface states) ,並且極的材料導電性要好,易於焊接,最好是跟半導體一樣有良好的黏附作用。以介紹兩種方式來改善這問題:

1. 低能障接觸→體到金屬或由P 型半導體的接觸能障高度比較低。

2. 高掺雜接觸→在半導體表面如果先用擴散或合金等方法,掺入高濃度的Donor 或Acceptor ,構成金屬/N+/N 半導體或金屬/P+/P 半導體結構,便可形成高摻雜接觸。這種高摻雜接觸在正向電壓時 ,流進金屬/N+/N 半導體是電子電流,這時阻抗很小。在反向電壓時,雖然存在能障,但因為高摻雜的N+層濃度極高,因而會有電子穿遂的機率顯著的不等於零,電子就會容易穿遂進入至金屬內。所以

能障在此並不阻擋電子從半導體進入金屬內,因此反向的阻抗就會大幅減

Transmission Line Model, TLM.)量測法。所謂傳輸線模型(TLM.)之理論,即等效電的平少,即可造成低阻抗接觸。此法亦為目前最被廣用的方式。如下圖所示。

四. T he measure method of Specific contact resistance:

接觸電阻R C ,此值的大小除了和金屬與半導體種類及製程方式有關外,也與金屬半導體間〝接觸面積〞的大小成一反比關係,因此,我們無法以R C 值來客觀評估歐姆接面的好壞。於是,引入另一特徵接觸電阻(specific contact resistance)值ρC ,來作為評斷歐姆接面之電特性表現的標準。一般常用傳輸線模型

(是把電流在金屬與半導體接面、及其下所通過的路徑,看成一個傳輸線的路模型,一般而言,是先將材料上蝕刻出一條一條寬度與接觸面寬度一樣臺,以便將電流侷限到只剩下一維(1-D)的活動方向,以屏除面積的變因。

2T SH c L R ×=ρ

經簡化過可得

R T :各個相同的平面型金屬接觸(長d c :兩接觸面的接觸電阻

:電流密度由最大值衰減到其值的1/e 時,的這段距離 :兩接觸面的間距

SH :可以由R T -L 函數的斜率得到

寬 w )兩者之間的總電阻 R L T L

R

五 c contact

o . Ohmi V .S Sch ttky contact:

但由於有機半導體受surface state 影響很大

Bp =E g -(q Фm -q χ) chottky: .選取 barrier height 小的

I-V relation

(MESFET)

左圖為MESFET 結構,MESFET 的

ce 和drain 都是ohmic contact ,但 t ,和 MOSFET 比較,MESFET 沒有 gate oxidation (金屬直接在半導體上面),而 是 以n-type 無機半導體為例,要做ohmic contact 時, 要找小的work function 的metal,, 找work function 小的metal 未必可以做成好的ohmi c。 q ФBn =(q Фm -q χ) q Ф

Ohmic: 1.選取 barrier height 大的

2.或是把semiconductor high doping

S 1

六cation . Appli sour 在gate 端是用schottky contac 且MESFET 半導體全部都是同一個

type ,但是MOSFET source 和 drain 同一種type ,而gate 是另一種type 。

以n-type semiconductor 為例

在有電流,所以稱為Normally ON , 隨著V G 往負走,因為反向偏壓,空乏區(b 開空為乏大需(b)之缺點為metal-semiconductor 在順偏 較大的電流流過,由於此元件是希望不之間,才在gate 做成schottky contac

半導係,而Ohmic contact 則可以被探討接電阻;這兩種特性在一般製造上很容易被應用到,整流可控制電流容許之流通向,接觸電阻則可控制元件的效益。然而製程與實際應用上還是有可以改善之

. Reference:

ects on CMOS Logic, R. Jacob Baker DEVICES, MICHAEL SHUR 場效電晶體中P 型埋藏層之效應,武良文 (a)圖為一個Normally ON 的MESFET ,一開始metal-semiconductor 之間存空乏區,但未把通道佔滿,在未加電壓時(V G = 0V),只要V DS 有電壓差,即變大,所以電流較低。

為一個Normally OFF 的MESFET ,一始V G 沒加電壓,半導體和金屬之間的乏區佔據了全部的channel ,所以稱Normally OFF ,隨著電壓往正走,空區變小,導致channel 變大,電流變。

要正電源,負電源。

操作,會使metal-semiconductor 有比 要有電流流經過metal-semiconductor t 。

(a)之缺點為電壓可以有正有負的操作,七. Conclusion:

體之中,其與各接觸層的接面關係有很大的影響。對於金屬/半導體的接面關Schottky contact 可被拿來使用在整流上,

觸方處,在此只對基本問題加以簡介與探討。八1.Semiconductor Devices Physics and Technology, S. M. Sze, 2nd edition

2.Mental/Semiconductor and Semiconductor Heterojunctions, Ching-Sung Lee

3.Mental-semiconductor contact, J. B. Lee

4.Schottky Diode RF Detectors an RF Pulse Eff

5.PHYSICS OF SEMICONDUCTOR

6.砷化鎵金屬半導體

7.P-型氮化鎵歐姆接觸製作研究,黃宏基

金属和半导体的接触

金属和半导体的接触 1金属和半导体接触及其能带图 金属和半导体的功函数 金属 1.金属中电子虽然能在金属中自由运动,但绝大多数所处的能级都低于体外能级。要使电子 从金属中逸出,必须有外加能量。所以金属内部的电子是在一个势阱中运动。 2.金属功函数的定义是真空中静止电子的能量E?与费米能级Ef能量之差。表示一个起始能量 等于费米能级的电子,由金属内部逸出到真空中所需要的最小能量。 3.功函数的大小标志着电子在金属中束缚的强弱。W越大,电子越难离开金属。 半导体 接触电势差 金属与(n型)半导体的接触 接触前

qФ为金属一边的势垒高度,qVd为半导体一边的势垒高度。 总结 当金属与n型半导体接触的时候,若Wm>Ws,能带向上弯曲,即可形成表面势垒,在势垒区中,空间电荷主要由电离施主形成,电子浓度比体内小得多,因此它是高阻域,常称为阻挡层;若是Ws>Wm,能带向下弯曲,此时电子浓度比体内高得多,因而是高电导区域,称为反阻挡层,它是很薄的,对金属和半导体接触电阻的影响很小。 p型半导体和金属接触时与n型半导体的相反。 空间电荷区电荷的积累 表面势的形成 造成能带的弯曲 表面态对接触势垒的影响 不同金属与同一半导体材料接触所形成的金属一侧的势垒高度相差不大,金属功函数对势垒高度没有多大影响。 表面能级 1.表面处存在一个距离价带顶为qФ?的能级,若电子正好填满qФ?以下的所有表面态时,表 面呈电中性;若qФ?以下的表面态空着时,表面带正电,呈现施主型;若qФ?以上的表面态被电子填空时,表面带负电,呈现受主型。对于大多数半导体,qФ?约为禁带宽度的三分之一。

2.假设一个n型半导体存在表面态。半导体费米能级Ef将高于qФ?,如果qФ?以上存在有受 主表面态,则在qФ?到Ef间的能级将基本被电子填满,表面带负电。如此,半导体表面附 近必定出现正电荷,成为正的空间电荷区,结果形成了电子的势垒,势垒高度qVD恰好使 得表面态上的负电荷与势垒区的正电荷数量相等,这里着重表明了势垒高度产生的第二层 原因。(第一层是金属与半导体接触) 3.当半导体的表面态密度很高的时候,Ws几乎与施主浓度无关。此时此刻,当D远大于原 子间距时,金属与半导体利用一根导线进行接触,同样有电子流向金属,但此时电子不是 来自于半导体体内,而是来自于受主表面态,若表面态密度很高,能放出足够多的电子, 则半导体势垒区的情形几乎不会发生变化。间隙D中的压降(Ws-Wm)/q,这时空间电荷 区的正电荷等于表面受主态上留下的负电荷与金属表面负电荷之和。当间隙D小到可以与 原子间距相比时,电子就可以自由地穿过它。 施主型 若能级被电子占据时呈电中性,释放电子后呈正电性,称为施主型表面态 受主型 能级空着的时候呈电中性,接受电子后呈负电性; 总结 当半导体表面态密度很高的时候,由于它可以屏蔽金属接触的影响,使半导体内的势垒高度 和金属功函数几乎无关,而基本上由半导体的表面性质所决定。 2金属半导体接触整流理论 定性分析 以n型半导体为例,表面势Vs < 0;半导体一侧的势垒高度即为qVD = - qVs。若此时,我们外加电压V于紧密接触的金属和半导体之间,由于阻挡层是高阻区域,因此电压主要降落在阻挡层上,势垒高度变为-q(Vs+V) V>0 若V > 0,则会导致(Vs + V)降低,便会导致半导体一侧势垒高度降低,这时,从半导体流到金属的电子便会增加,多于从金属流到半导体的电子,便会形成从金属流向半导体的正向 电流。外加电压越大,势垒下降越多,正向电流也就越大。 V<0 若V<0,则(Vs + V)增加,便会导致半导体一侧势垒高度升高,从半导体流到金属的电子 会减少,少于从金属流到半导体的电子,会形成从半导体流向金属的反向电流,又因为金属 的势垒高度基本不会受V的影响,由于金属一侧的电子要越过相当高的势垒才能到达半导体 中,所以反向电流是很小的值。随着电压的增大,势垒高度越来越高,从半导体流向金属的 电子可以忽略不计,反向电流渐渐趋于饱和值。

肖特基二极管的目前趋势

肖特基二极管的目前趋势 虽然肖特基二极管已经上市有几十年了,新的发展和产品却不断增强了它的特性并扩展了应用的可能性。除了太阳能电池板和汽车,它们现在也被用于笔记本电脑、智能手机和平板电脑的电池充电器。 早在1938年,德国物理学家Walter Schottky开发了金属-半导体接触的模型。与半导体-半导体接触相反,肖特基二极管由于材料组成的选择方式在半导体的界面上形成了一个耗尽区而因此具有势垒。这防止了低于特定功率阈值的电功率在金属和半导体之间流通。肖特基二极管因此比其他金属-半导体二极管(例如:表现出欧姆电阻行为的欧姆接触)为转移提供了更大的势垒。 由于这种特性,肖特基二极管主要用于以下两个领域: 1)整流,即在开关电源(开关模式电源,SMPS)或电源整流器内部的交流至直流转换,以及直流电压转换; 2)阻止直流电流和相反极性的直流的反向流动,例如当电池插入不正确时。 由于其较高的开关速度,肖特基二极管主要用于高达微波范围的高频应用。这也是由于它们的低饱和能力。因此它们通常在开关电源中以续流二极管或整流器二极管的形式用作降低感应电压的保护二极管,还可用作检测电路的解调器。 然而,并非所有的肖特基二极管都一样。例如,大多数硅用于高达250V的电压,而砷化镓、碳化硅或硅锗被用作阻断200至1700V电压的半导体材料。硅肖特基二极管具有大约0.4V的低阈值电压,工作电流较低时甚至低于0.1V。这远远低于电压约为1V的半导体-半导体结。肖特基二极管因此可以与硅双极晶体管的集电极基极结并联切换,以防止晶体管的饱和,并且使得晶体管能够显

著更快地切换到阻断状态。然而,它们具有比硅基半导体-半导体二极管更高的漏电流,并且在较高的阻断电压下快速导致高导通损耗。

半导体的欧姆接触

半导体的欧姆接触(2012-03-30 15:06:47)转载▼ 标签:杂谈分类:补充大脑 1、欧姆接触 欧姆接触是指这样的接触:一是它不产生明显的附加阻抗;二是不会使半导体内部的平衡载流子浓度发生显著的改变。 从理论上说,影响金属与半导体形成欧姆接触的主要因素有两个:金属、半导体的功函数和半导体的表面态密度。对于给定的半导体,从功函数对金属-半导体之间接触的影响来看,要形成欧姆接触,对于n型半导体,应该选择功函数小的金属,即满足Wm《Ws,使金属与半导体之间形成n型反阻挡层。而对于p型半导体,应该选择功函数大的金属与半导体形成接触,即满足Wm》Ws,使金属与半导体之间形成p型反阻挡层。但是由于表面态的影响,功函数对欧姆接触形成的影响减弱,对于n型半导体而言,即使Wm《Ws,金属与半导体之间还是不能形成性能良好的欧姆接触。 目前,在生产实际中,主要是利用隧道效应原理在半导体上制造欧姆接触。从功函数角度来考虑,金属与半导体要形成欧姆接触时,对于n型半导体,金属功函数要小于半导体的功函数,满足此条件的金属材料有Ti、In。对于p型半导体,金属功函数要大于半导体的功函数,满足此条件的金属材料有Cu、Ag、Pt、Ni。 2、一些常用物质的的功函数 物质Al Ti Pt In Ni Cu Ag Au 功函数4.3 3.95 5.35 3.7 4.5 4.4 4.4 5.20 3、举例 n型的GaN——先用磁控溅射在表面溅射上Ti/Al/Ti三层金属,然后在卤灯/硅片组成的快速退火装置上进行快速退火:先600摄氏度—后900摄氏度——形成欧姆接触; p型的CdZnTe——磁控溅射仪上用Cu-3%Ag合金靶材在材料表面溅射一层CuAg合金。 欧姆接触[编辑] 欧姆接触是半导体设备上具有线性并且对称的 果电流- 这些金属片通过光刻制程布局。低电阻,稳定接触的欧姆接触是影响集成电路性能和稳定性的关键因素。它们的制备和描绘是电路制造的主要工作。 目录 [隐藏] ? 1 理论 ? 2 实验特性 ? 3 欧姆接触的制备 ? 4 技术角度上重要的接触类型 ? 5 重要性 ? 6 参考资料

肖特基二极管简介

肖特基二极管 简介 肖特基二极管是以其发明人肖特基博士(Schottky)命名的,SBD是肖特基势垒二极管(SchottkyBarrierDiode,缩写成SBD)的简称。SBD不是利用P型半导体与N型半导体接触形成PN结原理制作的,而是利用金属与半导体接触形成的金属-半导体结原理制作的。因此,SBD也称为金属-半导体(接触)二极管或表面势垒二极管,它是一种热载流子二极管。 是近年来问世的低功耗、大电流、超高速半导体器件。其反向恢复时间极短(可以小到几纳秒),正向导通压降仅0.4V左右,而整流电流却可达到几千毫安。这些优良特性是快恢复二极管所无法比拟的。中、小功率肖特基整流二极管大多采用封装形式。 原理 肖特基二极管是贵金属(金、银、铝、铂等)A为正极,以N型半导体B为负极,利用二者接触面上形成的势垒具有整流特性而制成的金属-半导体器件。因为N 型半导体中存在着大量的电子,贵金属中仅有极少量的自由电子,所以电子便从浓度

高的B中向浓度低的A中扩散。显然,金属A中没有空穴,也就不存在空穴自A向B的扩散运动。随着电子不断从B扩散到A,B表面电子浓度逐渐降低,表面电中性被破坏,于是就形成势垒,其电场方向为B→A。但在该电场作用之下,A中的电子也会产生从A→B的漂移运动,从而消弱了由于扩散运动而形成的电场。当建立起一定宽度的空间电荷区后,电场引起的电子漂移运动和浓度不同引起的电子扩散运动达到相对的平衡,便形成了肖特基势垒。 典型的肖特基整流管的内部电路结构是以N型半导体为基片,在上面形成用砷作掺杂剂的N-外延层。阳极使用钼或铝等材料制成阻档层。用二氧化硅(SiO2)来消除边缘区域的电场,提高管子的耐压值。N型基片具有很小的通态电阻,其掺杂浓度较H-层要高100%倍。在基片下边形成N+阴极层,其作用是减小阴极的接触电阻。通过调整结构参数,N型基片和阳极金属之间便形成肖特基势垒,如图所示。当在肖特基势垒两端加上正向偏压(阳极金属接电源正极,N型基片接电源负极)时,肖特基势垒层变窄,其内阻变小;反之,若在肖特基势垒两端加上反向偏压时,肖特基势垒层则变宽,其内阻变大。 综上所述,肖特基整流管的结构原理与PN结整流管有很大的区别通常将PN结整流管称作结整流管,而把金属-半导管整流管叫作肖特基整流管,近年来,采用硅平面工艺制造的铝硅肖特基二极管也已问世,这不仅可节省贵金属,大幅度降低成本,还改善了参数的一致性。 优点 SBD具有开关频率高和正向压降低等优点,但其反向击穿电压比较低,大多不高于60V,最高仅约100V,以致于限制了其应用范围。像在开关电源(SMPS)和功率因数校正(PFC)电路中功率开关器件的续流二极管、变压器次级用100V以上的高频整流二极管、RCD缓冲器电路中用600V~1.2kV的高速二极管以及PFC升压用600V二极管等,只有使用快速恢复外延二极管(FRED)和超快速恢复二极管(UFRD)。目前UFRD的反向恢复时间Trr也在20ns以上,根本不能满足像空间站等领域用1MHz~3MHz的SMPS需要。即使是硬开关为100kHz的SMPS,由于UFRD的导通损耗和开关损耗均较大,壳温很高,需用较大的散热器,从而使SMPS 体积和重量增加,不符合小型化和轻薄化的发展趋势。因此,发展100V以上的高压SBD,一直是人们研究的课题和关注的热点。近几年,SBD已取得了突破性的进展,150V和200V的高压SBD已经上市,使用新型材料制作的超过1kV的SBD也研制成功,从而为其应用注入了新的生机与活力。 结构 新型高压SBD的结构和材料与传统SBD是有区别的。传统SBD是通过金属与半导体接触而构成。金属材料可选用铝、金、钼、镍和钛等,半导体通常为硅(Si)或砷化镓(GaAs)。由于电子比空穴迁移率大,为获得良好的频率特性,故选用N 型半导体材料作为基片。为了减小SBD的结电容,提高反向击穿电压,同时又不使串联电阻过大,通常是在N+衬底上外延一高阻N-薄层。其结构示图如图1(a),图形符号和等效电路分别如图1(b)和图1(c)所示。在图1(c)中,CP是管壳

欧姆接触与肖特基接触

欧姆接触 欧姆接触是指金属与半导体的接触,而其接触面的电阻值远小于半导体本身的电阻,使得组件操作时,大部分的电压降在活动区(Active region)而不在接触面。欧姆接触在金属处理中应用广泛,实现的主要措施是在半导体表面层进行高掺杂或者引入大量复合中心。 欧姆接触指的是它不产生明显的附加阻抗,而且不会使半导体内部的平衡载流子浓度发生显著的改变。 条件 欲形成好的欧姆接触,有二个先决条件: (1)金属与半导体间有低的势垒高度(Barrier Height) (2)半导体有高浓度的杂质掺入(N ≧10EXP12 cm-3) 区别 前者可使界面电流中热激发部分(Thermionic Emission)增加;后者则使半导体耗尽区变窄,电子有更多的机会直接穿透(Tunneling),而同时使Rc阻值降低。 若半导体不是硅晶,而是其它能量间隙(Energy Gap)较大的半导体(如GaAs),则较难形成欧姆接触 (无适当的金属可用),必须于半导体表面掺杂高浓度杂质,形成Metal-n+-n or Metal-p+-p等结构。 理论 任何两种相接触的固体的费米能级(Fermi level)(或者严格意义上,化学势)必须相等。费米能级和真空能级的差值称作工函数。接触金属和半导体具有不同的工函,分别记为φM和φS。当两种材料相接触时,电子将会从低工函一边流向另一边直到费米能级相平衡。从而,低工函的材料将带有少量正电荷而高工函材料则会变得具有少量电负性。最终得到的静电势称为内建场记为Vbi。这种接触电势将会在任何两种固体间出现并且是诸如二极管整流现象和温差电效应等的潜在原因。内建场是导致半导体连接处能带弯曲的原因。明显的能带弯曲在金属中不会出现因为他们很短的屏蔽长度意味着任何电场只在接触面间无限小距离内存在。 欧姆接触或肖特基势垒形成于金属与n型半导体相接触。 欧姆接触或肖特基势垒形成于金属与p型半导体相接触。在经典物理图像中,为了克服势垒,半导体载流子必须获得足够的能量才能从费米能

肖特基接触与欧姆接触

欧姆接触 是指金属与半导体的接触,而其接触面的电阻值远小于半导体本身的电阻,使得组件操作时,大部分的电压降在活动区(Active region)而不在接触面。 欲形成好的欧姆接触,有二个先决条件: (1)金属与半导体间有低的势垒高度(Barrier Height) (2)半导体有高浓度的杂质掺入(N ≧10EXP12 cm-3) 前者可使界面电流中热激发部分(Thermionic Emission)增加;后者则使半导体耗尽区变窄,电子有更多的机会直接穿透(Tunneling),而同时使Rc阻值降低。 若半导体不是硅晶,而是其它能量间隙(Energy Cap)较大的半导体(如GaAs),则较难形成欧姆接触(无适当的金属可用),必须于半导体表面掺杂高浓度杂质,形成Metal-n+-n or Met al-p+-p等结构。 理论 任何两种相接触的固体的费米能级(Fermi level)(或者严格意义上,化学势)必须相等。费米能级和真空能级的差值称作工函。接触金属和半导体具有不同的工函,分别记为φM和φS。当两种材料相接触时,电子将会从低工函一边流向另一边直到费米能级相平衡。从而,低工函的材料将带有少量正电荷而高工函材料则会变得具有少量电负性。最终得到的静电势称为内建场记为Vbi。这种接触电势将会在任何两种固体间出现并且是诸如二极管整流现象和温差电效应等的潜在原因。内建场是导致半导体连接处能带弯曲的原因。明显的能带弯曲在金属中不会出现因为他们很短的屏蔽长度意味着任何电场只在接触面间无限小距离内存在。 欧姆接触或肖特基势垒形成于金属与n型半导体相接触。 欧姆接触或肖特基势垒形成于金属与p型半导体相接触。在经典物理图像中,为了克服势垒,半导体载流子必须获得足够的能量才能从费米能级跳到弯曲的导带顶。穿越势垒所需的能量φB是内建势及费米能级与导带间偏移的总和。同样对于n型半导体,φB = φM ? χS当中χS是半导体的电子亲合能(electron affinity),定义为真空能级和导带(CB)能级的差。对于p型半导体,φB = Eg ? (φM ? χS)其中Eg是禁带宽度。当穿越势垒的激发是热力学的,这一过程称为热发射。真实的接触中一个同等重要的过程既即为量子力学隧穿。WKB近似描述了最简单的包括势垒穿透几率与势垒高度和厚度的乘积指数相关的隧穿图像。对于电接触的情形,耗尽区宽度决定了厚度,其和内建场穿透入半导体内部长度同量级。耗尽层宽度W可以通过解泊松方程以及考虑半导体内存在的掺杂来计算: 在MKS单位制ρ 是净电荷密度而ε是介电常数。几何结构是一维的因为界面被假设为平面的。对方程作一次积分,我们得到 积分常数根据耗尽层定义为界面完全被屏蔽的长度。就有 其中V(0) = Vbi被用于调整剩下的积分常数。这一V(x)方程描述了插图右手边蓝色的断点曲线。耗尽宽度可以通过设置V(W) = 0来决定,结果为

肖特基接触与欧姆接触

欧姆接触是半导体设备上具有线性并且对称的电流-电压特性曲线(I-V curve)的区域。如果电流-电压特性曲线不是线性的,这种接触便叫做肖特基接触。 理论:任何相接触的固体的费米能级(化学势)必须相等,费米能级和真空能级的差值称为功函数,因而,接触的金属和半导体具有不同的功函数。当两种材料相接触的时候电子会从低功函数的的一端流向另一端直到费米能级平衡;从而低功函数的材料带有少量正电荷,高功涵的材料带有少量负电荷,最终得到的静电势称为内建场。内建场是导致半导体连接处能带弯曲的原因。 欧姆接触是指金属与半导体的接触,而其接触面的电阻值远小于半导体本身的电阻,使得组件操作时,大部分的电压降在活动区(Active region)而不在接触面。 欲形成好的欧姆接触,有二个先决条件: (1)金属与半导体间有低的势垒高度(Barrier Height)使界面电流中热激发部分(Thermionic Emission)增加 (2)半导体有高浓度的杂质掺入(N ≧10EXP12 cm-3) 使半导体耗尽区变窄,电子有更多的机会直接穿透(Tunneling),而同时使Rc阻值降低。 若半导体不是硅晶,而是其它能量间隙(Energy Cap)较大的半导体(如GaAs),则较难形成欧姆接触 (无适当的金属可用),必须于半导体表面掺杂高浓度杂质,形成Metal-n+-n or Metal-p+-p等结构。 肖特基接触是指金属和半导体材料相接触的时候,在界面处半导体的能带弯曲,形成肖特基势垒。势垒的存在才导致了大的界面电阻。与之对应的是欧姆接触,界面处势垒非常小或者是没有接触势垒。 理论:当半导体与金属接触的时候由于半导体的电子逸出功一般比金属小,电子就从半导体流入了金属,在半导体的表面层形成一个带正电不可移动的杂质离子组成的空间电荷区域。电场方向由半导体指向金属,阻止电子继续向金属中扩散。界面处半导体能带发生了弯曲,想成一个高势能区,这就是肖特基势垒。 肖特基势垒的高度是金属和半导体的逸出功的差值。

欧姆接触

1.1 金属-半导体接触的基本原理 金属-半导体接触(金半接触)是制作半导体器件中十分重要的问题,接触情况直接影响到器件的性能。从性质上可以将金属-半导体接触分为肖特基接触和欧姆接触。肖特基接触的特点是接触区的电流-电压特性是非线性的,呈现出二极管的特性,因而具有整流效应,所以肖特基接触又叫整流接触。欧姆接触的特点是不产生明显的附加阻抗,而且不会使半导体内部的平衡载流子浓度产生明显的改变。理想的欧姆接触的接触电阻与半导体器件相比应当很小,当有电流通过时,欧姆接触上的电压降应当远小于半导体器件本身的电压降,因而这种接触不会影响器件的电流-电压特性[1]。下面将从理论上对金属-半导体接触进行简要的分析。 1.2欧姆接触 本章1.1节中提到,当金属-半导体接触的接触区的I-V曲线是线性的,并且接触电阻相对于半导体体电阻可以忽略不计时,则可被定义为欧姆接触(ohmic contact)[1]。良好的欧姆接触并不会降低器件的性能,并且当有电流通过时产生的电压降比器件上的电压降还要小。 1.2.1欧姆接触的评价标准 良好的欧姆接触的评价标准是[4]: 1)接触电阻很低,以至于不会影响器件的欧姆特性,即不会影响器件I-V的线 性关系。对于器件电阻较高的情况下(例如LED器件等),可以允许有较大的接触电阻。但是目前随着器件小型化的发展,要求的接触电阻要更小。2)热稳定性要高,包括在器件加工过程和使用过程中的热稳定性。在热循环的 作用下,欧姆接触应该保持一个比较稳定的状态,即接触电阻的变化要小,尽可能地保持一个稳定的数值。 3)欧姆接触的表面质量要好,且金属电极的黏附强度要高。金属在半导体中的 水平扩散和垂直扩散的深度要尽可能浅,金属表面电阻也要足够低。

肖特基与欧姆接触

94學年度第二學期無機與有機光電半導體材料與元件-期末報告 The formation of Schottky and Ohmic contact in semiconductor 組員:蕭傑予、李鴻昌 一.Schottky contact: 1.Definition: Metal-semiconductor contact having a large barrier height and a low doping concentration. 2.整流介紹:以n-type半導體為例 equilibrium forward bias reverse bias 順偏有大量電子流從 n-type半導體流入metal 逆偏則兩邊的電子流都超小數學推導如下

二. Ohmic contact: 1.Definition : Metal-Semiconductor contact that has a negligible contact resistance relative to the bulk or series resistance of the semiconductor. 2.Specific contact resistance : (1)With low doping concentrations, thermionic emission dominates the current. []1-e kT q -exp(T *A J qV/kT Bn 2 n φ=? 由公式知ΦBn 越大Rc越大 ,但是在low doping concentrations可以看出和N D 無關 (2) With high concentrations, tunneling dominates the current. 由公式知ΦBn 越大Rc越大,N D 越大則Rc越小, 表示N D 越大tunneling current越大,導致Rc 變小

肖特基二极管

肖特基二极管 肖特基二极管是以其发明人肖特基博士(Schottky)命名的,SBD是肖特基势垒二极管(SchottkyBarrierDiode,缩写成SBD)的简称。SBD不是利用P型半导体与N型半导体接触形成PN结原理制作的,而是利用金属与半导体接触形成的金属-半导体结原理制作的。因此,SBD也称为金属-半导体(接触)二极管或表面势垒二极管,它是一种热载流子二极管。 简介 肖特基二极管是以其发明人肖特基博士(Schottky)命名的,SBD是肖特基势垒二极管 肖特基二极管结构原理图 (SchottkyBarrierDiode,缩写成SBD)的简称。SBD不是利用P型半导体与N型半导体接触形成PN结原理制作的,而是利用金属与半导体接触形成的金属-半导体结原理制作的。因此,SBD也称为金属-半导体(接触)二极管或表面势垒二极管,它是一种热载流子二极管。是近年来问世的低功耗、大电流、超高速半导体器件。其反向恢复时间极短(可以小到几纳秒),正向导通压降仅0.4V左右,而整流电流却可达到几千毫安。这些优良特性是快恢复二极管所无法比拟的。中、小功率肖特基整流二极管大多采用封装形式。 原理 肖特基二极管是贵金属(金、银、铝、铂等)A为正极,以N型半导体B为负极,利用二者接触面上形成的势垒具有整流特性而制成的金属-半导体器件。因为N型半导体中存在着大量的电子,贵金属中仅有极少量的自由电子,所以电子便从浓度高的B中向浓度低的A中扩散。显然,金属A中没有空穴,也就不存在空穴自A向B的扩散运动。随着电子不断从B扩散到A,B表面电子浓度逐渐降低,表面电中性被破坏,于是就形成势垒,其电场方向为B→A。但在该电场作用之下,A中的电子也会产生从A→B的漂移运动,从而消弱了由于扩散运动而形成的电场。当建立起一定宽度的空间电荷区后,电场引起的电子漂移运动和浓度不同引起的电子扩散运动达到相对的平衡,便形成了肖特基势垒。

肖特基接触与欧姆接触

欧姆接触是指金属与半导体的接触,而其接触面的电阻值远小于半导体本身的电 阻,使得组件操作时,大部分的电压降在活动区(Active region)而不在接触面。 欲形成好的欧姆接触,有二个先决条件: (1)金属与半导体间有低的势垒高度(Barrier Height) (2)半导体有高浓度的杂质掺入(N ≧10EXP12 cm-3) 前者可使界面电流中热激发部分(Thermionic Emission)增加;后者则使半导体耗尽区变窄,电子有更多的机会直接穿透(Tunneling),而同时使Rc阻值降低。 若半导体不是硅晶,而是其它能量间隙(Energy Cap)较大的半导体(如GaAs),则较难形成欧姆接触(无适当的金属可用),必须于半导体表面掺杂高浓度杂质,形成Metal-n+-n or Metal-p+-p等结构。 [编辑本段] 理论 任何两种相接触的固体的费米能级(Fermi level)(或者严格意义上,化学势)必须相等。费米能级和真空能级的差值称作工函。接触金属和半导体具有不同的工函,分别记为φM和φS。当两种材料相接触时,电子将会从低工函一边流向另一边直到费米能级相平衡。从而,低工函的材料将带有少量正电荷而高工函材料则会变得具有少量电负性。最终得到的静电势称为内建场记为Vbi。这种接触电势将会在任何两种固体间出现并且是诸如二极管整流现象和温差电效应等的潜在原因。内建场是导致半导体连接处能带弯曲的原因。明显的能带弯曲在金属中不会出现因为他们很短的屏蔽长度意味着任何电场只在接触面间无限小距离内存在。 欧姆接触或肖特基势垒形成于金属与n型半导体相接触。 欧姆接触或肖特基势垒形成于金属与p型半导体相接触。在经典物理图像中,为了克服势垒,半导体载流子必须获得足够的能量才能从费米能级跳到弯曲的导带顶。穿越势垒所需的能量φB是内建势及费米能级与导带间偏移的总和。同样对于n型半导体,φB = φM ? χS当中χS是半导体的电子亲合能(electron affinity),定义为真空能级和导带(CB)能级的差。对于p型半导体,φB = Eg ? (φM ? χS)其中E g是禁带宽度。当穿越势垒的激发是热力学的,这一过程称为热发射。真实的接触中一个同等重要的过程既即为量子力学隧穿。WKB近似描述了最简单的包括势垒穿透几率与势垒高度和厚度的乘积指数相关的隧穿图像。对于电接触的情形,耗尽区宽度决定了厚度,其和内建场穿透入半导体内部长度同量级。耗尽层宽度W可以通过解泊松方程以及考虑半导体内存在的掺杂来计算: 在MKS单位制ρ 是净电荷密度而ε是介电常数。几何结构是一维的因为界面被假设为平面的。对方程作一次积分,我们得到 积分常数根据耗尽层定义为界面完全被屏蔽的长度。就有 其中V(0) = Vbi被用于调整剩下的积分常数。这一V(x)方程描述了插图右手边蓝色的断点曲线。耗尽宽度可以通过设置V(W) = 0来决定,结果为

肖特基势垒和欧姆接触_孟庆忠

烟台师范学院学报(自然科学版)Yantai T eachers U niversity Journal (N atural Science ) 2000,16(2):153-156教学 研究 收稿日期:2000203218 作者简介:孟庆忠(1942—),男,教授,大学本科,从事电子技术基础理论研究. 肖特基势垒和欧姆接触 孟 庆 忠 (青岛大学师范学院物理系,山东青岛266071) 摘要:用能带结构的观点分析了金属和半导体相接触时的机理,并简要介绍了肖特基二极管的构造及应用. 关键词:肖特基势垒;欧姆接触;费米能级 中图分类号:TN 710.1 文献标识码:A 文章编号:100424930(2000)022******* P 型半导体和N 型半导体通过掺杂方式结合而成的PN 结,是一种比较复杂的半导体结构.这种结构的重要特征之一是在结的相邻两侧,两种载流子的分布具有不对称的特性,从而形成载流子的浓度梯度,结果使PN 结具有非线性的伏安特性.在制造半导体器件的过程中,除了有PN 结之外,还会遇到金属和半导体相接触的情况,这种接触(指其间距离只有几个埃)有时会在半导体表面形成载流子的积累层,从而表现出低阻特性,其伏安特性是线性的;有时会在半导体表面形成载流子的耗尽层(阻挡层),出现表面势垒,其伏安特性与PN 结相似,呈非线性状态.上述两种情况在实际应用中都有用到之处〔1〕,前者可用来作欧姆接触,后者可用来制作肖特基势垒二极管. 1 肖特基势垒 从能级的观点来看,要使金属或半导体中的电子脱离原子核的束缚成为体外自由电子,就必须做功.因为金属或半导体内的绝大多数电子都比体外电子处于较低的能级.物体对电子束缚的强弱决定于物体的性质和表面情况,我们称之为逸出功.显然,逸出功越大,电子越不容易离开物体.由半导体物理学知识可知,物体的逸出功等于体外静止电子的能量与该物体费米能级之差. 现以N 型半导体为例.如果N 型半导体的逸出功小于金属的逸出功,这种费米能级的差别意味着在金属内部和半导体导带相对应的那部分能级上,电子的密度要小于半导体导带的电子密度,因此当它们接触时,电子便从半导体向金属扩散,结果使金属带负电,半导体带正电.对于金属而言,负电荷只能分布在表面;而对于N 型半导体来说,施主杂质失去电子成为正离子,由于掺杂浓度有限,这些正离子必须分布在一定厚度的空间电荷区内,其间的载流子(电子)浓度几乎为零,因而形成了高阻的耗尽层,电荷分布如图1所

comsol案例——肖特基接触

肖特基接触 本篇模拟了由沉积在硅晶片上的钨触点制成的理想肖特基势垒二极管的行为。将从正向偏压下的模型获得的所得J-V(电流密度与施加电压)曲线与文献中发现的实验测量进行比较 介绍 当金属与半导体接触时,在接触处形成势垒。这主要是金属和半导体之间功函数差异的结果。在该模型中,理想的肖特基接触用于对简单的肖特基势垒二极管的行为进行建模。使用“理想”这个词意味着在这里,表面状态,图像力降低,隧道和扩散效在界面处计算半导体与金属之间传输的电流应被忽略。 注意,理想的肖特基接触的特征在于热离子电流,其主要取决于施加的金属- 半导体接触的偏压和势垒高度。这些接触通常发生在室温下掺杂浓度小于1×1016 cm-3的非简并半导体中。 模型定义 该模型模拟钨 - 半导体肖特基势垒二极管的行为。图1显示了建模设备的几何形状。它由n个掺杂的硅晶片(Nd = 1E16cm-3)组成,其上沉积有钨触点。该模型计算在正向偏压(0至0.25V)下获得的电流密度,并将所得到的J-V曲线与参考文献中给出的实验测量进行比较。该模型使用默认的硅材料属性以 及一个理想的势垒高度由下列因素定义: ΦB=Φm-χ0(1) 其中ΦB是势垒高度,Φm是金属功函数,χ0是半导体的电子亲和力。选择钨触点的功函数为 Φm = 4,72V (2) 其中势垒高度为ΦB= 0.67V。 结果与讨论 图2显示了使用我们的模型(实线)在正向偏压下获得的电流密度,并将其与参考文献中给出的实验测量进行比较ref. 1(圆)。

建模说明 从文件菜单中,选择新建NEW。 N E W 1在“新建”窗口中,单击“模型向导”。 MODEL WIZARD 1 在模型向导窗口,选择2D轴对称 22在选择物理树中,选择半导体>半导体(semi)。 3单击添加。 4点击研究。 5在“选择”树中,选择“预设研究”>“稳态”。 6单击完成。 D E F I N I T I O N S 参数 1在“模型”工具栏上,单击“参数”。 2在“参数”的“设置”窗口中,找到“参数”部分。3在表格中,输入以下设置: 选择um做长度单位

肖特基势垒二极管知多少_2317

肖特基势垒二极管知多少_2317 肖特基势垒二极管知多少 金属-半导体(MS)结,是众所周知的最普通的“肖特基势垒二极管 ”,有时,它被称为“表面势垒二极管”。由于在界面处能带不连续,注入的载流子具有过高的能量,该结构也被称为“热载流子二极管 ”或“热电子二极管”。MS结也是许多其它器件应用的有效器件结构。特殊类型的MS结是“欧姆接触”,半导体是重掺杂。显然,欧姆接触是每一种半导体器件都需要的,因为最终的导体总是金属。 金属-半导体系统是早期的半导体器件之一,其器件的应用可以追溯到1900年以前。在半导体表面由空间电荷产生势垒,是1938年肖特基和莫特独自实现的。 早期类型的肖特基势垒二极管是“点接触”形式,在点接触的位置,将金属线压焊在干净的金属表面上,金属线曾被称为猫的胡须。(点接触具有肖特基势垒特性或p-n结特性,取决于形成工艺)。这种结构不可靠,也不能重复加工,后来被真空淀积金属取代。对硅衬底,在金属的位置,可以使用金属性硅化物。 制作肖特基势垒二极管的关键工艺步骤,是准备干净的表面,用于金属的紧密接触。在制作中,采用化学方法,将表面清洗干净。实验者也要检测分开的表面,并采用真空反溅射方法清洗。通常,采用蒸发或溅射方法,在真空中淀积金属。化学淀积方法正得到普及,特别是难熔金属得到更多应用。电镀方法也有应用,但是溶液的粘污不易得到控制。硅衬底上的硅化物,通常是采用金属淀积制得,接着进行加热处理以形成硅化物。这种系统可能是最理想的,因为其反应将消耗硅,而硅化物和半导体界面将从原来表面向下扩展。肖特基势垒的优点之一是低温工艺,不需要杂质扩散过程中的高温工艺步骤,也可避免离子注入后的杂质激活。