Cadence原理图库属性添加修改-UPD功能介绍

Cadence如何使用UPD功能批量修改元器件信息

1.元器件属性介绍(用cadence做过原理图封装的可以跳过)

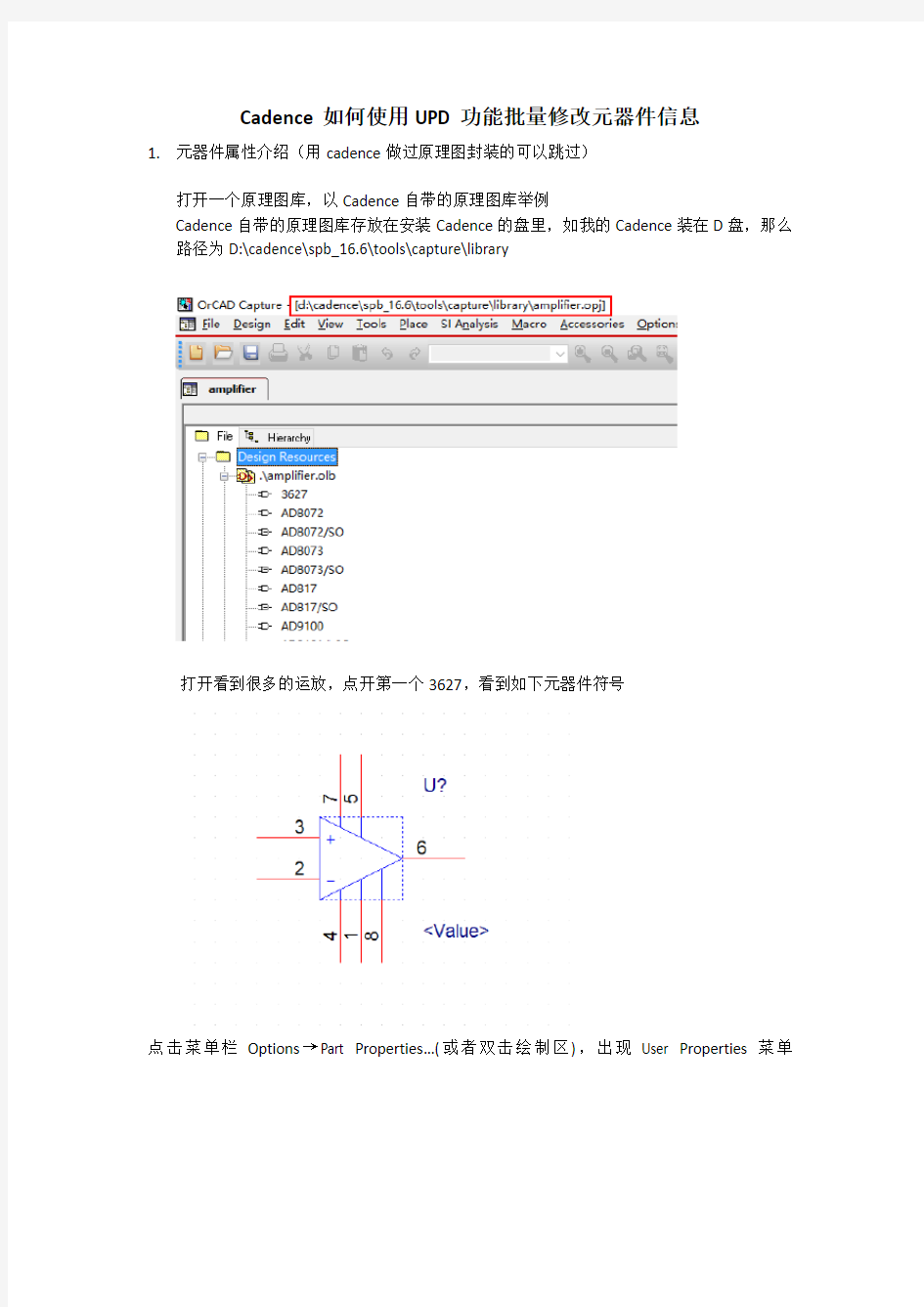

打开一个原理图库,以Cadence自带的原理图库举例

Cadence自带的原理图库存放在安装Cadence的盘里,如我的Cadence装在D盘,那么路径为D:\cadence\spb_16.6\tools\capture\library

打开看到很多的运放,点开第一个3627,看到如下元器件符号

点击菜单栏Options→Part Properties…(或者双击绘制区),出现User Properties菜单

这里就是这个器件的基本属性信息,用户可以自行添加需要的属性,如有些需要添加器件功能描述,有些需要添加器件ERP编号等等,

我们可以通过右栏的New来新增添加,这种方法对于要同时添加很多信息或者很多器件的人来说是很费时的,那么我们自然想到批量修改的方法。

2.UPD功能详细介绍

为了解决上面的问题,cadence支持文件批量添加更改功能,简称UPD功能。

继续上面的例子来新增信息,增加厂家信息,厂家名称,输入电压范围,输出电压范围,SVN编号等。

就以前两个器件举例来添加,如下

2.1新建一个TXT文本(当然可以用其他编辑工具,比如UE),输入需要添加的信息,并

将器件对应的信息填上,如下

这里需要说明一下,Name就是器件名称,一定要一致,后缀.Normal是器件属性的名称,

有些元器件厂家没有给出相应信息,我们可以直接双引号,表示空白以后更新用,英文的双引号。

2.2将新建的文本文档保存为UPD格式,为了以后对信息的修改维护方便,文件名最好和库名字一样,保存位置也和库文件放一起,本例库名字是amplifier。

保存好,就显示为UPD文件了,如下

2.3下一步就是将这些信息更新到原理图库里了,在如下界面选择Tools

→Update Properties

出现如下界面

红框位置打勾选上,注意最后一栏UPD路径这里要选择上一步文件保存的位置,点OK,如果不报错,那么属性添加成功。

结尾:点开器件,看看属性是否添加好了,

如上看到确实添加成功了,一个库里的其他器件也可以以此为例添加齐全,如要修改,UPD文件里修改好,如上再操作一遍,会替换原来的属性。

最后补充两点:

1.UPD里出现的器件,库里必须要有,否则导入会出错,所有描述都要加上英文字符

的双引号。

2.有些器件是由不相同的几部分组成,那么UPD里也要把每部分写上,否则做BOM

时会出现几个器件,总之UPD里的name信息要与原理图封装里的每部分name对应上。

像AD8072是由相同的两部分组成,点开属性名字都是AD8072.Normal,同单个器件。

OrCAD Capture CIS Cadence原理图绘制

OrCADCaptureCIS(Cadence原理图绘制) 1,打开软件........................................ 2,设置标题栏..................................... 3,创建工程文件................................... 4,设置颜色........................................ 2.制作原理库.......................................... 1,创建元件库...................................... 2,修改元件库位置,新建原理图封库................. 3,原理封装库的操作............................... 3.绘制原理图.......................................... 1.加入元件库,放置元件............................ 2.原理图的操作.................................... 3.browse命令的使用技巧 ........................... 4.元件的替换与更新................................ 4.导出网表............................................ 1.原理图器件序号修改.............................. 2.原理图规则检查.................................. 3.显示DRC错误信息................................ 4.创建网表........................................ 5.生成元件清单(.BOM)..................................

CADENCE工具VIRTUSO-DRACULA入门介绍

CADENCE工具VIRTUSO/DRACULA入门介绍 (2) 1.使用V IRTUSO/D IV A/D RACULA之前的准备 (2) 1.1.找一台装有IC工具的服务器 (2) 1.2.连接到这台计算机上 (2) 2.IC工具的软件环境配置 (3) 2.1.创建IC工具的启动目录,即工作目录。 (3) 2.2.将配置文件拷贝到IC工具的启动目录 (3) 2.3.将工艺文件和显示文件拷贝至工作目录 (3) 2.4.启动IC工具,命令为icfb& (3) 3.IC工具的使用 (4) 3.1.新建一个设计库 (4) 3.2.Compile一个工艺文件 (5) 3.3.创建新设计 (5) 3.4.编辑电路图 (5) 3.5.编辑版图 (6) 3.6.根据习惯改变版图层次的显示特性 (7) 3.7.完成版图编辑之后保存,退出 (8) 4.版图的DRC检查 (8) 4.1.基于Diva的方式(不推荐) (8) 4.2.基于Dracula的方式(推荐) (8) 5.LVS (10) 5.1.准备版图的GDS文件 (10) 5.2.准备电路网表 (10) 5.3.用LOGLVS转换电路网表成LVS要求格式 (11) 5.4.修改lvs的命令文件 (12) 5.5.运行PDRACULA来生成lvs任务的可执行文件 (12) 5.6.在控制台下,运行https://www.wendangku.net/doc/f812590540.html,文件 (12) 5.7.查看错误 (12) 5.8.修正版图或网表错误 (13) 6.一些小经验 (13) 7.附件清单 (14)

Cadence工具Virtuso/Dracula入门介绍 (以上华0.6um DPDM工艺设计库为例) Cadence 是一套功能强大的EDA软件,包含有诸如IC、SE等常用芯片设计工具。其中IC是针对全定制芯片设计应用的,IC本身仍是一套工具集。本手册主要讨论其中的全定制版图设计工具Virtuso和验证工具Diva/Dracula之使用方法。其中Diva是基于Xwindow 的方式,而Dracula是基于命令行的方式;Virtuso中提供这两者的相关接口。 采用Virtuso/ Diva/Dracula进行芯片的设计和验证大致有如下几步:准备schmematic(电路)、画layout(版图)、作版图设计规则检查(DRC)、做电路与版图的一致性检查(LVS)、导出最终版图的gds文件。 缩写术语: ERC: Electrical Rule Check DRC: Design Rule Check LVS: Layout Versus Schematic LPE: Layout Parameter Extraction PRE: Parasitic Resistor Extraction 1.使用Virtuso/Diva/Dracula之前的准备 1.1.找一台装有IC工具的服务器 Virtuso不能单独安装,所以只有在安装了IC工具的计算机上才能使用。 [例]机房的10台服务器(IP:219.223.169.111到219.223.169.120)都能使用Virtuso/Diva/Dracula. 1.2.连接到这台计算机上 除非是在自己的计算机上安装有IC工具,否则您必须保证能够从您的计算机远程登录到装有IC的服务器上。 [例]以登录服务器IC来说明远程登录方法: a.向管理员申请用户(每个人都已经有了一个用户) b.下载远程登录软件Exceed, 在本地计算机上安装; 安装完毕之后进行远程登录配置: 在开始菜单→程序→Hummingbird.Exceed.v7.1.Multilanguage→Exceed→Client Wizard设定xterm,Host:219.223.169.111,Host type: Linux(下拉菜单选择),其余next即可。c.完成登录。 采用其它方式比如vnc、xWin、SSH Secure Shell Client等远程终端方法登录。 『注意』使用不同的远程登陆软件连接服务器;不同的服务器所需的软件设置均有所不同,配置细节请咨询曾经使用过该登陆软件的师兄师姐或同学。

实验一Virtuoso原理图和图标编辑器的基本使用

实验一Virtuoso原理图和图标编辑器的基本使用 目录 1.实验目的 2.创建一个新的自定义单元库 3.使用 Cadence Virtuoso 原理图编辑器构建一个反相器 4.创建一个自定义元器件图标 1.实验目的 本实验采用AMI06工艺设计一个反相器,以此使学生达到熟悉 Cadence Virtuoso 原理图和图标编辑器使用,记住常用热键组合以及掌握与特定工艺库关联之目的。 2.创建一个新的自定义单元库 启动 Cadence,调用 CIW(Command Interpreter Window) 首先启动计算机,在用户名处键入 cdsusr, 密码处键入123456,进入Linux操作系统桌面,在cdsusr’s Home 文件夹中创建iclabs子文件夹。请记住一定要创建这个子文件夹,这样才不会影响到cdsusr根目录下的cds.lib文件。操作如下:File --> Create Folder, 在新创建的文件夹名称处键入iclabs(可取不同名字,学号和本人名字拼音等)。进入Linux桌面,单击鼠标右键打开终端。见图1。 图1. Linux桌面操作 在打开的终端中执行下列命令:见图2的红色框线内。 图2. Linux终端

执行第二个命令后你就可看见Cadence软件的CIW窗口出现。见图3所示。 图3. Cadence软件的CIW窗口 在CIW窗口中点击Tools-->Library Manager..., 将打开库管理器(图4)。 图4. 库管理器 你可看到NCSU提供的库已显示在Library栏目中,有 NCSU_Analog_Parts,...等。点击库管理器中的File-->New-->Library..., 将打开New Library 对话窗口, 现创建一个新库取名为IClab1。见图5。

Cadence原理图绘制流程

第一章设计流程 传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。设计人员只需要了解本阶段的基本知识及设计方法即可。但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。 细化并调整以上原理图设计阶段的流 程,并结合我们的实际情况,原理图设计 阶段应该包括如下几个过程: 1、 阅读相关资料和器件手册 在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。 2、 选择器件并开始建库 在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。 3、 确认器件资料并完成详细设计框图 为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。 4、 编写相关文档 这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。 5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。 6、使用Concept-HDL绘制原理图 7、检查原理图及相关文档确保其一致性。 以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

Cadence 原理图库设计

Cadence原理图库设计 一.工具及库文件目录结构 Cadence提供Part Developer库开发工具供大家建原理图库使用。 Cadence 的元件库必具备如下文件目录结构为: Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table) Sym_1:存放元件符号 Entity:存放元件端口的高层语言描述 Chips:存放元件的物理封装说明和属性 Part-table:存放元件的附加属性,用于构造企业特定部件 我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。 二.定义逻辑管脚 在打开或新建的Project Manager中,如图示,打开Part Developer。 然后出现如下画面, 点击Create New,下图新菜单中提示大家选择库路径,新建库元件名称及器件类型。

点击ok后,Part Developer首先让大家输入元件的逻辑管脚。一个原理图符号可以有标量管脚和矢量管脚。 标量管脚在符号中有确定位置,便于检查信号与管脚的对应,但矢量管脚却可使原理图更简洁,适用于多位 总线管脚。 点击上图中的Edit,编辑器会让我们对首或尾带有数字的字符串的多种输入方式(A1; 1A; 1A1)进行选择,一但选定,编辑器即可对同时具有数字和字母的管脚输入进行矢量或标量界定。 管脚名首尾均不带数字的字符串如A; A1A则自动被识别为标量管脚。 按照元件手册决定管脚名称及逻辑方向,选择是否为低电平有效,点击ADD即可加入新的管脚。 (注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C)

cadence工具介绍

标签:cadence工具介绍 cadence工具介绍 主要是cadence的常用工具: (一)System & Logic Design & Verification 1、SPW:系统仿真工具,与matlab相似,但是比其专业,用于系统建模,常用于通信系统2、Incisive: 就是大家最常用的nc_verilog, nc_sim, nc_lauch,以及ABV,TBV的集合,仿真和验证功能很强大 (二)Synthesis & Place & Route 1、BuildGates:与DC同期推出的综合工具,但是在国内基本上没有什么市场,偶尔有几家公司用2、RTL Complil er:继BuildGates之后的一个综合工具,号称时序,面积和功耗都优于DC,但是仍然无法取代人们耳熟能详的DC 3、Silicon Ensemble & PKS: 硅谷早期做物理设计的工程师,几乎都用它。是第一个布局布线工具4、First Encount er & SoC Encounter: 继SE以后的很好的P&R工具,但是盗版太少,所以也只有大公司能用且都用,但是目前astro在国内有赶超之意5、Cetlic :噪声分析工具,权威6、Fire&Ice: 分布参数提取工具,国内很多人用synopsys的StarRC 7、VoltageStrom:静态功耗和动态功耗分析的很不错的工具,与s 的Power Complier相同。8、SingnalStrom:时序分析工具,唯一一个能建库的工具9、nanoroute : 很强大的布线器喔,但是不是一般人能用的到的。我也是在cadence实习的时候爽过的,比astro快十倍不止。 (三)custom IC Design 1、Virtoso:版图编辑工具,没有人不知道吧,太常用了,现在还有一个公司的laker 2、diva, dracula, assura: 物理验证工具,用的比较普遍,但是calibre是标准,很多公司都是用其中的一个和calibre同时验证,我好可怜,现在只能用herculus (四)数模混合信号设计这部分太多了,但是一个ADE的环境基本上都能包括,不细说了,打字都打累了(五)PCB A llego最为典型了,很多大公司都用的。 系统分类: 软件开发 | 用户分类: IC设计 | 来源: 原创 | 【推荐给朋 友】 | 【添加到收藏夹】 Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。下面主要介绍其产品线的范围。 1、板级电路设计系统。 包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。包括: A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

CAD原理图库部分

启动 Protel 99SE,用自己的名字建立一个设计数据库文件,在其中新建元件库子文件schlib1.lib,在该文档中创建下列新元件: (图中元件管脚长度为30mil(三格),每小格长度为10mil) 1、OPTOISO1图形如下: 2、TRANS5图形如下: 3、名为74139A 4.名为SCR3。 23 1

5.名为LF353A ; 3 2 1 8 4 6、名为bridge5,图中元件管脚长度为 20mil ; 01 7、名为bridge4,图中元件管脚 长度为20mil ,每小格长度为10mil ; 8、命名74LS000,图中元件管脚长度为30mil ,每小格长度为10mil ; 附图二:原理图元件74LS000 1 34 2 9.命名74LS138A ,图中元件管脚长度为30mil ,每小格长度为10mil ;

10. 元件 74LS138A 11. 原理图元件PLUS 12、原理图元件XTALB 13、元件命名为SCHOTTKY,图中每小格长度为10mil; 14、元件命名为CAP,图中每小格长度为10mil;

15、元件命名为PNP,图中每小格长度为10mil; 16、原理图元件VS A 17、在schlib1.lib库文件中建立样图所示的带有子件的新元件,元件命名为74ALS000,其中图中对应的为四个子件样图,其中第7、14脚接地和电源,网络名称为GND和VCC。

18、在schlib1.lib 库文件中建立样图3所示的的新元件,元件命名为P89LPC930。 19、schlibl.1ib 库文件中建立样图2所示的带有子件的新元件,元件命名为SN74F27D ,其中第7、14脚接地和电源,网络名称为GND 和VCC 。 20、在schlibl.1ib 库文件中建立样图3所示的新元件,元件命名为PICl6C61-04/P 。 20、在schlibl.1ib 库文件中建立样图2所示的带有子件的新元件,元件命名为CA258,其中第4、8脚接地和电源,网络名称为GND 和VCC 。 231U?A 74ALS000564 U?B 74ALS0008910U?C 74ALS0001112 13U?D 74ALS000

在Protel DXP中建造自己的原理图库

在Protel DXP中建造自己的原理图库 Protel DXP是Altium公司的桌面板级电路设计系统,它集原理图设计输入、PCB设计绘制、模拟电路仿真、数字电路仿真、VHDL混合输入、FPGA设计、信号完整性分析等诸多功能于一体,是非常优秀的EDA软件.Protel DXP提供了丰富的元器件库,这些元器件库主要是集成库和PCB库.Protel DXP没有单独的原理图库,原理图符号存在于集成库中.即使这样,在使用的过程中,有时也经常遇到需要的元器件原理图符号在Protel DXP自带的元器件库中找不到.这时就需要使用者自己绘制原理图符号或者下载所需的库文件.可是如果不进行存档,下次使用时又得重新绘制或者重新下载,麻烦不说,还要浪费很多时间.因此,把自己绘制的和从网上搜集到的原理图符号集中起来,建造一个属于自己的元器件原理图库文件就显得尤为必要.再有,把自己经常需要用到的Protel DXP原理图符号统一放在一个自己建造的Protel DXP原理图库文件中,既便于使用时查找,又便于平时对原理图库文件的管理.下面简单介绍一下如何在ProtelDXP建造一个属于自己的原理图库文件. 1 从现有的库文件中拷贝原理图符号 首先,启动Protel DXP在菜单中点击File→New→Schematic Library,新建一个原理图库文件.接着,保存文件,给它起一个有特色又能反应原理图库特点的名字,如“MySchLib”.然后,再打开一个含有想要添加元器件符号的Protel DXP自带的库文件,假如添加一个电阻元件符号,已知在"Miscellaneous Devices IntLib"集成库文件中含有电阻元件符号,那么就打开该集成库文件.由于是集成库文件,打开该文件时系统会给出“你想要释放这个集成库吗?”的信息.按“Yes”按钮,系统就会把原理图库文件“Miscellaneous Devices.SchLib”,从“Miscellaneous Devices.IntLib”集成库文件中抽取出来,添加到“Projects”面板中.接着,双击“Projects'’面板中“Miscellaneous Devices.SchLib”打开该文件,点击“SCH Library”面板标签,在该面板的“Component”中找到想要添加到自己新建的原理图库文件中去的元件名称.假如以添加电阻元件符号为例,找到“RES2”电阻元件,单击选中它.最后,拷贝该元件到自己新建的原理图库文件中,用Protel DXP的菜单命令:Tools→ Copy Component命令.执行该命令以后系统会出现对话框:在该对话框中单击鼠标,选中要拷贝的目的原理图库文件名,这里是“Myschlib.SchLib”,按“OK”按钮.这样就把电阻元件的原理图符号复制到了我们自己的库文件中. 2 从现有的原理图文件中提取原理图符号 如果你有现成的原理图文件,想把其中你需要的元器件原理图符号添加到自己的库文件中,可又找不到含有该原理图符号的库文件,而且又不想自己重新绘制.这种情况下,可以使用Protel DXP提供的一个由原理图生成原理图库文件的命令.此命令可以把当前打开的原理图文件中用到的所有原理图符号抽取出来,生成一个与当前打开的原理图文件同名的一个原理图库文件.这样一来,只要Protel DXP能打开的原理图文件,你就可以利用这个命令,把现有原理图中所需要的原理图符号抽取出来,用本文第一部分从现有的库中拷贝原理图符号的方法,添加到自己的原理图库文件中去.一般扩展名为“.SCHDOC”、“.SCH”、“.DSN”等的文件,Protel DXP可以直接打开.而且对于扩展名为“.DSN”的文件,用Protel DXP打开后就已经自动生成了原理图库文件,并且直接在Projects浮动面板中列出.由原理图生

实验指导书1——原理图库文件的创建

实验一、原理图库文件的创建 一、实验目的: 1、掌握原理图库文件的建立方法。 2、掌握原理图元件的绘制方法。 二、实验步骤: Ⅰ、新建一个元件库: 1、原理图元件库的建立 新建一个新的原理图库文件并保存该文件:执行菜单file->new->schematic library,系统默认新建一个名为schlib1.schlib的库文件,鼠标右键单击该库文件,在弹出的菜单中选择save 或save as,选择合适的路径,改名(只需输入文件名即可,如abc)并保存该文件。 2、新建一个原理图元件(以一个PDIUSBD12为例) 1)、如果是新建的一个库文件,则系统自动新建一个新元件component_1。否则执行菜单tools->new component,新建一个新元件component_1。在sch library(右下角SCH标签中)中可以看到元件。 2)、改名:在sch library(右下角SCH标签中)中,选中器件,执行菜单tools->rename component, 输入元件名(如本例中为PDIUSBD12)即可。 3)、绘制元件的外形,执行菜单place->rectangle,单击鼠标左键确定外形的左上角,拖动鼠标,在外形的右下角单击鼠标左键。然后单击鼠标右键取消放置外形。 4)、添加引脚,执行菜单place->pin,按TAB键,编辑引脚属性。要编辑引脚名(display name)、引脚号(Designator)、及引脚的电气属性(Electrical Type)。如第1脚,引脚名(display name)为DA TA<0>,引脚号(Designator)为1,引脚的电气属性(Electrical Type)为IO。同样,放置其它引脚。PDIUSBD12 的引脚图见附录。 说明:放置引脚时引脚号在原件外形框外;反斜杠“\”可以给引脚添加取反号。 5)、设置元件属性,在sch library中,选中器件,点edit。“Designator”输入默认的标识,”IC?”;“Comment”输入默认的元件标注,” PDIUSBD12”;在model区域添加PCB封装:单击add,在mode type栏内选footprint,单击ok。点按钮browse,再点右边的…, 选择合适的封装即可。注:元件封装可暂时不加。这里,“Designator”项必不可少。 3、建立一个多功能原理图元件(以反向器74HC14为例)

于博士Cadence视频教程原理图设计pdf

Cadence SPB 15.7 快速入门视频教程 的SPB 16.2版本 第01讲 - 第15讲:OrCAD Capture CIS原理图创建 第16讲 - 第26讲:Cadence Allegro PCB创建封装 第27讲 - 第36讲:Cadence Allegro PCB创建电路板和元器件布局 第37讲 - 第46讲:Cadence Allegro PCB设置布线规则 第47讲 - 第56讲:Cadence Allegro PCB布线 第57讲 - 第60讲:Cadence Allegro PCB后处理、制作光绘文件 第1讲 课程介绍,学习方法,了解CADENCE软件 1.要开发的工程 本教程以下面的例子来开始原理图设计和PCB布线 2.教程内容

3.软件介绍 Design Entry CIS:板级原理图工具 Design Entry HDL:设计芯片的原理图工具,板级设计不用 Layout Plus:OrCAD自带的PCB布线工具,功能不如PCB Editor强大 Layout Plus SmartRoute Calibrate:OrCAD自带的PCB布线工具,功能不如PCB Editor强大PCB Editor:Cadence 的PCB布线工具 PCB Librarian:Cadence 的PCB封装制作工具 PCB Router:Cadence 的自动布线器 PCB SI:Cadence 的PCB信号完整性信号仿真的工具 SigXplorer:Cadence 的PCB信号完整性信号仿真的工具 4.软件列表

5.开始学习Design Entry CIS 启动:Start/Cadence SPB 16.2/Design Entry CIS 启动后,显示下图: 里面有很多选项,应该是对应不同的License 本教程使用:OrCAD Capture CIS 我个人认为:Allegro PCB Design CIS XL是所有可选程序中,功能最强大的,但不知道,强在哪里;而且本教程的原理图文件可以使用上表中不同的程序打开 6.选择OrCAD Capture CIS,启动后显示下图

Cadenceallegro菜单解释

Cadence allegro菜单解释——file 已有 320 次阅读2009-8-16 19:17|个人分类:|关键词:Cadence allegro file 菜单解释 每一款软件几乎都有File菜单,接下来详细解释一下allegro与其他软件不同的菜单。 new 新建PCB文件,点new菜单进入对话框后,drawing type里面包含有9个选项,一般我们如果设计PCB就选择默认第一个board即可。 如果我们要建封装库选package symbol即可,其他7个选项一般很少用,大家可以理解字面意思就可以知道什么意思了。 open 打开你所要设计的 PCB文件,或者封装库文件。 recent designs 打开你所设计的PCB文件,一般是指近期所设计的或者打开过的PCB文件。 save 保存 save as 另存为,重命名。 import import 菜单包含许多项,下面详细解释一下我们经常用到的命令。 logic 导入网表,详细介绍在allegro基础教程连载已经有介绍,在此不再详细介绍。 artwork 导入从其他PCB文件导出的.art的文件。一般很少用词命令。 命令IPF和stream 很少用,略。 DXF 导入结构要素图或者其他DXF的文件。 导入方法如下: 点import/DXF后,在弹出的对话框选择,在DXF file里选择你要导入的DXF的路径,DXF units 选择MM,然后勾选use default text table和incremental addition,其他默认即可。再点edit/view layers弹出对话框,勾选select all,DXF layer filter 选择all,即为导入所有层的信息,然后在下面的class里选择board geometry,subclass选择assembly_notes,因为一般导入结构要素图都是导入这一层,然后点ok,进入了点import/DXF后弹出的对话框,然后点import即可将结构要素图导入。 IDF IFF Router PCAD 这四个命令也很少用,略。 PADS 一般建库的时候导入焊盘。 sub-drawing 命令功能非常强大,也是我们在PCB设计中经常用的命令,如果能够非常合理的应用sub-drawing命令会提高我们设计PCB的效率。

实验报告(原理图库的建立)

物理与电子科学学院PCB 实验 —原理图库的设计 教 案 姓名:刘斌 班级:物电 1105 班 学号: 2011112030560 指导老师:曹老师

实验三原理图库的设计教案 (物理与电子科学学院1105班刘斌2011112030560) 一、实验目的: 1.熟悉原理图工作环境,图形工具中各种命令的使用。 2.熟悉原理图符号的编辑,原理图库的建立。 二、实验内容 在protel DXP中完成,完成下列原理图符号的制作。 1.AT89c51单片机原理图符号制作 2.74LS00芯片的原理图制作

二、AT89c51单片机原理图符号制作实验步骤 第一步:新建工程;“打开软件—文件—新建—PCBproject”,步骤如图 第二步:保存工程;快捷保存方式:可以直接点击菜单栏中的保存按钮即可进行保存操作,或者”File—Save Project”,接着选择保存路径即可,步骤如图: 第三步:新建原理图文件;“在Project命令栏中,PCB Project右击,选择Add New to Project ——Schematic”,步骤如图 第四步:新建原件库文件;“Project—Add New to Project—Schematic Library”,步骤如图

第五步:绘制元器件;可以直接在工具栏选择想要的图形,步骤如图: 第六步:绘制元器件引脚;步骤如图: 第七步:绘制元器件;结构如图: 第八步:在原理图中查看绘制好的元器件图形;形状如图: 第九步:对绘制好的元件原理图,进行适当的调整和修改,使其形状尽量的合理美观。

三、74LS00芯片的原理图制作实验步骤 第一、二、三、四步重复:二、A T89c51单片机原理图符号制作实验步骤 第五步:在这里74LS00芯片原理图通过“分部分”来完成绘制;步骤如图: 第五步:添加五个Part,分别为(PartA、B、C、D、E),然后在Part BCDE绘制如下图形;步骤如图: 第六步:在Part A中绘制如下图形;步骤如图:

如何在原理图中自建原理图库

Altium Designer6.9是Altium公 的桌面板级电路设计系统,它集原理图设计输入、PCB设计 制、模拟电路仿真、数 电路仿真、VHDL混合输入、FPGA设计、信 完整性分析等诸多 能于一体,是非常优秀的EDA软件.Altium Designer6.9提供了丰富的元器件 , 些元器件 要是集 和PCB .Altium Designer6.9没有单独的原理图 ,原理图符 在于集 中.即使 样,在使用的过程中,有时也经常遇到需要的元器件原理图符 在Altium Designer6.9自带的元器件 中找 到. 时就需要使用者自 制原理图符 或者 载所需的 文件.可是如果 进行 档, 次使用时又得 新 制或者 新 载,麻烦 说, 要浪费很多时间.因 ,把自 制的和从网 搜集到的原理图符 集中起来,建造一个属于自 的元器件原理图 文件就显得尤 必要.再有,把自 经常需要用到的Altium Designer6.9原理图符 统一放在一个自 建造的Altium Designer6.9原理图 文件中,既便于使用时查找,又便于平时对原理图 文件的管理. 面简单介绍一 如何在ProtelDXP建造一个属于自 的原理图 文件. 1 从现有的 文件中拷贝原理图符 首先,启动Altium Designer6.9在菜单中点 File→New→Schematic Library,新建一个原理图 文件.接着,保 文件, 它起一个有特色又能 原理图 特点的 ,如听MySchLib吭.然 ,再打开一个 有想要添 元器件符 的Altium Designer6.9自带的 文件,假如添 一个电阻元件符 , 知在"Miscellaneous Devices IntLib"集 文件中 有电阻元件符 ,那 就打开该集 文件.由于是集 文件,打开该文件时系统会 听你想要释放 个集 吗?吭的信息.按听Yes吭按钮,系统就会把原理图 文件听Miscellaneous Devices.SchLib吭,从听Miscellaneous Devices.IntLib吭集 文件中抽取 来,添 到听Projects吭面板中.接着, 听Projects'含面板中听Miscellaneous Devices.SchLib吭打开该文件,点 听SCH Library吭面板标签,在该面板的听Component吭中找到想要添 到自 新建的原理图 文件中去的元件 称.假如 添 电阻元件符 例,找到听RES2吭电阻元件,单 选中它.最 ,拷贝该元件到自 新建的原理图 文件中,用Altium Designer6.9的菜单命 Tools→Copy Component命 .执行该命 系统会 现对话框 在该对话框中单 鼠标,选中要拷贝的目的原理图 文件 , 是听Myschlib.SchLib吭,按听OK吭按钮. 样就把电阻元件的原理图符 复制到了 们自 的 文件中. 2 从现有的原理图文件中提取原理图符 如果你有现 的原理图文件,想把 中你需要的元器件原理图符 添 到自 的 文件中,可又找 到 有该原理图符 的 文件,而且又 想自 新 制. 种情况 ,可 使用Altium Designer6.9提供的一个由原理图生 原理图 文件的命 . 命 可 把当前打开的原理图文件中用到的所有原理图符 抽取 来,生 一个 当前打开的原理图文件 的一个原理图 文件. 样一来,只要Altium Designer6.9能打开的原理图文件,你就可 利用 个命 ,把现有原理图中所需要的原理图符 抽取 来,用本文第一部分从现有的 中拷贝原理图符 的方法,添 到自 的原理图 文件中去.一般扩展 听.SCHDOC吭、听.SCH吭、听.DSN吭等的文件,Altium Designer6.9可 直接打开.而且对于扩展 听.DSN吭的文件,用Altium Designer6.9打开 就 经自动生 了原理图 文件,并且直接在Projects 浮动面板中列 .由原理图生 原理图 文件的 体操作是 首先,打开原理图文件 然 ,使用菜单命 Design→Make Project Library,即可生 一个扩展 听.SCHLIB吭的和打开原理图 的原理图 文件. 3 自 制原理图符 可 直接打开自 的 文件,如 述中的听Myschlib.SchLib吭,然 通过菜单命 Tools →New Component,在 现的对话框中,输入想要建立元件符 的 ,再用图形工 进行

Candence原理图库设计指南

原理图库设计 一,工具及库文件目录结构 目前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发工具供大家建原理图库使用。 Cadence 的元件库必具备如下文件目录结构为: Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table) Sym_1:存放元件符号 Entity:存放元件端口的高层语言描述 Chips:存放元件的物理封装说明和属性 Part-table:存放元件的附加属性,用于构造企业特定部件 我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。 二,原理图库建库参考标准 1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求 该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。 2,Q/ZX 04.125 EDA模块设计规范 此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。 3,Q/ZX 73.1151 EDA库管理办法 此标准规定了公司统一的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件V ALOR的VPL库及相应的元器件资料的管理办法。从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。4,Q/ZX 73.1161 EDA模块库管理办法 此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。 三,原理图库建库step by step 第一步,建库准备 在打开或新建的Project Manager中,如图示,打开Part Developer。

cadence软件介绍

1.Allegro PCB Design CIS Allegro PCB Design CIS Allegro Designer Entry CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,Allegro Designer Entry CIS 提供电路设计从构思到生产所需的一切。 Allegro Designer Entry CIS是全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。 优点 1、提供快捷,直观的,具备完备功能的原理图编辑工具 2、通过层次式和变体(基于同一原理图,不同机型导出)设计提高复杂原理图的设计效率 3、具备强大功能的CIS,帮助加速设计进程,降低项目成本 4、原理图提供的自动缩放/搜索/导航功能,结合Allegro PCB Editor之间的交互探测和交互摆放,和集成的 AMS-Simulatuor帮助提供设计的可生产性 5、减少重复搜寻元件信息的时间,接收来自MRP,ERP和PLM的数据和支持关系型数据库使智能选择元件成为可能 6、通过直接访问ActiveParts和ActiveParts门户网站,提供给选择原理图设计所需要的元件和直接获取器件供应商元件数据更大的便利,ActiveParts提供了超过200万份的元器件数据 7、通过FPGA输出/输入双向数据流程自动整合可编程门阵列(FPGA)和可编程逻辑器件(PLD),从而缩短设计时间 功能特色 全功能原理图编辑器 Allegro Designer Entry CIS,带有拼接式和层次式的原理图页面编辑器,它具有快捷、直观的原理图编辑的特点。原理图页面编辑器整合了标准的Windows用户界面,这些功能和特性是为工程师完成设计任务和发布设计设计数据而特别定制的。 1、在一个会话窗中可以查看和编辑多个项目 2、通过互联网访问最新元器件 3、对“What-if”场景使用状态标签 4、在设计中引入了高效率的电子表格式的属性编辑或者是在原理图编辑器中编辑属性和打印定义好的属性

制作与编辑原理图元件库实验报告

海南师范大学物理与电子工程学院 实验报告 (20 ----20 学年第学期) 课程名称:电子CAD技术 实验名称:制作与编辑原理图元件库专业班级:10级电子二班 学号:201006030240 姓名:叶芬 实验时间:年月日(第周)

实验室名称:学时数: 节 注:报告内容根据具体实验课程或实验项目的要求确定,一般包括实验目的、实验仪器、原理摘要、数据记录及结果分析等。如纸张不够请自行加纸。 实验目的1、熟悉元件库管理; 2、掌握元件编辑器的使用; 3、熟练掌握原理图元件库的创建、新元件的制作 二、实验内容 虽然在Altium Designer Winter09提供了丰富的元器件库,但在设计过程中,仍然会发生在元器件库中找不到需要的元器件。因此,可以利用元器件的绘图工具及IEEE符号工具创建元器件,并添加到元器件库中。 1、利用元件库编辑器提供的制作工具,分别绘制图4-1的元件,并将它保存 在“混杂元器件.SchLib” 元件名:2SC1815 元件名:Res4 元件名:PS2-6PIN LCD-8X2

图4-1混杂元器件 2、利用元件库编辑器提供的制作工具,分别绘制(创建)单片机AT89S51和运放LF347BN芯片,如图4-2和图4-3所示。并将它保存在“常用集成电路.SchLib”元件库中。 图4-2 AT89S51 Part A Part B Part C Part D 图4-3 LF347BN 三、实验步骤 1、在Altium Designer Winter09中,新建工程并保存工程为“常用元器件.PrjPCB”。然后执行【文件】→【库】→【原理图库】命令,创建“混杂元器件.SchLib”原理图元件库,并在该库中制作2SC1815,CAP 2,Res4,PS2-6PIN 和LCD-8X2等元件。

cadence原理图设计规范

原理图设计规范 理念: 设计好一份规范的原理图对设计好PCB/跟机/做客户资料具有指导性意义,是做好一款产品的基础。 一、标准图框图幅 根据实际需要,我公司常用图幅为A2、A3、A4,并有标准格式的图框。其中每一图幅可根据方向分为Landscape(纵向)及Portrait(横向)。在选用图纸时,应能准确清晰的表达区域电路的完整功能。 二、电路布局 原理图的作用是表示电路连接关系,因此需要注意电路结构的易读性。一般可将电路按照功能划分成几个部分,并按照信号流程将各部分合理布局。连线时,需注意避免线条的不必要交叉,以免难于辨识。具体要求如下: 1. 各功能块布局要合理, 整份原理图需布局均衡. 避免有些地方很挤,而有些 地方又很松, PCB 设计同等道理. 2. 尽量将各功能部分模块化(如功放,RADIO, E.VOL, SUB-WOOFER 等),以便于同 类机型资源共享, 各功能模块界线需清晰. 3. 接插口(如电源/喇叭插座, AUX IN, RCA OUTPUT, KB/CD SERVO 接口等)尽 量分布在图纸的四周围, 示意出实际接口外形及每一接脚的功能. 4. 可调元件(如电位器), 切换开关等对应的功能需标识清楚. 5. 滤波器件(如高/低频滤波电容,电感)需置于作用部位的就近处. 6. 重要的控制或信号线需标明流向及用文字标明功能. 7. CPU 为整机的控制中心, 接口线最多. 故CPU周边需留多一些空间进行布线 及相关标注,而不致于显得过分拥挤. 8. CPU 的设置管脚(如AREA1/AREA2, CLOCK1/CLOCK2等)需于旁边做一表格进 行对应设置的说明. 9. 重要器件(如接插座,IC, TUNER 等)外框用粗体线(统一 0.5mm). 10. 元件标号照公司要求按功能块进行标识. 11. 元件参数/数值务求准确标识. 特别留意功率电阻一定需标明功率值, 高耐 压的滤波电容需标明耐压值. 12. 每张原理图都需有公司的标准图框,并标明对应图纸的功能,文件名,制图人 名/审核人名, 日期, 版本号.

- cadence的原理图库设计

- 原理图库编辑器

- Cadence 原理图库设计

- 给你一些常用的原理图库文件

- cadence的原理图库设计..

- Cadence原理图库和PCB库的设计与流程 ppt课件

- Cadence原理图库的制作及使用(二)

- 原理图库元件操作

- AD自建原理图库

- Altium Designer,中自建原理图库

- 第4章 原理图库元件操作

- 原理图库和PCB库设计规范

- 第8章元件基本原理图库、PCB元件封装库和集成元件库

- altium封装库大全原理图库

- 原理图库文件的管理

- AD自建原理图库

- ORCAD_原理图库详细说明

- 创建原理图库和PCB库并关联

- 在Protel DXP中建造自己的原理图库

- 创建原理图库和PCB库并关联